Устройство диагностирования систем управления

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и контрольно-измерительной технике и может быть применено при диагностике систем управления. Введение третьего блока полупостоянной памяти, второго регистра, разрядного коммутатора, генератора логического нуля, генератора логической единицы , регистра .сдвига,- третьего регистра , третьего дешифратора, третьего блока коммутации и ч-етвертого дешифратора позволяет повысить быстродействие устройства, т.е. сократить время поиска неисправности диагностируемого блока, так как не производится накапливания наборов отклонения диагностического теста с последующей от отработкой, а по мере их получения сразу производится обработка дешифрирующих зависимостей . Устройство содержит генератор импульсов, первый, второй и третий счетчики импульсов, первый, второй и третий блоки коммутации, первый, второй и третий регистры, первый, второй и третий дешифраторы, первый, второй и третий блоки полупостоянной памяти, шифратор, аналого-цифровой преобразователь, первый, второй, третий, четвертый, пятый и шестой переключатели, первый и второй блоки сравнения, первый и второй элементы ИЛИ, первьш и второй блоки оперативной памяти, генераторы логического нуля и логической единицы , разрядный коммутатор, регистр сдвига, блок индикации. 1 ил. о б W 1C 4ii tc СО

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК. SU„„3 242918 дц 4 G 05 В 23/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (2i) 3820765/24-24 (22) 04. 12.84 (46) 07.07.86. Бюл. № 25 (72) А.И. Кострыкин, А.Д. Раевский, Ю.М. Бирюков и В.Н. Лифарь (53) 621.396(088.8) (56) Авторское свидетельство СССР № 661552, кл. G 05 В 23/02, 1979.

Авторское свидетельство СССР

¹ 1022118, кл. G 05 В 23/02,. 1983. (54) УСТРОЙСТВО ДИАГНОСТИРОВАНИЯ

СИСТЕМ УПРАВЛЕНИЯ (57) Изобретение относится к автоматике и контрольно-измерительной технике и может быть применено при диагностике систем управления. Введение третьего блока полупостоянной памяти, второго регистра, разрядного коммутатора, генератора "логического нуля", генератора "логической единицы, регистра сдвига, третьего регистра, третьего дешифратора, третьего блока коммутации и четвертого дешифратора позволяет повысить быстродействие устройства, т.е. сократить время поиска неисправности диагностируемого блока, так как не производится накапливания наборов отклонения диагностического теста с последующей от отработкой, а по мере их получения сразу производится обработка дешифрирующих зависимостей. Устройство содержит генератор импульсов, первый, второй и третий счетчики импульсов, первый, второй и третий блоки коммутации, первый, второй и третий регистры, первый, второй и третий дешифраторы, первый, второй и третий блоки полупостоянной памяти, шифратор, аналого-цифровой преобразователь, первый, второй, третий, четвертый, пятый и шестой переключатели, первый и второй блоки сравнения, первый и второй элементы ИЛИ, первый и второй .блоки оперативной памяти, генераторы "логического нуля" и "логич ской единицы", разрядный коммутатор, регистр сдвига, блок индикации. 1 ил.

1242918

25 .З0

:1. >i

Изобретение относится к автоматике и контрольно-измерительной технике и может быть применено при диагностике систем управления.

Цель изобретения — повышение быстродействия устройства.

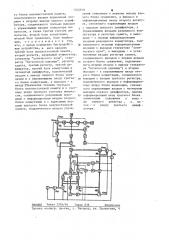

На чертеже представлена функциональная схема устройства.

Устройство имеет генератор I импульсов, первый счетчик 2 импульсоз„

I второй счетчик 3 импульсов, первый блок 4 коммутации, первый регистр 5, первый дешифратор 6, второй блок 7 полупостоянной памяти, шифратор 8, блок 9 диагностирования, аналого-цифровой преобразователь 10, первый переключатель 11, третий переключа— тель 12, первый элемент ИЛИ 13, второй переключатель 14, второй элемент

ИЛИ 15, первый и второй блоки 16 и 17 оперативной памяти, четвертый и пятый переключатели 18 и 19, второй дешифратор 20, шестой переключатель 21, первый блок 22 сравнения, первый блок 23 полупостоянной памяти, блок 24 индикации, третий блок 25 полупостоянной памяти, второй регистр 26, третий счетчик 27 импульсов, четвертый дешифратор 28, генератор 29 "логического нуля", разрядный коммутатор 30, третий блок 31 коммутации, третий дешифратор 32, регистр 33 сдвига, второй блок 34 сравнения, генератор 35 "логической единицы", второй блок 36 коммутации, третий регистр 37.

Устройство работает следующим образом.

Первый такт генератора 1 импульсов подсчитывается первым 2 и вторым 3 счетчиками импульсов,, причем счетчик 2 срабатывает по переднему фронту такта, а счетчик 3 — по заднему фронту. По переднему фронту первого такта открывается блок 4 коммутации и начальное (нулевое) значение счетчика 3 импульсов заносится в регистр 5.

Производятся следующие переключения: выход аналого-цифрового преобразователя 10 подключается к первому входу блока 16 оперативной памяти, выход блока 17 оперативной памяти подключается к второму входу блока

22 сравнения, выход блока 4 коммутаций подключается к адресному входу блока 17 оперативной памяти, выход

I счетчика 2 импульсов подключается к адресному входу блока 16 оперативной памяти, первый выход дешифратора 20 подключается к входу счйтывания блока 17 оперативной памяти, RTopoH выход второго дешифратора

20 подключается к входу записи блока 16 оперативной памяти:

По первому такту генератора импульсов дешифратор 6 выдает команду на считывание первого набора полного диагностического теста из блока 7 полупостоянной памяти, который преобразуется шифратором 8 в последовательность управляющих воздействий и подается на входы диагностируемого блока 9.

Выходная последовательность сигналов диагностируемого блока 9 преобразуется аналого-цифровым преобразователем 10 к единому цифровому виду и запоминается в блоке 16 оперативной памяти. По команде, формируемой счетчиком 2 и дешифратором 6, производится считывание нулевых записей из блока 17 оперативной памяти и из блока 23 полупостоянной памяти и осуществляется их сравнение блоком 22 сравнения.

Второй такт генератора 1 импульсов подсчитывается счетчиками 2 и 3 импульсов.По переднему фронту второго такта о.крывается блок 4 коммутации и значение счетчика 3 импульсов "единица" заносится в регистр 5.

Производятся следующие переключения: выход аналого — цифрового преобразователя 10 подключается к информационному входу. блока 17 оперативной памяти, выход блока 16 оперативной памяти подключается к первому входу блока 23 сравнения, выход блока 4 коммутации подключается к адресному входу блока 16 оперативной памяти, выход счетчика 2 импульсов подключается к адресному вхоцу блока 17 оперативной памяти, первый выход дешифратора 20 подключается к входу считывания блока 16 оператив— ной памяти, вгорой выход дешифрато 1 Л ра 20 подключается к входу записи второго блока 17 оперативной памяти.

Ilo второму такту генератора 1 импульсов дешифратор 6 выдает команду на считывание из блока 7 полупостоянной памяти второго набора полного структурного диагностического теста который преобразуется шифратором 8 в последовательность управляющих

1242918. воздействий и подается на входы диагностируемого блока 9. Выходная последовательность сигналов диагностируемого блока 9 преобразуется аналого-цифровым преобразователем 10 к единому цифровому виду и запоми, наетдя в блоке 17 оперативной памяти.

По команде дешифратора 6 производится считывание записей выходных последовательностей сигналов диагности- 0 руемого блока 9, соответствующих подаче на входы последнего первого набора структурного диагностического теста, из блока 16 оперативной памяти и блока 23 полупостоянной па- f5 мяти и осуществляется их сравнение блоком 22 сравнения.

В случае несовпадения этих последовательностей по команде блока 22 сравнения запускается дешифратором

28, а также открывается блок 31 коммутации и запускается дешифратор 32 °

Дешифратор 28 при очередном запуске выдает в блок 25 "полупостоянной памяти команды на считывание на- 25 боров дешнфрирующих зависимостей, а адресную часть считывания наборов дешифрирующих зависимостей формирует счетчик 27, при этом содержимое по данному адресу считывается в регистр ЗО

26. По команде дешифратора 32 раз- . рядным коммутатором 30 вьщеляется искомый разряд считанной записи в регистр 33 сдвига, остальные разряды данной записи обнуляются генерато35 ром "логического нуля" 29. В регист— ре 33 сдвига производится сдвиг вьщеленного разряда вправо под управлением дешифратора 32. Блоком 34 сравнения содержимое выделенного разряда сравнивается с логической единицей", формируемой генератором

35 "логической единицы". При сравнении в регистр 37 через блок 36 ком.мутации записывается адрес набора, сформированный счетчиком 27. При несравнении блоком 34 сравнения выдается команда на стирание записи с данным адресом из блока 25 полупостоянной памяти.

Формула изобретения

После поступления на вход дешифратора 6 такта, номер которого, подсчитанный счетчиком 2, равен (N+1), где N - количество наборов теста, первый дешифратор 6 выполняет следующие операции: выдает команду на вход управления генератора 1 импульсов на его выключение, выдает команду на включение блока 24 индикации, который показывает содержимое регистра 37 с адресом отказавшего элемента диагностируемого блока 9.

Устройство диагностирования систем управления, содержащее генератор импульсов, подключенный выходом к управляющим входам первого, второго, третьего, четвертого и пятого переключателей, к счетному входу первого счетчика импульсов, к управляющему входу первого блока коммутации и к счетному входу второго счетчика импульсов, соединенного разрядными выходами с информационным входом первого блока коммутации, подключенного выходом к входу первого регистра и к информационному входу третьего переключателя, связанного выходом с первыми входами первого и второго элементов И, подключенных вторыми входами к выходу второго переключателя, а выходами — к адресным входам соответственно первого и второго блоков оперативной памяти, соединенных информационными входами с выхо- дом первого переключателя, а выходами — с информационными входами шестого переключателя, подключенного управляющим входом к выходу первого генератора импульсов, а выходом — к первому входу первого блока сравнения, связанного вторым входом с выходом первого блока полупостоянной памяти, подключенного входом управления чтением к первому выходу первого дешифратора, а адресными входами — к входам первого.дешифратора и к разрядным выходам первого счетчика импульсов, к адресным входам второго блока полупостоянной памяти, к информационному входу второго переключателя и к входам второго дешифратора, соединенного первым и вторым выходами с информационными входами соответственно четвертого и пятого переключателей, соединенных выходами соответственно с входами управления чтением и записью второго и первого блоков оперативной памяти, аналого-цифровой преобразователь, подключенный входом к входу устройства, а выходом — к информационному входу первого переключателя, шифратор, связанный выходом с выходом устройства, а входом — с выходом второ12429 цПИИПИ Заказ 37С4/46 Тираж 836

Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

5 го блока полупостоянной памяти, подключенного входом управления чтением к второму выходу первого дешифратора, соединенного третьим выходом управляющим входом генератора Hìпульсов, а также третий счетчик импульсов, второй блок коммутации, второй блок сравнения, блок индикации, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства„ в него введены третий блок полупостоянной памяти, второй регистр, разрядный коммутатор, генератор "логического нуля, генератор "логической единицы", регистр сдвига, третий регистр, третии дешифратор, третий блок коммутации и четвертый дешифратор, подключенный входом к выходу первого блока сравнения и к управляющему входу третьего блока коммутации, а выходом — к входу управления чтением третьего блока полупостоянной памяти и к счетному входу третьего счетчика импульсов, соединенного разрядными выходами с информационным входом второго блока коммутации и с адресными входами третьего блока полупостояннои памяти, подключенного входом управl8 Ь чения стиранием к первому выходу вто-. рого блока сравнения, а выходом к информационному входу второго регистРа, связанного управляющим входом с выхоцом третьего дешифратора, с управляющими входами разрядного коммутатора и регистра сдвига, а выходами — с первым информационными входами разрядного коммутатора, подключенного вторыми информационными и входами к выходам генератора логического нуля.", а выходами — к установочным входам регистра сдвига, соединенного выходом с первым входом второго блока сравнения; подключенного. вторым входом к выходу генератора "логической единицы а вторым выходом — к управляющему входу второго блока коммутации, соединенного выходом с входом третьего регистра, подключенного выходом к информационному входу блока индикации, связанного управляющим входом с четвертым выходом r::epâoão дешифратора, причем информационный вход третьего блока коммутации псдключен к выхо ду первого регистра, а, выход — к входу третьего дешифратора.