Устройство для контроля адресных шин интерфейса

Иллюстрации

Показать всеРеферат

Изобретение относится к автома- . тике и вычислительной технике и,.может быть использовано для контроля некоторых функций интерфейса. В устройстве происходит контроль адресных шин интерфейса. С целью повышения достоверности контроля устрбйство содержит п блоков анализа, где п - разрядность адресной шины интерфейса . В каждом блоке анализа содержится дешифратор, шифратор, схема свертки по модулю три, которые обеспечивают получение остатка по модулю три от входного адреса. В случае совпадения этого модуля с контрольным йодуЛем происходит включение абонента , соответствующего этому адресу, в случае несовпадения происходит отключение блока анализа от шин интерфейса . 3 ил. W

СОЮЗ СОВЕТСНИХ

РЕСПУБЛИН

„„SU„„1242963 А1 дц 4 0 06 F 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

KFrrle-.."iq

)3, „ „)В

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ВЯЬЛНОТИИ (:

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3724430/24 24 (22) 11.04.84 (46) 07.07.86. Бюл. 9 25 (72} А. Н. Гришуткин, А. P. Каплан и Н. Н. Новиков . (53) 681.3(088.8) (56) Авторское свидетельство СССР

В 601895, кл. G 06 F 11/00.

Селлерс П. Ф. Методы обнаружения, ошибок в работе ЭЦВМ. М.: Мир, 1972, с. 232, фиг. 12.8. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АДРЕС»

НЫХ ШИН ИНТЕРФЕЙСА (57) Изобретение относится к автома тике и вычислительной технике и,мо» . жет быть использовано для контроля некоторых функции интерфеиса. В уст ройстве происходит контроль адресных шин интерфейса. С целью повышения достоверности контроля устрбйство содержит п блоков анализа, где п —разрядность адресной шины интерфейса. В каждом блоке анализа содержится дешифратор, шифратор, схема свертки по модулю три, которые обеспечивают получение остатка по модулю три от входного адреса. В случае совпадения этого модуля с контрольным модулем происходит включение абонента, соответствующего этому адресу, в случае несовпадения происходит отключение блока анализа от шин интерфейса. 3 ил.

124?963

20

30 анализа.

Изобретение относится к вычислительной технике и может быть использовано для контроля функционирования интерфейсов процессоров, микропрограммных автоматов или других систем.

Цель изобретения - повышение достоверности контроля.

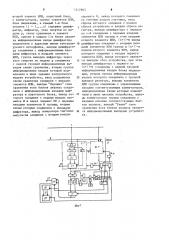

На фиг. 1 представлена блок-схема предлагаемого устройства, на фиг. 2 - схема шифратора; на фиг. 3схема порогового блока.

Устройство содержит контролируемый интерфейс 1, и блоков 2,1-2.п анализа, информационные выходы 3.1З.п, дешифраторы 4.1-4,п, шифраторы

5.1-5.п, узлы 6.1-6.п свертки по модулю Р, схемы 7.1.-7,п сравнения, элементы ИЛИ 8.1-8,п, шину- 9 задания контрольного модуля, шифратор 10, регистр 11, блок 12 индикации, вход

13 сброса, элемент ИЛИ 14, группу элементов И 15, элемент НЕ 16, поро говый блок 17, элемент И 18, генера- тор 19 тактовых импульсов, счетчик

20, дешифратор 21, элемент ИЛИ 22, группу элементов ИЛИ 23, группу коммутаторов 24.1-24.п, выход 25 сбоя, дешифратор 26 и элементы 27 индикации.

Шифратор (фиг. 2) содерлжт сум маторы 28 по модулю два.

Пороговый блок (фиг. 3) содержитэлементы И 29 и элемент ИЛИ 30.

Шифратор 10 (фиг. 2) осуществляет суммирование в подмножестве Хэмминга в соответствии со следующими формула" ми .

Я = b +а +а +а +а +а +а +8, +...;

0 1 4 4 3 7 0 1

5. = b +а +а +а +а +a +а +а +...;

2 1 З 4 Ь 6 s0 1 1

S = Ь +"., +а. + . +а +а +а +а +..., 3 p z y g & э 10 м * где Ь, b „ Ь в данном случае равно нулю. а„ ...а, - информационные разряды, их значения определяются сигналами, снимаемыми с выходов

"Неравно" схем 7.1.7.п сравнения;

+ - математический знак суммирования по моду лю два.

На основании этих формул построен шифратор 10 для трех контрольных схем

55 сумм $ 3 и Б в подмножествах Хэм а минга.

Пороговый блок 17 осуществляет контроль наличия сигнала на выходе схем 7,1-7.п сравнения блоков 2.12,п анализа. Если выдается сигнал только с одной схемы 7 сравнения, ro на выходе порогового блока 17 сигнал отсутствует, Сигнал отсутствует и тогда, когда ни с одной схемы 7 сравнения сигнал не поступает. В случае, если на шифратор 10 посту лают более одного сигнала (т.е. два, три и т„д.), то с выхода порогового блока 17 выдается сигнал, эквивалентный логической единице, который с помощью- элемента НЕ 16 запрещает прохождение информации через элемент

И 15.

Количество блоков анализа опреде ляется числом адресных шин интерфейса (т,е, числом абонентов). В качестве абонентов могут служить такие устройства, как оперативно запоминающее устройство и т.п.

Коммутатор 24 работает следующим образом, При появлении сигнала, эквивалентного логической единице, на выходе элементов ИЛИ 23, закрывается коммутатор 24, тем самым снимается питание со всех элементов блоков 2,1-2.п

По шине адреса поступает информация об адресе выбираемого абонента.

Абонент подключается к выходам 3.13,7l устройств 1.

На шину 9 задания контрольного модуля поступает эталонный остаток но модулю р, который определяется в зависимости от номера адреса (веса кода слова адреса).

Устройство работает следующим об» разом, С интерфейса 1 код адреса появляется в момент времени и поступает на дешифратор 4. С его выхода информация поступает на шифратор 5„ а с него на узел 6 свертки по модулю р.

Последний производит сворачивание поступившей информации по модулю р и определяет остаток. С выхода этого узла остаток поступает на первую группу входов схемы 7 сравнения. На вторую группу входов этой схемы поступает эталонный остаток с шины 9 задания контрольного модуля. Синхронизация режима сравнения осуществля1242963

40

55 ется по сигналу, поступающему с вьгхода элемента ИЛИ Я. Если информация, поступающая на первую и вторую груп пу входов схемы 7 сравнения, совпа дает, то с выхода"Равно". схемы выда» ется сигнал, эквивалентный логичес кой единице, который служит для под ключения абонента по соответствующему адресу.

Если информация, поступающая на первую и вторую группы входов схемы

7 сравнения, не совпадает только в одном из блоков 2 анализа, то с выхода "Неравно" схемы 7 сравненИя снимается выходной сигнал, который поступает на шифратор 10 где в со ответствии с описанным законом происходят сворачивание информации и запись ее через элементы И 15 в регистр 11.

Информация с выхода регистра 11 поступает через элемент ИЛИ 14 на выход сбоя устройства и на блок индикации, в котором благодаря дешифратору 26 определяется место неисправности., Если возникает помеха .(т.е. сигналы типа константы единицы) на адресных шинах интерфейса 1, приводящая. к выбору двух или более абонентов, или при возникновении неисправностей в двух или более дешифраторах 4 выдаются сигналы с двух или более схем

7 сравнения, В этом случае срабатывает пороговый блок 17, который вы дает сигнал на элемент НЕ 16, запрещая прохождение информации через эле менты И 15, а также на вход элемента

И 18, подготавливая его к открытию.

На другой вход элемента Ц 18 посту лают импульсы с генератора 19 тактовых импульсов. В счетчик 20 записы вается импульс. Со счетчика 20 поступает кодовая комбинация на информационные входы дешифратора 21. Например, у дешифратора 21 возбуждается одна из выходных шин, что обеспечивает выдачу сигнала через элементы ИЛИ 22 и 14 на выход сбоя устройства. Одновременно с первого выхода дешифрато- . ра 21 сигнал поступает на коммутатор

24.1, который снимает питание с первого блока 2.1 анализа.

По командам с дешифратора 21 может отключаться как один, так и несколько блоков анализа, т.е. не происходит включение абонентов по невер15

35 ному адресу с выходов 3.1 Л.г. устройства.

Емкость счетчика 20 и дешифратора

21 выбирается, исходя из количества абонентов (адресов).

Информация с дешифратора 2!, т.е. информация о тех блоках анализа, с которых снято питание, подается на блок 12 индикации.. В случае, если при отключении какого-либо блока 2 анализа на примере блока 2,1 и при появлении следующего адреса, снимаемого с шин адреса интерфейса 1, на вход шифратора

10,поступает сигнал только с одной схемы 7 сравнения, то с порогового блока 17 выдается сигнал, эквивалент ный логическому нулю. Это дает воз» можность информации проходить с шифратора 10 через элементы И 15 на вход регистра 11. С выхода регистра 11 информация поступает на дешифратор

26, который, выдает на блок 12 индикации информацию о неисправном блоке 2 анализа.

Таким образом, на блок 12 индикации поступает информация с дешифратора 21 об отключенном блоке анализа (абоненте) или группе абонентов и с регистра

11 неисправного блока анализа, что позволяет выявить ошибочный адрес интерфейса, по которому шла адресация к абоненту.

Приведение в исходное (нулевое) со стояние регистра 11 и счетчика 20 производится по команде сброс, поступающей по входу 13 устройства.

Ф о р м ул а и з о б р е т е н и я

Устройство для контроля адресных шин интерфейса, содержащее генератор тактовых импульсов, группу элементов

И. первый элемент .ИЛИ, дешифратор, регистр, элемент HE элемент И, счетчик, причем выходы счетчика соединены с информационными входами дешифратора, информационные входы регистра соединены с информационными входами дешифратора, информационные входы регистра соединены с выходами элементов

И группы, группа выходов регистра со-. единена с группой входов первого элемента ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно содержит п блоков анализа (где n » число контролируемых адресных шин интерфейса), шифратор, l2l:2963 второй элемент ИЛИ, пороговый блок, п коммутаторов, группу элементов ИЛИ, блок индикации, а каждый i-й блок анализа (i = 1...,п) содержит дешиф.ратор, шифратор, узел свертки по модулю р, схему сравнения и элемент

ИЛИ, причем в каждом i-м блоке анализа информационные входы дешифратора подключены к адресным шинам контроли- 10 руемого интерфейса, выходы дешифрато- . ра соединены с информационными входами шифратора и.входами элемента

ИЛИ, группа выходов шифратора через узел свертки по модулю р соединена 15 с первой группой информационных выходов схемы сравнения, вторая группа информационных входов которой подключена к шине задания контрольного модуля устройства, вход разрешения 20 схемы сравнения соединен с выходом элемента ИЛИ, выходы "Неравно" схем сравнения всех блоков анализа соединены с информационными входами шифратора и порогового блока, выход ко- 25 торого соединен с первым входом элемента И и через элемент НЕ с первыми входами элементов И группы, вторые входы которых соединены с выходами шифратора, выход генератора тактовых 30 импульсов соединен с вторым входом элемента И, выхоц которого соединен ,со счетным входом счетчика, вход сброса которого соединен с входом сброса устройства и входом сброса регистра, выходы дешифратора с первого по и-й соединены с первыми входами элементов ИЛИ группы и и-ми входами второго элемента ИЛИ, (п+1)-й выход дешифратора соединен с вторыми входами элементов ИЛИ группы и (п- 1)-м. входом второго элемента ИЛИ, выход которого соединен с входом первого элемента ИЛИ, выход которого является выходом сбоя устройства, при этом выходы дешифратора с первого по (и+1)-й соединены с первой группой информационных входов блока индикации, вторая группа информационных входов которого соединена с группой выходов регистра., выходы элементов

ИЛИ группы соединены с управляющими входами соответствующих коммутаторов, информационные входы которых подключены к шине питания устройства, выхо ды коммутаторов группы соединены с входами питания соответствующих блоков анализа, выход@ "Равно" схем сравнения всех блоков анализа являют сН информационными выходами устройствае!

242963

Составитель А. Сиротская

Редактор О. 10рковецкая . Техред О. ортвай Корректор А. Тяско

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35,. Раушская наб., д..4/5

Заказ 3706/48

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4