Устройство для мажоритарного декодирования в целом

Иллюстрации

Показать всеРеферат

Изобретение может найти применение в системах передачи информации с трехкратным дублированием сообщений. Применение этого устройства позволяет повысить быстродействие. Устройство содержит аналоговый демодулятор 1, квантизатор2, регистры 3, ; 4 памяти, элементы И 5, 6, элементы 1ШИ 7, 8, блоки 9, 10 ключей 11, сумматоры 12 - 14, вычитатели 15 - 18, пороговые элементы 19, 20, элемент НЕ 21, счетчик 22, логический блок 23,- блок 24 усилителей 25, делитель 26, источник 27 опорных напряжений-, коммутаторы 28 - 31, перемножители 32, 33, триггер 34, выходной регистр 35 и блок 36 управления. Запись каждого повторения квантованного и дискретизированного входного сигнала (О (Л СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (В 4 Н 03 М 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ВЫЮ,"Г.1(А

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3829538/24-24 (22) 20.12.84 (46) 07.07.86. Бюл. № 25 (72) Ю.П. Зубков, Л.Ф. Бородин, Е.П. Трубников, В.И. Ключко, А.N. Александров, Ю.И. Николаев и В.Е. Петухов (53) 621.394.142(088.8) (56) Авторское свидетельство СССР № 1045383, кл. Н 03 К 13/32, 10.06.82.

Авторское свидетельство СССР № 1109902, кл. Н 03 К 13/32, 08.04.83.

I (54) УСТРОИСТВО ДЛЯ МАЖОРИТАРНОГО

ДЕКОДИРОВАНИЯ В ЦЕЛОМ (57) Изобретение может найти применение в системах передачи. информации

ÄÄSUÄÄ 1243101 А1 I с трехкратным дублированием сообще ний. Применение этого устройства позволяет повысить быстродействие. Устройство содержит аналоговый демодулятор 1, квантизатор.2, регистры 3, 4 памяти, элементы И 5, б, элементы

ИЛИ 7, 8, блоки 9, 10 ключей 11, сумматоры 12 — 14, вычитатели 15 — 18, пороговые элементы 19, 20, элемент

НЕ 2 1, счетчик 22, логический блок

23; блок 24 усилителей 25, делитель

26, источник 27 опорных напряжений, коммутаторы 28 — 31, перемножители

32, 33, триггер 34, выходной регистр

35 и блок 36 управления. Запись каждого повторения квантованного и дискретизированного входного сигнала

12431 производится в регистры 3, 4 памяти, уричем каждое следующее повторение выталкивает предыдущее из регистра

3 в регистр 4. С помощью сумматоров

12 — 14, вычитателей 15 — 16 и пороговых элементов 19, 20 производится декодирование сообщения с учетом предыдущих повторений и передача его на выход устройства с помощью ком01 мутаторов 30, 31 и выходного регистра

35. Введение блока 36 управления, логилескбго блока 23, блока 24 усилителей 25, делителя 26, перемножителя

32 и коммутатора 29 позволяет сократить:время анализа, если решение о правильном приеме может быть пРинято по первьпч.двум из трех повторений., 2 з.п. ф-лы, 3 ил.

Изобретение относится к вычислительной технике и технике связи и может использоваться н системах передачи информации с трехкратным дублированием сообщений.

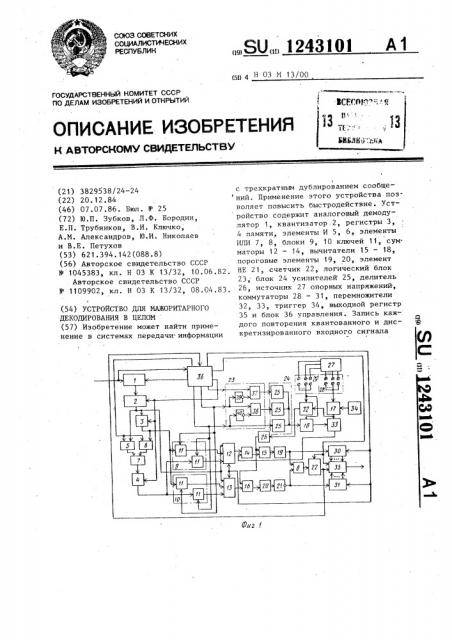

Цель изобретения — повышение быстродействия. На фиг,. 1 приведена функциональная схема устройства; на фиг. 2 — схема блока управления; на фиг. 3 — схема квантизатора.

Устройство для мажоритарного декодирования в целом содержит аналоговый демодулятор 1, квантизатор 2, первый и второй регистры 3 и 4 памяти, первый и второй элементы 5 и 6 И, первый 7 и второй 8 элементы ИЛИ, первый и второй блоки 9 и 10 ключей

11, первый, второй, третий сумматоры

12-14, первый, второй, третий, четвертый вычитатели 15-18, первый и второй пороговые элементы 19 и 20, элемент НЕ 21, счетчик 22, логический блок 23, блок 24 усилителей 25, дели тель 26, источник 27 опорных напряжений, первый, второй, третин и четвертый коммутаторы 28-31, первый и второй перемножители 32 "и 33, триггер

34, выходной регистр 35 и блок 36 управления.

Логический блок 23 состоит из пер» ного 37 и второго 38 элементов И и первого 39 и второго 40 элементов НЕ.

Блок управления включает хронизатор

4i первый, второй, третий счетчики

42-44, триггеры 45-49 с первого по пятый, первый и второй ключи 50 и 51, первый 52 и второй 53 элементы HJIH и элементы 54-58 задержки с первого по пятый.

Квантизатор 2 может состоять из преобразователя 59 на (М-1) триггерах 60, формирователя 61 пороговых уровней, дешифратора 62 на (М-2) элементах 63 И и многоустойчивого элемента 64. Квантизатор 2 предназначей для преобразования входного аналого2

aoro сигнала, дискретизированного н аналсгоном демодуляторе, н выходной

М-ичный дискретный си1 нал .

Первый элемент 5И открыт только на время обработки сигналов второго повторения, а второй элемент 6И от- . крыт только на время прохождения первсго и третьего повторов информационных символов. !

Ц

Источник 27 опорных напряжений выдает на первые выходы напряжения, соответствующие определенным значениям количеств М зон квантования, а на вторые выходы — напряжения, соответствующие определенным значениям количест:в Н повторов.

Физическая сущность алгоритма функционирования заключается в том, что при вынесении решения по соответствующему информационному символу учитывают не только все повторения этого символа, но и имеющееся число

:повторений. С учетом этого замечания

1 алгоритм функционирования устройства имеет вид

19 если, Х 7>

Н(М вЂ” 1)

Я |

0 если, Х +(Н-з) (М-1) 4

Н (М-1)

1 где j и информационный сигнал

1 (символ);

Х вЂ” i-e повторение j-го информационного сигнала н виде соответствующего сигнала на выходе квантизатора 2;

Н вЂ” количество повторений информационного сигнала;

М -- количество зон квантования н кнантизаторе 2.

1243101

Из анализа выражения (1) следует, что решение может быть вынесено не только по 1 повторениям (i=1,Н), но и по меньшему их количеству, что сокращает время на принятие решения.

Коммутаторы 28 и 29 выполнены в виде наборных полей. Выходные напряжения определяются положением соответствующих перемычек.

Счетчик 22 выполнен таким образом, что сигнал переполнения на его выходе появляется при поступлении на

его вход К -го сигнала (здесь количество информационных сигналов в кодограмме)По управляющемусигналу от блока 36управления счетчикустанавли— вается висходное (нулевое)состояние.

Коммутаторы 30 и 3". управляются .сигналами с выхода блока 36 управления. Выходы коммутатора 31 соединены с единичными входами ячеек памяти регистра 35, выходы коммутатора 30 соединены с нулевыми входами соответствующих ячеек памяти регистра 35.

Блок 36 управления (фиг. 2) рабо-. тает следующим образом. С помощью хронизатора 41 формируется Н1, (для кодов с трехкратным повторением — 3K) тактовых импульсов, которые подаются на аналоговый демодулятор 1 и через первый элемент 54 задержки на коммутаторы 30 и 31. Первый тактовый импульс устанавливает первый триггер

45 в единичное состояние, которое в виде соответствующего сигнала подается на первый вход логического блока

23. Тактовые импульсы поступают также на вход первого счетчика 42, импульс переполнения на выходе которого формируется при поступлении на его вход

К-ro импульса. Этот импульс переполнения устанавливает второй триггер 46 в едини ное состояние. При этом открывается первый ключ 50, на втором выходе блока 36 управления формируется управляющий сигнал для блоков 9 и

10 ключей 11 и логического блока 23,. и третий триггер 47 устанавливается в единичное пол.-„кение, открывая тем самым первый элемент И5 и закрывая второй элемент И6. Через открытый первый ключ 50 проходит на вход второго счетчика 43 вторая группа из K тактовых импульсов. При этом последний, то есть 2К-й тактовый импульс возвращает третий триггер 47 в исходное нулевое состояние и тем са мым открывает элемент И6, закрывая элемент И5. Этот же импульс с выхода40

5О

s(t)=Is„(t), s„(t),..., s„,(t), I где K — количество информационных сигналов в кодограмме с Н-3кратным повторением.

В блоке 36 управления формируется последовательность тактовых импульсов, которые подают на второй вход аналогового демодулятора 1. На первый вход демодулятора поступают элементарные канальные сигналы S (С). В демодуляЧ торе они преобразуются в аналоговые элементарные сигналы (существо этой операции определяется способом. приема элементарных сигналов, их типом, характеристиками канала связи, отношением сигнал — шум и т.д.), которые определяют составной аналоговый счгнал с избыточностью счетчика 43 подается на четвертый триггер 48 и устанавливает его в еди-, ничное состояние, Выходной едийичйый сигнал -четвертого триггера 48 уста5 навливает первый триггер 49 в единичное состояние. Выходной сигнал пятого триггера 49 подается на соответствующие входы блоков 9 и 10 ключей

11 и логического блока 23. Выходной

1б сигнал четвертого триггера 48, кроме того, открывает второй ключ 51. Через открытый ключ 51 тактовые импульсы подаются на вход третьего счетчика

44 и через элемент ИЛИ 52 — на входы

15 обнуления счетчика 22 и регистра 35 для их сброса (для этой же цели подается на другой вход элемента ИЛИ 63 выходной сигнал первого ключа 50).

Импульс переполнения третьего счет20 чика 44 через четвертый элемент 57 задержки поступает на один из вхо- . дов второго элемента ИЛИ 53, на выходе которого формируется сигнал "Обну-. ление". Выходной сигнал счетчика 44, пройдя третий элемент 56, возвращает пятый триггер 49 в исходное состояние. На второй вход блока 36 управления подается и выходной сигнал

c÷eò÷èêà 22. Этот сигнал после задержки в пятом элементе 58 появляется

,на выходе второго элемента ИЛИ 53 в виде сигнала "Обнуление".

Устройство для мажоритарного деко4 дирования в .целом работает следующим,. образом.

На вход устройства поступает последовательный составной сигнал с из-, быточностью

124310 I

Х Х Х \ 9 7/9 "ЯУ " * Р К )

Аналоговый сигнал Х последова- 5 тельно поступает на вход квантизатора 2, а точнее — на входы триггеров 60 преобразователя 59. На другой вход каждого триггера 60 с соответствующего выхода формирователя 61 лоро- 10 гового напряжения подаются напряжения, определяющие порог срабатывания данного триггера 60. Если входной аналоговый сигнал квантизатора 2 меньше (или равен) величины первого уровня, то все триггеры 60 находятся в исходном (нулевом) состоянии. При этом на всех входах многоустойчивого элемента 64 управляющие сигналы отсутствуют, вследствие чего на выходе 20 формируется сигнал "О . Если же вхсдной аналоговый "èãíàë больше первого, но меньше (или ранен) второго порогового уровня напряжения, то срабатывает первыи триггер, на первом входе элемента 64 "формируется управляющий сигнал, вследствие чего на выходе многоустойчивогс элемента 64 формируется сигнал "1". Если величина сигнала на выходе аналогового демодулятора Зо

1 такова, что срабатывает первый и второй триггеры 60, тс управляющие сигналы появляются на первых двух входах элемента 64„ а его выходной сигнал имеет значение 2 и т„д. Если же величина аналогового сигнала боль. ше величины последнего порогового уровня напряжения, то срабатывают все триггеры 60 преобразователя 59.

Управляющие сигналы будут присутствовать на всех входах элемента 64.

При этом на выходе элемента 64 появляется сигнал "М-1". Таким образом, с помощью квантизатсра 2 аналоговые сигналы преобразуют в дискретные Мичные сигналы. На выходе квантизатсра 2 формируется последовательный дискретный избыточный сигнал

В = (Ь„, Ь„,, Ь,, Ь„„ Ь,„ Ь.1 z

Ь„, Ь„,..., Ь„,), где ь, а(о,,7° .° .°.,, N-11 который представляет собой трехкратно повторенные информационные М-ичные символы (сигналы). Сигнал В последо- - » вательнс поступает на вход первого регистра 3 памяти и одновременно через элемент ИЛИ 7 — на вход второго регистра 4 памяти. Кроме того, этот сигнал подается на первые входы сумматоров 12 и 13. На другие входы этих сумматоров поступают нулевые сигналы (т.е. на эти входы сигналы не подаются). Следовательно, на первые входы сумматоров 12 и 13 последовательно поступают сигналы Ь,„, Ь „,..., Ь„, .

На выходе этих сумматоров формируется сигнал, соответствующий сумме входных сигналов, т.е. первым выходным сигналом каждого из рассматриваемых сумматорсв будет сигнал, равный сумме

Ь, с двумя нулевыми сигналами. Далее и на сумматоры подаются тактовые импульсы, которые сбрасывают этот выходной сигнал. После этого на выходе сумматоров I2 и 13 формируется сигнал, равный сумме Ь с нулевыми

Яf сигналами у и т од е

Наконец появляется на выходе каждого из сумматоров 12 и 13 сигнал, равный сумме Ь, с нулевыми сигналами, Выходной сигнал первого сумматора

12 подается на вход третьего сумматора 14, на другой вход которого поступает с выхода второго перемножителя 33 сигнал (Н-i) ° (М-1). Этот сигнал формируется следующим образом. Сигналы с соответствующих выходов источника 27 опорных напряжений через коммутатсрь; 28 и 29 подаются соответственно на входы третьего вычитателя

17 и четвертого вычитателя 18. Этот входной сигнал вычитателя 17 определяет значение М . Ha другой его вход с

I триггера 34, всегда находящегося в единичном состоянии, поступает сигнал "1". На выходе вычитателя 17 формируется сигнал "М-1". Он подается на первые входы перемножителей 32 и

33. Входно:. сигнал вычитателя 18 определяет значение Н . На другой вход вычитателя 18 поступает сигнал, определяющий величину, соответствующую номеру повторения информационных сигналов. В данном случае эта величина равна 1. Формируется номер повторения следующим образом. Для первого повторения на первом выходе блока 36 управления формируется управляющий сигнал, а на. втором и третьем выходах сигналов нет. Поэтому в логическом блоке 23 сигнал формируется только на выходе первого элемента

И 37, Этот сигнал пссле состветству1243101

Выходной сигнал второго сумматора;

13 подается на первый вход второго вычитателя 16, так как на другой его вход поступает сигнал ющего усиления в блоке 24 усилителей

25 подается на другой вход четвертого вычитателя 18. Поэтому на выходе вычитателя 18 формируется сигнал, соответствующий величине (Н-i). Этот сигнал подается на второй вход второго перемножителя 33 (на его первом входе — сигнал "M-1"). Выходной сиг- то на выходе вычитателя 16 формирус нал перемножителя 33 соответствует !О ется разностный сигнал величине (Н-i) (М-1). Он и подается на второй вход третьего сумматора 14. На выходе этого сумматора формируется сигнал

b; + 0 + 0 + (H-1) (M-1), Ъ =1,K.

Он поступает на первый вход второго вычитателя 15. На второй вход этого вычитателя подается сигнал

Н (M-1) преобразуется в сигнал, который и подается на второй вход первого вычитателя 15 (а также на второй вход второго вычитателя 16).

На выходе вычитателя 15 формируется сигнал

Н (M-1)

2 7 -1»7

b + (3-7) (М-1)—

Н (M-1) который формируется следующим образом. На первый вход перемноГ ителя 32 подается сигнал, соответст,вующий величине (М-1). На другой его 25 вход — сигнал, соответствующий величине 71. Поэтому на выходе перемножителя 32 формируется сигнал Я.(М-1) °

Этот сигнал с помощью делителя 26 который подается на вход второго порогового элемента 20. Если входной сигнал этого порогового элемента отрицателх,ный (или равен нулю), то на его выходе формируется управляюп;ий единичный сигнал. В противном случае единичный сигнал не формируется. Единичный выходной сигнал подается через второй элемент ИЛИ 8 на вход счетчика 22, изменяя при этом состояние последнего, и через третий коммутатор 30 на нулевой вход соответствующей ячейки памяти регистра 35

i(i.å. для входного сигнала b по перИ вому входу сумматора 13 соответствующий выходной сигнал элемента 19 за- 55 писывается в первую ячейку и т.д., для входного сигнала Ь вЂ” соответстМ венно в К-ю ячейку регистра 35).

Н(М-1)

2 3 который подается на вход второго элемента 20, с выхода которого этот сигнал через элемент НЕ 21 поступает на первый вход второго элемента ИЛИ 8.

На выходе элемента НЕ 21 появляется единичный сигнал только в том случае, когда выходной сигнал вычитателя 16 является положительным. Элемент НЕ 21 предназначен для того, чтобы использовать в схеме устройства идентичные пороговые элементы 19 и 20. Выходной сигнал элемента НЕ 21 обрабатывается так же, как и выходной сигнал порогового элемента 19.

Если после обработки сигнала Ь„1 на выходе счетчика 22 появится импульс переполнения, то с помощью этого сигнала осуществляется считывание информации из регистра 35 на выход устройства после чего с помощью этоУ

I го же сигнала в блоке 36 формируется i ,сигнал "Обнуление". Если же импульса переполнения не было, то из блока 36 управления подается сигнал начальной установки. счетчика 22 и регистра 35.

Далее с выхода квантизатора 2 пос. ледовательно подаются сигналы второго повторения Ь,2 bzz . bK2. Они последовательно подаются на первые входы сумматоров 12 и 13, на вход регистра 3 памяти и через открытый в это время второй элемент И 6 и элемент ИЛИ 7 на вход второго регистра

4 памяти считывается из первого регистра 3 памяти комбинация первого повтора. Таким образом, при обработке второго повторения информационных сигналов на первые входы сумматоров

12 и 13 подается соответствующий сим- вол второго повторения, на вторые входы сумматоров 12 и 13 подается соответствующий сигнал первого повторения через открытый сигналом со второго выхода блока 36 управления ключ

11 блока 9 ключей и соответствующий ключ блока 10 ключей. На третьем

1243101

10 входе каждого из сумматоров 12 и 13 сигналы отсутствуют. Выходные сигналы сумматоров 12 и 13 теперь определяются уже суммами первого и второго повторений соответствующих инфор"мационных сигналов и обрабатываются так же, как и сигналы первого повторения (точнее не первого повторения, а первого предъявления). При этом 1О следует только отметить, что ненулевые сигналы присутствуют на первом и втором входах логического блока 23, а единичный сигнал формируется только на втором ее выходе. Он усиливается 15 в блоке 24 усилителей, и в виде сигнала, определяющего номер второго повторения, появляется на первом входе четвертого вычитателя 18. При этом на входе первого порогового эле- 20 мента 19 формируется сигнал, соответствующий величине

Ъ, + Ь + (3 — 2) (M-1)—

25 а на входе второго порогового элемента 20 формируется сигнал, соответствующий величине ЗО

b. b — Н(И-1), V = 1 K.

)! J2 2 3

Наконец, на выходе квантизатора 2 формируются сигналы третьего повторе-З ния Ь 3 р Ь2 у, . е Ь, 3 информационных оигналов. B это время появляется сигнал на третьем выходе блока 36 управления, вследствие чего открываются все ключи блоков 9 и 10 ключей и открывается пороговый элемент И5. Символы третьего повторения сдвигают из регистра 3 символы второго повторения, а из регистра 4 — символы первого повторения. В результате на первых45 входах сумматоров 12 и 13 последовательно появляются символы третьего повторения, на вторых входах этих сум; маторов — символы второго повторения на третьих входах — символы пер

Ф

50 вого повторения. Следовательно, на выходах сумматоров 12 и 13 формируются сигналы, соответствующие сумме символов повторений одного и того же информационного символа. Выходные сигналы сумматоров 12 и 13 обрабаты55 ваются так же, как и при первом повторении. Единичные сигналы присутствуют теперь во всех входах логического блока 23, вследствие чего выходной сигнал формируется только на третьем его выхоце. Он усиливается и на первом входе вычитателя 18 определяет третий повтор. Входной сигнал порогового элемента 19 соответствует величине

H(M-1)

Kb; + (3-3)(И-1)2

1) входной сигнал элемента 20 определяется величиной

Н=3, b

H(M-1) 2

Таким образом, для одного из повторений решение принимается по всем информационным сигналам (срабатывает счетчик 22) и оно в виде двоичной кодовой комбинации из выходного регистра 35 считывается на выход устройства.

Очевидно, что скорость принятия решения зависит от качества канала связи: чем оно выше, тем быстрее принимается решение.

Из выражения (1) следует, что минимально возможное число повторений, по которым принимается достоверное решение, определяется как

Н (М-1) если Н вЂ” нечетно;

Н вЂ” — +1

2 если Н вЂ” четно

Следовательно, если канал хорошего качества, то решение при трехкратном повторении выносится по двум повторениям.

Ф о р и у л а и з о б р е т е н и я

1. Устройство для мажоритарного ,цекодирования в целом, содержащее аналоговый демодулятор, квантизатор, первый и второй регистры памяти, первый и второй элементы И, первый элемент ИЛИ, первый и второй сумматоры, соединенные последовательно первый вычитатель и первый пороговый элемент, соединенные последовательно второй вычитатель, второй пороговый элемент и элемент НЕ, третий и четвертый вы читатели, триггер, источник опорных

1243101 с соответствующими вторыми выходами источника опорных напряжений, входы блока усилителей соединены с соответствующими выходами логического блока, первый вход которого соединен с первым выходом блока управления, второй и третий входы логического блока объединены соответственно с первыми ов к о а

I напряжений и первый коммутатор, входы которого подключены к соответствующим

I первым выходам источника опорных напряжений, выход триггера соединен с первым входом третьего вычитателя, первый вход аналогового демодулятора является входом устройства, выход подключен к входу квантизатора, выческого блока, вход второго элемента НЕ является третьим входом логического блока и объединен с третьим выходом логического блока. ход которого соединен с первыми вхо- !О и вторыми управляющими входами блок да первого сумматора, первого эле- ключеи и подключены соответственно второму и третьему выходам блока уп и входом первого регистра равления, четвертый выход которого памяти, выход которого соединен с соедийен с вторым входом аналоговог первым входом второго элемента И, вто. демодулятора, первый вход которого рой вход которого объединен с вторым объединен с первым входом блока упвходом первого элемента И, вьгходы равления, пятый выход котопого соеди первого и второго элементов И соединен с вторыми входами первого и вто нены с входами первого элемента ИЛИ, рого элементов И, шестой выход блок выход которого подключен к входу втоуправления подключен к вторым входам рого регистра памяти, о т л и ч а юпервого и второго сумматоров и управ щ е е с я тем, что, с целью повышеляющим входам третьего и четвертого ния быстродействия, в него введены сумматоров, входы которых объединень блок управления, логический блок, с соответствующими входами второго блок усилителей, делитель, первый и элемента ИЛИ и подключены к выходам второй перемножители, второй, третий соответственно первого порогового и четвертый коммутаторы, второй элеэлемента и элемента НЕ, вьгходы тремент ИЛИ, счетчик, выходной регистр, тьего и четвертого коммутаторов соетретий сумматор и первый и второй динены соответственно с первыми и блоки ключей, первые и вторые входы вторьпги входами выходного регистра, которых объединены и подключены к выход которого является выходом уствыходам соответствующих регистров паройства, вход обнуления выходного ре мяти, выходы блоков ключей соединены гистра объединен с входом обнуления с входами соответственно первого и счетчика и.подключен к седьмому вывторого сумматоров, первые входы коходу блока управления, вход счетчика торых объединены, выход второго сум- 35 соединен с выходом второго элемента матора подключен к первому входу втоИЛИ, выход счетчика подключен к упрого вычитателя, выход первого сумравляющему входу выходного регистра матора подключен к первому входу треи второму входу блока управления, тьего суммато а, выход которого соевосьмой выход которого соединен с динен с первым входом первого вычита- 40 входами обнуления квантизатора и ретеля, второй вход которого объединен памяти. вторь-"- вхоДом рв ы т 2 Устройство по п 1 о т л и и подключен к выходу делителя, вход ч а ю щ е е с я тем, что логический

КОТОРОГО соединен с в"ходом пеРВОГО блок состоит из первого и второго перемножителя, первый вход которого

45 элементов И и первого и второго элеобъединен с первым входом второго ментов НЕ, выходы которых подключены перемножителЯ и поДключен к выхоДУ к первым входам соответствующих. элетРетьего вычита; елЯ, втоРой вхоД ко- ментов И, выходы которых являются со торого соединен с выхоДом пеРвого ответствующими выходами логического коммутатора, выход второго перемножи блока, второй вход первого элемента теля подключен к второму. входу тре И является первым входом логического тьего сумматора, а второй вход соеди блока, второй вход второго элемента нен с выходом четвертого вычитателя, первый вход которого подключен к вы та НЕ и является вторым входом. логиходу блока у-пилит елей, второй вход объе 55 динен с вторым входом первого перемножи теля и подключен к выходу второго коммутатора, входы которого соединены

1243101

1 4

3. Устройство по п. 2, о т л ич а ю щ е е с я тем, что блок управления содержит триггеры с первого по пятый, элементы. задержки с первого по пятый, первый, второй, третий счетчики, первый и второй ключи, первый и второй элементы ИЛИ и хронизатор, выход которого является первым входом блока управления, первый выход хронизатора подключен к первым входам первого и второго ключей и входам первого элемента задержки, перво.го счетчика и первого триггера, выход которого является первым выходом блока управления, выход первого счетчика соединен с входом второго триггера, выход которого подключен к второму входу первого ключа и первому входу третьего триггера и является ! вторым выходом блока управления, выход первого ключа соединен с первым входом первого элемента ИЛИ и входом второго счетчика, выход которого подключен к входам второго элемента задержки и четвертого триггера, выход которого соединен с вторым входом второго ключа и первым входом пятого триггера, выход которого является третьим выходом блока управления, второй выход хронизатора, выходы третьего триггера и первого элемента задержки являются соответственно чет1О вертым, пятым и шестым выходами блока управления., выход второго элемента задержки подключен к второму входу третьего триггера, выход второго ключа соединен с входом третьего счетчика и:вторым входом первого элемента

ИЛИ, выход которого является седьмым выходом блока управления, выход третьего счетчика. подключен через третий и четвертый элементы задержки соот- >

20 ветственно к второму входу пятого триггера и первому входу второго элемента ИЛИ,выход которого является восьмым выходомблока управления,авторой вход черезпятый элементзадержки сое25 цинен свторым входом блока управления.

1243101

Составитель О. Ревинский

Текред O.Сопко Корректор С. Шекмар

Редактор П. Коссей

Заказ 3716/55 Тираж 816

RHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4