Устройство циклового фазирования приемника дискретной информации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Сокращается время циклового . фазирования. Устр-во содержит распределитель 1, элемент И 2, коммута тор адресов (КА) 3, триггер 4, блок 5 обнаружения ошибок, запоминающий блок (ЗБ) 6, решающий блок 7 и формирователь сигналов записи-считьшания (ФСЗС) 8. На длительности каждого такта ФСЗС 8 формирует сигнал за- - писи-считьгаания, а блок 5 обнаруже- , ния ошибок вычисляет синдром комбинации , поступающей на его В5сод. По каждому такту в ЗБ 6 по адресу, определяемому положением распределителя 1 и КА 3, записьшается логическая 1, если вычисленный на данном такте синдром комбинации, находящейся в блоке 5 обнаружения ошибок, равен нулю, и логический О, если этот синдром не равен нулю. В режиме считьшание работы ЗБ 6 в каждом такте на его выходе появляется последовательность -логических 1, которая через решающий блок 7, триггер 4 и элемент И.2 поступает на выход устрва. Цель достигается введением КА 3, ЗБ 6 и ФСЗС 8. 2 ил: сл to 4 оо 00 фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCMOMV СВИДЕТЕЛЬСТВУ

13, "3

Такгпь

РН40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3496463/24-09 (22) 01.10.82 (46) 07.07.86. Бюл. У 25 (72) А. П. Чурус, В. И. Величко и В. И. Федорченко .(53) 621.394.662(088.8) (56) Патент США В 4189622, кл. Н 04 L 7/04, 1980.

Колтунов М. Н. и др. Синхронизация по циклам в цифровых системах связи.-M.: Связь, 1980, с. 121 †1.

Авторское свидетельство .СССР

786040. кл. Н 04,ь 17/16, 1980. (54) УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВА-

НИЯ ПРИЕМНИКА ДИСКРЕТНОЙ ИНФОРМАЦИИ (57) Изобретение относится к электросвязи. Сокращается время циклового фазирования. Устр-во содержит распределитель 1, элемент И 2, коммутатор адресов (КА) 3, триггер 4, блок 5 обнаружения ошибок, запоминающий (50 4 Н 04 L 7/08//Н 04 Ь 17/16 блок (ЗБ) 6, решающий блок 7 и формирователь сигналов записи-считывания (ФСЗС) 8. На длительности каждого такта ФСЗС 8 формирует сигнал за-— писи-считывания, а блок 5 обнаружения ошибок вычисляет синдром комбинации, поступающей на его вход. По каждому такту в ЗБ 6 по адресу, определяемому положением распределителя 1 и КА 3, записывается логическая

f I 11

1, если вычисленный на данном такте синдром комбинации, находящейся в блоке 5 обнаружения ошибок, равен нулю, и логический "0", если этот синдром не равен нулю. В режиме считывание работы ЗБ 6 в каждом такте на его выходе появляется последовательность логических "1", которая через решающий блок 7, триггер 4 и элемент И.2 поступает на выход устрва; Цель достигается введением КА 3, ЗБ 6 и ФСЗС 8. 2 ил .

1243148

30

55

Изобретение относится к электросвязи и может быть использовано при передаче данных для циклового фазирования аппаратуры передачи дискретной информации, в которой используются групповые корректирующие коды.

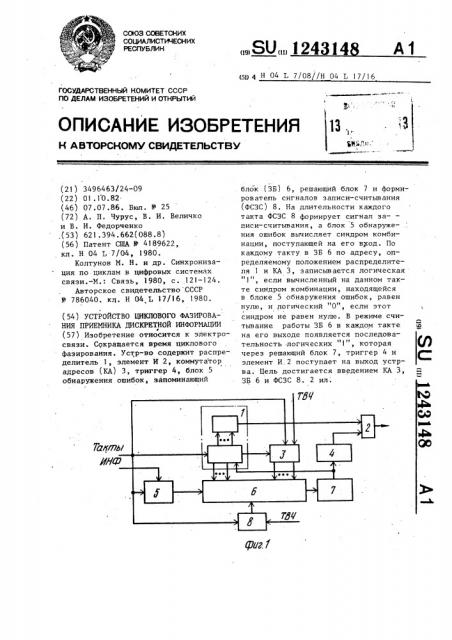

Цель изобретения — сокращение.времени циклового фазирования. . Ha фиг. 1 представлена структурная функциальная схема устройства циклового фазирования приемника дискретной информации; на фиг. 2. — временные диаграммы, поясняющие работу устройства.

Устройство циклового фазирования приемника. дискретной информации содержит распределитель 1, элемент И 2, коммутатор 3 адресов запоминающего блока, триггер,4, блок 5 обнаружения ошибок, запоминающий блок 6, решающий блок 7 и формирователь 8 сигналов записи-считывания.

Устройство циклового фазирования приемника дискретной информации работает следующим образом.

Блоки информации (фиг. 2 ) поступают в. блок 5 обнаружения ошибок, а тактовые импульсы (Фиг ° 2 а } поступают на тактовые входы блока 5 обнаружения ошибок, распределителя 1 и формирователя 8 сигналов и на первый вход коммутатора 3 адресов. По каждому тактовому импульсу распределитель 1 при сфазированном положении относительно принимаемых блоков (фиг. 2 ) формирует сигналы (фиг. 2 $ ), а при расфазированном положении — сигналы (фиг. 2 r ). На .длительности каждого такта формирователь 8 сигналов записи-считывания формирует сигнал (фиг. 2 y ) блок 5 обнаружения ошибок вычисляет синдром комбинации, поступающей на его вход.

По каждому такту в запоминающий блок 6 по адресу, определяемому положением распределителя 1 и коммутатором 3 адреса, записывается логическая "1", если вычисленный на данном такте синдром, находящийся в блохе 5 обнаружения ошибок комбинации, равен "О", и логический "0", и если этот синдром не равен 0

В режиме Считывание" (фиг. 2 ) ) работы запоминающего блока. 6 коммутатор 3 адреса последовательно устанавливает адрес текущего блока . информации (фиг. 2 г ), предыдущего блока информации (фиг. 2 q ) и т,д. (фиг, 2 а, + ), всего (ш — ) . .адресов предыдуших блоков информации. Величина н1 определяется длительностью интервала анализа синхронности приемника и в приведенном примере работы устройства соответствуют интервалу, который равен длительности четырех комбинаций. Таким образом, в режиме "Считывание" работы запоминающего блока 6 в каждом такте на его выходе появляется последовательность логических "1", соответствую-. щих нулевым синдромам предыдуших блоков {фиг. 2 О ). Такт, имеющий наибольшее количество считанных логических "1", соответствует концу принятого блока информации и выход-ной сигнал решающего блока 7 (фиг. 2.t- ) при несфазированном положении устанавливает распределитель 1 в синфазное положение (фиг. 2 1 ), а при сфазированном положении подтверждает синфазное положение распределителя 1 (фиг. 2 Х ).

Выходной сигнал решающего блока 7 (фиг, 2 к ) через триггер 4 формиI рует сигнал "Начало блока", поступает на выход устройства через элемент И 2.

Формула изобретения

Устройство циклового фазирования приемника дискретной информации, содержащее блок обнаружения ошибок, распределитель, последовательно соединенные решающий блок, триггер и элемент И, к второму входу которого подключен выход сигнала синхронизации распределителя, причем информационный и тактовый входы блока обнаружения ошибок являются соответствующими входами устройства, о т л и— ч а ю ш, е е с я тем, что, с целью сокращения времени циклового фазирования, введены запоминающий блок, формирователь сигналов записи-считывания и коммутатор адресов запоминаюшего блока, при этом тактовый вход блока обнаружения ошибок объединен с соответствующими входами распределителя, коммутатора адресов запоминающего блока и формирователя сигналов записи-считывания, выход которого подключен к входу записи-считыва,ния записывающего блока, тактовый выход распределителя подключен к другому входу коммутатора адресов эапо1243 1 48

К

Составитель В. Евдокимова

Редактор Н. Бобкова, Техред М.Ходанич

Корректор E . .Сирохман

Заказ 37)9/58 Тираж 624

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие,. г. Ужгород, ул. Проектная, 4 минающего блока, выход решающего блока подключен к установочному входу распределителя, адресные выходы коЮ торого и выходы коммутатора адресов запоминающего блока через запоминающий блок подключены к входу решающего блока, выход блока обнаружения ошибок подключен к информационному входу запоминающего блока.