Устройство для вывода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники. Оно может быть использовано и качестве выходного устройства универсальных ЭВМ для специализированного устройства в системах оперативной связи человека с вычислительной машиной. Целью изобретения является повышение быстродействия за счет сокращения времени редактирования выводимой информации путем сдвига части изображения вниз и вставки на раздвинутое место нижних Д У строк, что достигается введением блока формирования адреса. 1 з.п.ф-лы, 3 ил. € (Л

СОЮЗ СОВЕТСНИХ

СОЦИА ЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1

ÄÄSUÄÄ 1244 5

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOIVIV СВИДЕТЕЛЬСТВУ

ЯАМИ!; 1".

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3810767/24-24 (22) 10.11.84 (46) 15.07.86. Бюл. № 26 (71) Московский ордена Трудового

Красного Знамени инженерно-физический институт (72) О.Н.Цапко и В.Б.Шувалов (53) 681.327.11(088.8) (56) Авторское свидетельство СССР № 667979, кл. С 09 G 1/ 08, 1975.

Авторское свидетельство СССР № 614453, кл. G 09 G 1/08, 1976.

Авторское свидетельство СССР

¹ 930355, кл. С 09 G 1/08, 1979. (я) 4 G 06 F 3/12, G 09 G 1/88 (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники. Оно может быть использовано В качестве выходно— го устройства универсальных 3ВМ для специализированного устройства в системах оперативной связи человека с вычислительной машиной. Целью изобретения является повышение быстродействия за счет сокращения времени редактирования выводимой информации путем сдвига части изображения вниз и вставки на раздвинутое место нижних У строк, что достигается введением бло— ка формирования адреса. 1 з.п.ф-лы, щ

3 ил.

1244656!

Изобретение относится к вычислительной. технике, предназначено для вывода информации нз ЭВМ и может использоваться в системах автоматизации проектирования и конструирования, при автоматизированной обработке данных, в диалоговых системах.

Целью изобретения является увеличение быстродействия за счет сокращения времени редактирования выводимой информации.

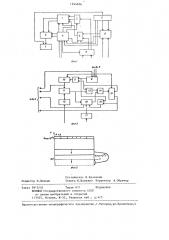

На фиг.1 представлена блок-схема устройства; на фиг.2 — функциональная схема блока формирования адресов ячеек блока памяти; на фиг.3 — расположение информации на экране.

Предлагаемое устройство содержит блок 1 памяти, дешифратор 2, распределитель 3 импульсов, блок 4 синхронизации, коммутатор 5, блок: 6 преобразования координат, блок 7 формирования адреса, первый счетчик 8, первый элемент И 9, второй счетчик

10, элемент 11 сравнения, первый регистр 12, второй элемент И 13, элемент ИЛИ 14, триггер 15, третий элемент И 16, второй регистр 1 7, счетчик 18.

Устройство работает следующим образом.

Блок 4 вырабатывает импульсы, соответствующие требуемой дискретизации растра индикатора,и управляет разверткой последнего. Эти импульсы поступают на распределитель 3, осуществляя. его временную привязку синхросигналу блока 4.

В блоке 1 памяти каждой точке изображения соответствует один бит, кодирующий ее яркость. При этом координаты изображения, записанного в блоке 1 памяти, образуют поле математических координат размерностью н ТИ

2 точек по горизонтали и 2 точек по вертикали с началом координат в нижнем левом углу.

Предлагаемое изобретение позволяет осуществлять раздвижку изображения на экране вниз, начиная с координаты на ьц строк. При этом нижние ац строк экрана перемещаются на раздвинутый участок в соответствии с фиг.3.

Для этого из 3ВМ заносятся соответственно в первый регистр 12 координата ч, а во второй регистр 17 значение ay . Регистры 12 и 17 имеют инверсные выходы. Сигнал кадро10

1I!>

40 ж3 вого гасящего импульса, поступающий из блока 4 синхронизации на первый вход блока 7, устанавливает счетчики 8 и -ilO и триггер 15 в состояние

0 . С началом видимого хода кадра индикатора из блока 4 на второй (тактовый) вход счетчика 8 поступа— ют импульсы с периодом, равным дли— тельности считывания одного слова из блока 1 памяти. Счетчик 8 осуществляет пересчет количества слов блока 1 памяти, уменьщающихся в одной строке изображения. Сигналы с выхода старшего разряда счетчика 8 через первый элемент И 9 поступают на тактовый вход счетчика 10, осу— ществляющего пересчет строк изображения. Выходы счетчика 10 подключены к входам элемента 11 сравнения, где осуществляется сравнение кода текущей строки с кодом 9, поступающим с инверсных выходов первого регистра 12. При совпадении кодов элемент"11 сравнения вырабатывает импупьс сравнения, который через второй элемент И 13 и элемент ИЛИ 14 перебрасывает по тактовому входу триггер 15 в состояние "1", а также производит запись начального кода д с инверсных выходов второго регистра 17 в счетчик 18. Счетчик

18 включает в себя m двоичных разрядов ° "0" на инверсном выходе триггера 17 запирает первый 9 и второй 13 элементы И, а "1" на прямом выходе триггера 15 подключает выход счетчика 8 слов к тактовому входу счетчика 18 через третий элемент И 16.

Счетчик 18 пересчитывает строки изображения до своего переполнения, т.е. отсчитывает вц строк. Сигнал переполнения с выхода счетчика 18 через элемент ИЛИ 14 переводит триггер 15 обратно в состояние "0". Тем самым осуществляется возврат к пересчету строк счетчиком 10. Выходы счетчика

10 и счетчика 18 образуют совместно с выходами счетчика 8 адреса считываемых из блока 1 памяти слов. При этом, если прямой выход триггера 15 равен "0", то к блоку 1 памяти через коммутатор 5 подключаются выходы счетчиков 8 и 10, а если прямой выход триггера 15 равен "1", то к входам блока 1 памяти подключаются выходы счетчиков 8 и 18. Для этого прямой выход триггера 15 подключается к управляющему входу коммутатора!

244656

5. При подаче на коммутатор 5 адресов считывания слов выходы счетчика

8 слов образуют младшие разряды адреса, а выходы счетчика 10 строк или, счетчика 18 — старшие. Таким образом, .г осуществляется считывание информации из блока 1 памяти.

Преобразование считанной информации в видеосигнал, а также запись информации в блок 1 памяти, осуществля- 10 ются идентично известному устройству.

Таким образом, изобретение позволяет достичь расширения функциональных возможностей за счет обеспечения возможности перестановки фрагментов 15 изобретения путем сдвига части изображения вниз и вставки нижних ц строк.

Формула изобретения 20

1. Устройство для вывода информации, содержащее блок памяти, дешифратор, распределитель импульсов, блок синхронизации, коммутатор, блок преобразования координат, входы пер25 вой группы которого являются информационными входами первой группы устройства, информационные выходы первой группы блока преобразования координат подключены к информационным 30 входам коммутатора, а информационные выходы второй группы подключены к информационным входам дешифратора, выходы которого подключены к входам первой группы блока памяти, выходы группы которого являются информационными выходами устройства, выходы группы блока синхронизации подключены к входам первой группы распределителя импульсов, выходы группы ко- 40 торого подключены к входам второй группы блока преобразования координат, первый и второй выходы распределителя импульсов подключены к первому и второму входам блока памяти, 4 третий и четвертый выходы распределителя импульсов подключены к управляющему входу дешифратора и к первому управляющему входу коммутатора соответственно, выходы коммутатора подключены к входам второй группы блока памяти, входы второй группы распределителя импульсов являются управляющими входами устройства, выходы второй группы распределителя импульсов являются управляющими выходами устройства, первый выход блока синхронизации является выходом

Д синхросигиала устройства, о т л и:,,( ч аю:ще е с я тем, что, с целью увеличения быстродействия за счет сокращения времени редактирования вы:водимой информации, в устройство введен блок формирования адреса, выходы группы которого подключены к адресным входам коммутатора, а выход подключен к второму управляющему входу коммутатора, первый и второй входы блока формирования адреса подключены к второму и третьему выходам блока синхронизации соответственно, входы первой и второй групп блока формирования адреса являются информационными входами второй группы устройства.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок формирования адреса содержит три счетчика, три элемента И, элемент сравнения, два регистра, элемент ИЛИ, триггер, R-входы первого, второго счетчиков и триггера являются первым входом блока, выход старшего разряда первого счетчика подключен к первым входам первого и третьего элементов И, выход первого элемента И подключен к тактовому входу второго счетчика, выходы которого подключены к входам первой группы элемента сравнения, выход которого подключен к R-входу третьего счетчика и к первому входу второго элемента И, выход которого подключен к первому входу элемента

ИЛИ, выход которого подключен к тактовому входу триггера, инверсный выход которого подключен к вторым входам первого и второго элементов И, прямой выход триггера подключен к второму входу третьего элемента И и является выходом блока, выход третьего элемента И подключен к тактовому входу третьего счетчика, выход переполнения которого подключен к второму входу элемента ИЛИ, входы первого регистра являются входами первой группы блока, инверсные выходы первого регистра подключены к входам второй группы элемента сравнения, входы второго регистра являются входами второй группы блока, инверсные выходы второго регистра подключены к входам группы третьего счетчика, выходы остальных разрядов первого счетчика, выходы второго и третьего счетчиков являются выходами группы блока.

1244656 фъ 1

Фбл б иа.

Составитель В.Базовкин

Техред Н, Бонк ало Корректор А. Обручар

Ре да к то р Л. По вх ан

Заказ 391 5/51 Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, 1!осква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r . Ужгород, ул. Проектная,4