Двоичный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной и предназначено для построения арифметикр-логических устройств. Цель изобретения - уменьшение количества оборудования. Сумматор содержит шесть переключателей тока, каждый из которых построен на информационном и опорном транзисторах , три источника тока, четыре детектора тока и четыре эмиттергалх повторителя . В качестве детекторов тока могут быть использованы схемы, состоящие из параллельно соединенных резистора и диода, t ил,, 1 табл. 1чЭ 4ib ;ik О О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„SU„„1244661

А1 д11 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Pü >E л g

1б, ИВАМИ i a. .s...

®

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3777737/24-24. (22) 08.08.84

:(46) 15.07.86. Бюл. И- 26 (72) А.И.Малинин, Ю.Н.Дубов, В.Ç.Шнитман и А.П.:Коваленко (53) 681.325.54(088.8) (56) Авторское свидетельство СССР

Ф 760094, кл. G 06 F 7/50, 1976, Авторское свидетельство СССР

Ф 429422, кл. G 06 Р 7/50, 1972. (54) ДВОИЧНЫЙ СУММАТОР (57) Изобретение относится к области вычислительной техники и предназначено для построения арифметико-логических устройств. Цель изобретения— уменьшение количества оборудования.

Сумматор содержит шесть переключателей тока, каждый из которых построен на информационном и опорном транзисторах, три источника тока, четыре де-. тектора тока и четыре эмиттерных повторителя. В качестве детекторов тока могут быть использованы схемы, состоящие из параллельно соединенных резистора и диода. 1 ил,, 1 табл.

Ток протекает через транзисторы

Вход

24

25 г1 ) 20 22 23

1,3. .5,7

1,3 5,7

1,3 6,8

1,3 6,8

2,4 5,7

2,4 5,7

9,11

10,12

9,11

10, 1:?

9,11

10, 1:?

2,4 6,8

9,11

2,4 6,8

10,12

1 12446

Изобретение относится к вычислительной технике и предназначено для построения арифметическо-логических устройств.

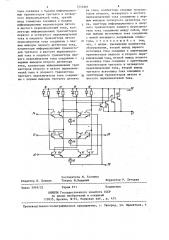

Цель изобретения — уменьшение количества оборудования. .На чертеже приведена принципиальная схема двоичного сумматора.

Сумматор содержит первый переклю- 10 чатель тока, построенный на информа- . ционном и опорном транзисторах 1 и 2; второй, третий, четвертый, пятый, шестой переключатели тока, построенные соответственно на информационных 15 и опорных транзисторах 3 и 4, 5 и б, 7 и 8, 9 и 10, 11 и 12; первый, вто- рой и третий источники тока 13, 14 и

15 соответственно; детекторы 16, 17, 18 и 19 тока; эмиттерные повторители 2п

20, 21, 22, 23 на транзисторах, входы

24, 25, 26, выход 27 суммы, шину 2К опорного напряжения, шину 29 питающеФ ор мула из об ре.те ния

Двоичный сумматор, содержащий шесть переключателей тока, состоящих каждый из информационного и опорного транзисторов, четыре эмиттерных повторителя, четыре детектора тока, три источника тока, причем первый вход сумматора соединен с базами информационных транзисторов первого второго переключателей тока, эмиттеры транзисторов эмиттерных повторителей объединены между собой и сое61 2

ro напряжения, шину 30 нулевого потенциала.

Для описания работы сумма. тора рассмотрены возможные сочетания сигналов на тех входах, приведенных в таблице, где "1" обозначает высокий, а 0 — низкий из двух возможных уровней напряжения.

В качестве детекторов тока могут быть использованы схемы, состоящие из параллельно соединенных резистора и диода,, причем первые выводы детектора тока должны быть соединены с катодами соответствующих диодов первыми выводами соответствующих резисторов и базами транзисторов соответствующих эмиттерных повторителей, вторые выводы детекторов тока должны быть соединены с вторыми выводами соответствующих резисторов, с анодами соответствующих диодов и подключены к шине нулевого потенциала сумматора.

Напряжение на вы- Выход ходах ЭП 27

0 0 0 . 1

0 0 0 0

0 0 0 0

0 1 0 0

0 0 0 0

0 0 1 0

1 0 0 0

0 0 0,0

I динены с выходом cymar сумма. тора, базы опорных транзисторов переключателей тока объединены между .собой и соединены с шиной опорного напряжения сумматора, первые выводы детекторов тока подключены к базам транзисторов соответствующих эмиттерных повторителей, вторые выводы детекторов тока соединены с коллекторами транзисторов эмиттерных повторителей и подключены к шине нулевого потен-. циала сумматора, второй вход суммаСоставитель М. Есенина

Техред М.Ходанич Корректор О. Луговая

Редактор Л. Повхан

Тираж 671

Подписное

Заказ 3919/52

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12446 тора соединен с базами информационных транзисторов третьего и четвертого переключателей тока, третий вход сумматора соединен с базами информационных транзисторов пятого и шестого переключателей тока, кол-. лекторы информационных транзисторов первого и четвертого переключателей тока и опорного транзистора пятого переключателя тока соединены с пер- 10 вым выводом первого детектора тока, коллекторы информационных транзисторов третьего и шестого переключателей тока и опорного транзистора первого переключателя тока соединены с первым выводом второго детектора тока, коллекторы информационных транзисторов второго .и пятого переключателей тока и опорного транзистора третьего переключателя тока соедине- 2о ны с лервым выводом третьего детекто.

61 4 ра тока, коллекторы опорных транзисторов второго, четвертого и шестого переключателей тока соединены с первым выводом четвертого детектора тока,.эмиттеры информационного и опорного транзисторов каждого переключателя тока соединены между собой, первые выводы источников тока соединены с шиной питающего напряжения сумматора, отличающийся тем, что, с целью, уменьшения количества оборудования, второй вывод первого .источника тока соединен с эмиттерами транзисторов первого и второго переключателей тока, второй вывод второго источника тока соединен с эмиттерами транзисторов третьего и четвертого переключателей тока, второй вывод третьего источника тока соединен с эмиттерами транзисторов пятого и шестого переключателей тока.