Устройство для умножения двух чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и технической ;кибернетики, преимущественно к устройствам для цифровой обработки сигналов . Цель изобретения - повьппение быстродействия работы устройства. Поставленнай цель достигается тем, что в устройство введены группа элементов И и группа сумматоров по модулю два, причем выход переноса п-разрядного сумматора соединен с (1+1)-м входом i-ro (, ..., n-.l) элемента И и вторым входом первого сумматора по модулю два, j-й вход i-го (, ..., п-1, , ..., i) элемента И соединен с j-м выходом суммы п-разрядного сумматора, выходы элементов И соединены с первыми входами соответствующих сумматоров по модулю два, начиная со второго, вторые входы -. которых соединены с соответствующими выходами блока коррекции, а их выходы являются выходами устройства. 1 з.п. ф-лы, 2 ип. с $ (П tC 4 4 Од Од ISD

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1244662 (59 4 G 06 F 7/52

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (а

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3814239/24-24 (22) 20.11.84 (46) 15.07.86. Бюл. Ф 26 (72) Л.В.Вариченко, В.В.Вишневский

P.Á.Ïîïîâè÷ и Ю.А.Томик (53) 681.325(088.8) (56) Рабинер Л,, Гоунд Б. Теория и применение цифровой обработки сигналов. М.: Мир, 1978.

Авторское свидетельство СССР

0 - 1179322, кл. G 06 F 7/52, 1984. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВУХ

ЧИСЕЛ (57) Изобретение относится к области вычислительной техники и технической ,кибернетики, преимущественно к устройствам для цифровой обработки сигналов. Цель изобретения — повыщение быстродействия работы устройства.

Поставленная цель достигается тем, что в устройство введены группа элементов И и группа сумматоров по модулю два, причем выход переноса и-разрядного сумматора соединен с (+1)-м входом i-ro (i-=1, ..., -п-1) элемента

И и вторым входом первого сумматора по модулю два, j-й вход i-ro (i=1, п-1, j=1, ..., i) . элемента И соединен с j-м выходом суммы п-pasрядного сумматора, выходы элементов И соединены с первыми входами соответствующих сумматоров по модулю -два, начиная со второго, вторые входы которых соединены с соответствующими Pg выходами блока коррекции, а их выходы являются выходами устройства. 1 з.п. ф-лы, 2 ил.

С:

1 124

Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в системах цифровой обработки сигналов (в частности, изображений), а также в системах кодирования, принцип действия которых базируется на теории конечных колец.

Целью изобретения является повы-. шение быстродействия работы устройства.

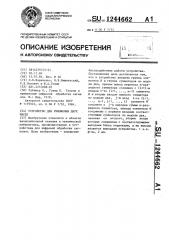

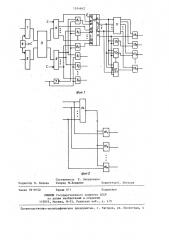

На фиг. 1 представлена схема уст— ройства для умножения двух чисел; на фиг. 2 — блок коррекции результата.

Устройство для умножения двух чисел (фиг. 1) содержит регистры, множимого 1 и множителя 2, блок 3 формирования частичных произведений, регистры младших 4 и старших 5 разрядов произведения, блок 6 синхро- низации, элемент НЕ 7, группу 8 эле- ментов И, группу 9 элементов И, и-раз рядный сумматор 10, блок 11 коррекции результата, группу 12 элементов И, г 1уппу 13 сумматоров по модулю 2.

Блок 11 коррекции результата (фиг. 2) содержит п — входовой элемент

И-НЕ 14 и группу 15 элементов И.

Устройство работает следующим образом.

Разряды множимого и множителя поступают в регистры 1 и 2 множимого и множителя и по синхроимпульсам блока 6 заносятся в них. Блок 3 формирует попарные произведения разрядов множимого и множителя и производит сложение попарных произведений одинакового веса с учетом возникающих переносов. На выходе блока 3 образуются разряды обычного произведения множимого и множителя. По синхроимпульсу С от блока 6 младшие разряды произведения заносятся в регистр 4

J а старшие разряды — в регистр 5, В режиме обычного умножения на вход элемента НЕ 7 подается сигнал, соответствующий логической "1". Тогда на выходах элементов И группы 8— логические нули, а младшие разряды произведения проходят через и-разрядный сумматор 10 и блок 11 коррекции результата на первые входы сумма торов по модулю два группы 13. Так как сигнал переноса P на выходе сумматора 10 соответствует логическому

1I 11

0, то на выходах элементов И группы 12 — логические нули:. Поэтому младшие разряды пропускаются на выходы сумматоров по модулю два груп4662 2 пы 13. Сигнал логической "1" на входе элемента НЕ 7 пропускает старшие

I разряцы произведения на выходы элементов И группы 9.

В режиме умножения по модулю 2 — 1

5 на вход элемента НЕ 7 подается сигнал логического "0". При этом старшие разряцы произведения проходят через элементы И группы 8 и прибавляются к соответствующим младшим разрядам

11+ Л в сумматоре 10 (так как 2 совпадает с 2 по модулю 2"-1) . Возможны следующие соотношения между резульи татом S сложения и модулем S < 2 -1.

Сигнал переноса сумматора !О равен

"0" и на выходах элементов И группы

12 — логические нули. Полученные разряды суммы проходят через блок 11 коррекции результата и группу 13 сумматоров по модулю два на выходы устройства. и

S = 2 -1. Сигнал переноса сумматора 10 также равен "0 ", на выходах элементов И группы 12 — логические нули. На всех выходах суммы сумматора 10 — логические единицы. Блок 11 преобразует слово 11 ... 1 в слово и разрядов

00 ... С, которое проходит на выходы п разрядов

30 устройства. рл

S ) 2 -1. Сигнал переноса сумматора 10 равен логической "1", его необходимо прибавить в младший раз— ряд полученного слова сумм S S „

S SÄ . Так как слагаемые на входах сумматора, 10 не больше 2" -1, то результат S (с учетом переноса Р) не больше 2" " -2. Тогда слово сумм не больше ? -2, т.е. хотя бы один .его разряд равен,"0 1, и оно пропускается через блок 11 на первые входы сумматоров по модулю два группы 13; i-й элемент И (1=1, ..., и-1) группы 12 формирует перенос в (i+i)-й разряд при прибавлении переноса P к слову сумм.

Перенос в (i+1) é разряд становится равным 11", если все прецыдущие разряды S, ..., S слова сумм

5" равняются "1" ° Сумматоры по модулю два группы 13 производят прибавление сформированных переносов к соответствующим разрядам слова сумм.

Блок 11 коррекции результата устраняет неоднозначность представления нуля в режиме умножения по модулю: за 00 ... О, и разрядив и разрядив3 1244 а остальные слова пропускают без изменений.

В блоке 11 при подаче на его входы всех единиц на выходе элемента И-НЕ

14 появляется ",О" и на выходах эле-. ментов И группы 15 — логические нули.

При подаче любого слова на выходе элемента 14 — "1.", и слово проходит на выходы блока 11. I0

Формула из обретения

1. Устройство для умножения двух чисел, содержащее регистр множимого, регистр множителя, блок формирования частичных произведений, блок синхронизации, регистры старших и млад— ших разрядов произведений, элемент НЕ, две группы элементов И по п элементов в каждой, (n -разрядность множимого и множителя), п-разрядный сумматор и блок коррекции результата, входы которого соединены соответственно с выходами суммы и-разрядного сумматор ра, входы первого слагаемого которого ZS соединены с выходами регистра младших разрядов произведения, а входы второго слагаемого — с выходами элементов И первой группы, первые входы которых соединены с выходом элемента О

НЕ, вход которого соединен с входом установки режима устройства и первыми входами элементов И второй группы, выходы которых соединены с выходами старших разрядов произведения устройства, а вторые входы — с вторыми

35 входами элементов И первой группы и выходами регистра старших разрядов произведения, информационные входы которого соединены с выходами стар40 ших разрядов блока формирования частичных произведений, выходы младших разрядов которого соединены с информационными входами регистра младших разрядов произведения, а первая и вторая группа входов — с б62 выходами регистров множимого н множителя соответственно, информационные входы которых соединены соответственно с входами мчожимого и множителя устройства, выходы блока синхронизации соединены с синхровходами регистров множимого, множителя, старших и младших разрядов произведений, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены третья группа и-1 эле— ментов И, причем i-й элемент И третьей группы (i=1, ..., и-1) содержит

i+1 входов, и группа и сумматоров по модулю два, выходы которых соединены с-выходами младших разрядов произведения устройства, шина нулевого потенциала которого соединена с входом переноса и-разрядного сумматора, выход переноса которого соединен с первыми входами элементов И третьей группы и входом первого слагаемого первого сумматора по модулю два группы, входы первых слагаемых сумматоров по модулю два группы, начиная со второго, соединены с выходами элементов И третьей группы соответственно, входы вторых .слагаемых сум. маторов по модулю два группы соединены с выходами блока коррекции, 1-й выход суммы и-разрядного сумматора (j=1, ..., n) соединен с (j+1)-м входом i-х элементов И третьей группы.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок коррекции результата содержит и-входовой элемент И-НЕ и группу элементовИ, выходы которых соединены с выходами блока коррекции результата, а первые входы — с выходом и-входового элемента И-НЕ, входы которого соеди иены с входами блока коррекции результата и вторыми входами элементов

И группы соответственно.

12446б2

Que. 1

Составитель E. Захарченко

Редактор Л. Повхан Техред .М.Ходанич Корректор О. Луговая

Заказ 3919/52 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. ч/5

Производственно-полиграфическое предприятие, г. Ужгород. ул. Проектная, 4