Устройство для сопряжения электронно-вычислительной машины с каналами связи

Иллюстрации

Показать всеРеферат

Изобретение относится к области вьиислительной техники и может быть использовано в телекоммуникационных .системах. Целью изобретения является уменьшение времени преобразования информации, содержащейся в буферной памяти. Устройство содержит узел коммутации , преобразователь кода, буферную память, узел управления коммутацией каналов, счетчик, распределитель импульсов, коммутатор памчти, первый, второй, третий триггеры, регистр управления, первый,.второй, третий элементы И и элемент задержки. Устройство за один сеанс связи обеспечивает прием или вьщачу всей информации в каналы связи. 1 ил. to 4: 4 О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU „„1244610. (5ц 4 С 06 F 13/22

I!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

С Я

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) .3821369/24-24 (22) 06. 12.84 (46) 15.07.86. Бюл. ¹ 26 (72) В.П.Мочалов (53) 681.3(088.8) (56) Авторское свидетельство СССР .№- 516031, кл. G 06 F 3/00, 1973.

- Авторское свидетельство СССР № 760075, кл. G 06 F 3/04, 1980. . (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ (57) Изобретение относится к области вычислительной техники и может быть использовано в телекоммуникационных.системах. Целью изобретения является уменьшение времени преобразования информации, содержащейся в буферной

1 памяти. Устройство содержит узел коммутации, преобразователь кода, буферную память, узел управления коммутацией каналов, счетчик, распределитель импульсов, коммутатор памчти, первый, второй, третий триггеры, регистр управления, первый, второй, третий элементы И и элемент задержки.

Устройство за один сеанс связи обеспечивает прием или выдачу всей информации в каналы связи. 1 ил.

1 124

Изобретение относится к вычислительной технике и может быть использовано в телекоммуникационных системах.

Целью изобретения является уменьшение времени передачи информации.

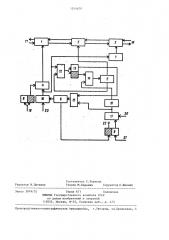

На чертеже представлена структурная схема устройства.

Устройство содержит узел 1 коммутации, последовательно-параллельный преобразователь 2 последовательного кода в параллельный и обратно, буферную память 3, узел 4 управления коммутацией каналов, счетчик 5, распределитель 6 импульсов, коммутатор 7 памяти, первый триггер 8, второй триггер 9, регистр 10 управления, первый элемент И 11, элемент ИЛИ 12, третий триггер 13, второй элемент И 14, третий элемент. И 15, элемент 16 задержки, передающие и приемные вход и выход 17 каналов связи, информационные вход и выход 18 ЭВМ, выход 19 разрешения передачи -ЭВМ, выход 20 тактовой частоты ЭВМ, выход 21 запуска

ЭВМ, вход 22 сигнализации режима ЭВМ, выход 23 выбора страницы ЗВМ.

Устройство работает следующим образом.

Регистр 10 управления подразделяется на части, каждая иэ которых со. ответствует определенному номеру канала связи, а каждому позиционному разряду — страница в буферной памя—

10 то сигнал с регистра 10 подается на дешифратор 7 для подключения соответствующей страницы буферной паМяти и через элемент ИЛИ 12 переключает триггер 13 в нулевое состояние. При этом следующие тактовые импульсы через элемент 16 задержки и элемент И 14 поступают на счетчик 5. С первого выхода счетчика сигналы подаются на вход преобразователя 2. После завершения преобразования сообщения с второго выхода счетчика 5 снимается сигнал, который через элемент ИЛИ t2. переключает триггер 13 в единичное состояние.

Схема И 14 открывается, и тактовые импульсы снова поступают через распределитель 6 импульсов на опрос регистра 10. Таким путем последовательно опрашивается весь регистр 10 и в каждый канал считывается информация с заданных, страниц буферной .памяти. В режиме приема информации работает триггер 8, который через узел 4 подключает канады связи к преобразо4670 2 триггер 9. Тактовый импульс через элементы И 11 и 15 подается на распре делитель 6 импульсов и опрашивает первый разряд регистра 10. Если в этом разряде регистра записан 0", то состояние элементов устройства не меняется и следующий тактовый иМпульс поступает на опрос следующего разряда регистра t0. Если же записана "1", 35

40 ти 3. Все разряды регистра 10 при помощи распределителя 6 импульсов последовательно опрашиваются в соответствии с их приоритетами и в порядке их нумерации. При записи информации в режиме обмена в регистре 10 записывается код, соответствующий режимуобмена. Если, например, в буферной

f памяти 3 содержится K страниц для / каналов связи, то объем регистра 10 по режиму обмена должен содержать

k . .М разрядов, причем каждая л/-я часть его выделяется узлом 1, как при надлежащая к режиму обмена только в одном канале . В один канал связи считывается информация со всех сторон буферной памяти, которым соответствовали единицы в регистре 10. Подключение той или иной страницы буферной памяти осуществляется через коммутатор 7. Преобразование сообщения осуществляет преобразователь 2 по тактовым импульсам.

В режиме обмена информацией сигнал обращения к устройству поступает на

55 вателю 2. Запись информации в буферную память осуществляется также в соI ответствии с информацией на регистр

10 о режиме обмена. В этом случае в каждый разряд регистра 10 должна быть записана -" 1", По окончании приема или передачи информации с ° вывода распределителя импульсов снимается сигнал, который поступает на триггер 9 и переводит его в нулевое состояние. В этом слу чае на выходе 22 формируется сигнал готовность". Таким образом, при обращении к устройству все разряды управления опрашиваются тактовыми импульсами„ причем если из регистра управления считывается "0", то очередным сигналом опроса является очередной .тактовый импульс, если " 1" — то очередной сигнал опроса формируется через интервал времени, равный времени преобразования страницы. Зто приводит к уменьшению времени преобразова.ния информации в буферной памяти, 3 1244

Формул а изобретения

Устройство для сопряжения элект.ронно-вычислительной машины,с каналами связи, содержащее узел коммутации, преобразователь последовательного кода в параллельный и обратно, буферную память, дешифратор памяти, узел управления коммутацией каналов,. регистр управления, первый, второй триггеры, первый элемент И, причем 10 первые информационные вход и выход узла коммутации соединены соответственно с передающим и приемным каналами связи, вторые информационные вход и выход узла коммутации соединены 15 соответственно с первыми информационными выходом и входом преобразоватеI ля последовательного кода в параллель.г ный и обратно, вторые информационные вход и выход которого соединены соот- gp ветственно с первыми информационными выходом и входом. буферной памяти, вторые информационные вход и выход которой соединены соответственно с информационными выходом и входом 25 электронно-вычислительной машины (ЭВМ), вход выбора канала узла ком мутации соединен с выходом узла управления коммутацией каналов, вход разрешения приема и вход выбора кана-Зо ла которого соединены соответственно с выходами первого триггера и регистра управления, информационный вход которого и счетный вход первого триггера соединены соответственно с вы35 ходами адреса и разрешения приема ЭВМ, выход регистра управления соединен с входом дешифратора адреса, выход которого подключен к адресному входу

670 4 буферной памяти, единичный вход второго триггера соединен с выходом запуска ЭВМ, единичный и нулевой выходы второго триггера подключены соответственно к первому входу первого элемента И и к входу сигнализации режима ЭВГ1, второй вход первого эле— мента И соединен с тактирующим выходом ЭВМ, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени передачи информации, в него введены элемент ИЛИ, второй, третий элементы И, третий триггер, счетчик, элемент задержки, распределитель импульсов, причем выход регистра управления подключен к первому входу элемента

ИПИ, второй вход и выход которого подключены соответственно к информационному выходу счетчика и счетному входу третьего триггера, единичный и нулевой выходы которого подключены к первым входам соответственно второго и третьего элементов И, вторые входы которых подсоединены соответственно к выходу элемента задержки и к выходу первого элемента И, выходы второго и третьего элементов И соединены соответственно со счетным входом счетчика и входом распределителя импульсов, первый и второй выходы которого подключены соответственно к синхронизирующему входу регистра управления и к нулевому входу второго триггера, выход первого элемента И соединен с входом элемента задержки, выход переноса счетчика соединен с входом разрешения преоб- . разователя последовательного кода в параллельный и обратно.

1244670

Составитель С.Бурухин .

Техред М.Ходанич Корректор С.Шекмар

Редактор М. Циткина

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 3919/52 (Производственно-полиграфическое предприятие, r.Óæãoðoä, ул.Проектная, 4