Формирователь уровня считывания

Иллюстрации

Показать всеРеферат

Изобретение относился к вь1числительной технике и может быть использовано в биполярных статических запоминающих устройствах. Целью изобретения является повышение точности формирования уровня считывания. Формиро тватель уровня Считывания содержит . переключающий, нагрузочный, усилительный и три согласующих транзистора , первьй диод, два источника тока, шесть резисторов. Повышение точности . формирования уровня считывания достигается введением четвертого согласующего транзистора, .что обеспечивает увеличение тока, протекающего через нагрузочный транзистор. Введение в формирователь второго диода, третьего источника тока и седьмого резистора позволяет учесть перепад логических уровней. 1 з.п.. ф-лы, 3 ил. о ю 4

СОЮЗ СОВЕТСКИХ

СоаМЛИСТИЧЕСНИХ

РЕСПУБЛИН се С11С

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Б (54) ФОРМИРОВАТЕЛЬ УРОВНЯ СЧИТЫВАНИЯ (57) Изобретение относится к вычислительной технике н может быть использовано в биполярных статических запоминающих устройствах. Целью нзобрете(21) 3796995/24-24 (22) Oi 10.84 (46) 15.07.86. Бюл. ¹ 26 (72) С.А,Дорожкнн и А.g.Ìàêàðoâ (53) 681.327(088.8) (56) Патент США ¹ 4099070, кл. 307-238, опублик. 1976.

Патент ФРГ ¹ 2738187, кл. 42 t 2, G 11 C 7/00, опублик. 1979.

„.Я0„„1244718 А1 ния является повышение точности формирования уровня считывания. Формиро .ватель уровня считывания содержит переключающий, нагрузочный, усилительный н три согласующих транзистора, первый диод, два источника тока, шесть резисторов. Повышение точности формирования уровня считывания достигается введением четвертого согласующего транзистора„ .что обеспечивает увеличение тока, протекающего через нагрузочный транзистор. Введение в формирователь второго диода, третьего источника тока и седьмого резистора позволяет учесть перепад логических уровней. 1 з.п.. ф-лы, 3 ил.

1244718

1

Изобретение относится к вычислительной технике и может быть использовано в биполярных статических запоминающих устройствах.

Цель изобретения — повьш ение точности формирования уровня считывания.

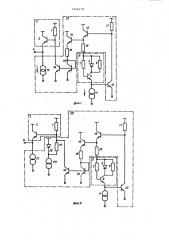

На фиг, 1 приведена принципиальная электрическая схема формирователя уровня считывания; на фиг. 2 — принципиальная .электрическая схема вари- 1О анта выполнения формирователя уровня считывания, в котором учитывается изменение перепада уровней в ячейке памяти; на фиг. 3 — диаграмма зависимости уровня считывания от характе — 15 ристик ячейки памяти, поясняющая работу формирователя.

Формирователь уровня считывания, (фиг. 1) содержит первый резистор 1 и первый согласующий транзистор 2, 2О выполняющие функцию эквивалента адресного формирователя 3 с выходом ч, первый диод 5, нагрузочный транзистор 6, второй 7 и третий 8 резисторы, выполняющие функцию эталонной ячейки 9 памяти, переключающий транзистор 10, первый 11 и второй 12 источники тока, второй 13 и третий 14 согласующие, усилительный 15 и четвертый согласующий 16 транзисторы и 30 резисторы 17-19 с четвертого по шестой, выполняющие функцию блока 20 регулирования. Во вторбм варианте выполнения формирователь уровня считывания содержит также (фиг. 2) седьмой резистор 21, второй диод 22 и третий источник 23 тока.

На фиг. 3 показаны зависимости

А, В, С падения напряжения Uö„ — П...,р

Ige U > — потенциал словарной шины, — потенциал разрядной шины, от тока I „, протекающего через ячейку 9 памяти.

В качестве. эталонной ячейки 9 памяти могут быть использованы ячейки различных типов: тиристорные, инжекционные, с резистивными нагрузками °

Формирователь уровня считывания работает слецующим образом.

При изменении величины резистора 18 или коэффициента усиления тока транзистора 6 меняется падение напряжения на резисторе 7 (фиг. 1). Сумма падений напряжений на резисторах 7 и 18 выделяется на резисторе 19. Поэтому ток через резистор 19 изменяется в соответствии с изменением напряжения на резисторе 7, Так как ток резистсра 19 ранен току, протекающему через транзистор 15, а токи транзисторов 15 и 16 соотнося ;æå, как соотносятся площади их эмиттеров, то ток коллектора транзистора 19 изменяется пропорционально изменению напряжения на резисторе 7. На резисторе 1, через который протекает ток коллектора транзистора 16, выделяется перепад напряжения, отслеживающий изменение напряжения на резисторе 7. Этот перепад напряжения через транзистор 2, работающий в режиме эмиттерного повторителя„ передается на выход. Ток источника 12 тока создает на транзисторе 2 и резисторе 1 падение напряжения, равное падению напряжения на ацресном формирователе (на фиг.1 не показано)„ в результате чего на выходе 4 устанавливается потенциал (относительно шины нулевого потенциала), ра.вный

1)С% (KTq6 M 2 ) 3 6312 где U — потенциал считывания на выходе 4;

1 кт, — ток коллектора транзистора 16;

Т@.2 — ток базы транзистора 2;

R — номинал резистора 1;

Uв, — пацение напРЯжениЯ HB IIBPe ходе база-эмиттер транзистора 2.

Величина этого потенциала отличается от потенциала верхнего логического уровня в ячейке памяти накопителя (на фиг, 1 не показано) на величину падения напряжения на резисторе 18.

На фиг. 3 кривая А характеризует граничный случай„ когда. весь ток выборки втекает в ячейку 9 и не течет в транзистор 10. Кривая В соответствует случаю, когда ток выборки делится поровну — одна половина течет в ячейку 9, другая половина — в транзистор 10. Кривая С соответствует случаю, когда большая часть тока вы— борки течет в транзистор 10. Точки

А„, В,, С, отражают случай работы формирователя в первом варианте выполнения (фиг. 1), не позволяющем учитывать зависимость уровня считывания от параметров ячейки. Наклон линии А„, В, С обуславливается тем, что ток выборки в формирователе уровня считывания делится на две части„ Первая часть (большая) течет в ячейку 9 памяти, а вторая — в блок 20.

1244718

Использование предлагаемого формирователя позволяет избавиться от деления токов между блоком 20 и эталонной ячейкой 9.

Формирователь уровня считывания во втором варианте выполнения, позволяющем учитывать перепад логических уровней в ячейке памяти (фиг. 2), работает следующим образом..

При изменении параметров ячейки памяти накопителя формирователь уровня считывания устанавливает уровень считывания ниже высокого логического уровня в ячейке памяти накопителя на величину падения напряжения на резисторе 18 (фиг. 1), в результате че.го весь ток выборки, за исключением тока эмиттера закрытого транзистора 10, течет в ячейку памяти накопи-теля. Этот режим (фиг. 3) характеризуется точками А„, В, С . В этом случае положение уровня считывания определяется соотношением резисторов 1 и 21. Резистор 19 выбирается так, чтобы скомпенсировать ошибку в положении уровня считывания, вносимую базовым током транзистора 1б.

Формула изобретения

1. Формирователь уровня считывания, содержащий переключающий, нагрузочный, усилительный и согласующие транзисторы, первый диод, источник тока и резисторы, причем база первого согласующего транзистора соединена с первым выводом первого резистора, а коллектор и второй вывод первого реэиСтора подключены к шине нулевого потенциала, выход первого источника тока соединен с эмиттером нагрузоч ного транзистора, база которого под" ключена к первому выводу второго резистора, а коллектор соединен с первым выводом третьего резистора и ка- . тодом первого диода, коллектор переключающего транзистора подключен к первому выводу четвертого резистора и базе второго согласующего транзистора, первый вывод пятого резистора подключен к базе третьего согласующего транзистора, коллекторы второго и третьего согласующих транзисторов и второй вывод четвертого резистора соединены с шиной нулевого потенциала, коллектор и база усилительного транзистора подключены к первому вы10 воду шестого резистора, входы первого и второго источников тока соединены с шиной питания, о т л и ч а юшийся тем, что, с целью повышения очности формирования уровня считывания, в формирователь введен четвертый согласующий транзистор, коллектор которого подключен к базе первого согласующего транзистора, а база соединена с базой усилительного транзистора, эмиттер которого и эмиттеры четвертого согласующего и переключающего транзисторов подключены к шине питания, причем эмиттер второ. го согласующего транзистора соединен

25 с первым выводом пятого резистора, второй вывод которого подключен к аноду первого диода и вторым выводам второго и третьего резисторов, эмиттер третьего согласующего транзистора соединен с вторым выводом шестого резистора, база переключаюI щего транзистора соединена с выходом первого источника тока, эмиттер первого согласующего транзистора подключен к выходу второго источника тока

35 и является выходом формирователя.

2. Формирователь по п. 1, о т л ич а ю шийся тем, что в него введены второй диод, третий источник

4О тока и седьмой резистор, первый вывод которого соединен с базой первого согласующего транзистора, а второй вывод и катод второго диода подключены к выходу третьего источника тока, вход которого соединен с шиной питания, причем анод второго диода подключен к шине нулевого потенциала, 1244718

1244718

>сп Уразр Составитель Т.Зайцева

Редактор И.Касарда Техред Н.Бонкало Корректор А. Обручар

Заказ 3923/54 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4