Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам на полупроводниковых динамических элементах. Целью изобретения является повьшение быстродействия за счет совмещения такта записи скорректированной информации с тактом регенерации - считывания. Устройство содержит накопитель , формирователь корректирующих сигналов, блок коррекции, регистр регенерации, коммутаторы, счетчик, регистр адреса, дешифратор, блок сравнения, блок управления, дополнительный регистр адреса.1 з.п. ф-лы, 2 ил. 4ib Ч N) Од

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (50 4 . 0 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А 8TOPCKOMV СВИДЕТЕЛЬСТВУ

ЬМ-ы"

ГОСУДАРСТВЕННЫЙ HOMHTET СССР по делАм изОБРетений и ОткРытий (21) 3783155/24-24 (22) 21.08.84 (46) 15.07.86. Бюл. ¹ 26 (72) Н.А. Н)матов, В.И. Титов и Е.А. Воронин (53) 681.327.6(088.8) (56) Авторское свидетельство СССР ¹ 760194, кл. G II С 29/00.

Авторское свидетельство СССР № 1133625, кл. G 11 С 29/00, 1984. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМО

КОНТРОЛЕМ (57) Изобретение относится к вычис лительной технике, в частности к

„„SU „„1244726 А 1 запоминающим устройствам на полупроводниковых динамических элементах.

Целью изобретения является повышение быстродействия за счет совмещения такта записи скорректированной информации с тактом регенерации считывания. Устройство содержит накопитель, формирователь корректирующих сигналов, блок коррекции, регистр регенерации, коммутаторы, счетчик, регистр адреса, дешифратор, блок сравнения, блок управления, дополнительный регистр адреса.1 з.п. ф-лы, 2 ил.

44 726 l блока 3 коррекции через открытый элемент Р: 12.6 производится формирование импульса записи в дополнительный регистр 10 адреса и регистр 4 регенерации.

По концу такта фронтом синхроимпульса производится взведение триггера 12.3, закрытие элемента И 12,6 и установление счетного триггера !

О 12,2 в нулевое состояние.

Единичный уровень инверсного вьгхода счетнсго триггера 12.2 подключаЕсли на шине 18 в это время присутствует единичный уровень, то открывается элемент И 12.4. На выходах элементов ИЛИ 12.7 и 12.8 появляются единичные уровни, под воз.действием которых в накопителе производится запись информации. Если, при наличии сигнала обращения,.по шине 18 подается нулевой уровень, ro единичный уровень появляется только на выходе элемента ИЛИ 1?.8, под воздействием которого в накопителе происходит считывание информации.

В случае обнаружения ошибки в этом такте, управляющим сигна.пом от

1 12

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ), выполненным на полупроводниковых динамических элементах.

Цель изобретения — повышение быстродействия устройства за счет совмещения такта записи скоррек;тированной информации с тактом регенерациисчитывания.

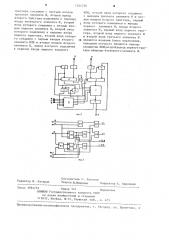

На фиг, 1 приведена структурная схема устройства; на фиг. 2 — схема блока управления.

Устройство содержит накопитель 1 на полупроводниковых элементах 1 памяти, формирователь 2 корректирующих сигналов, блок 3 коррекции, регистр

4 регенерации, второй коммутатор 5, счетчик б, регистр 7 адреса, первый коммутатор 8, дешифратор 9, дополнительный регистр 10 адреса, блок 11 сравнения, блок 12 управления, адресный вход 13, информационный вход

14, выход 15 устройства, управляющие

Входы 16-18 устройства.

Блок 12 управления содержит эле— менты И 12.1, 12.4, 12.5, 12.6, элементы ИЛИ 12.7 и 12.8, счетный триггер 12.2, динамический триггер 12.3.

Устройство работает следующим об— разом.

По шине 16 на третий вход блока управления поступает синхронизирующая серия. Сигнал обращения к памяти поступает по шине 17 на второй вход блока управления и совпадает по времени с импульсом синхронизирующей . серии.

Частота синхросерии в два раза больше частоты сигналов обращения.

При поступлении по шине 17 обращения, счетный триггер устанавпивается в нулевое состояние. ет на соответствующие входы памяти выходы регистра 7 адреса и формирова15 теля 2 коррек гирующих сигналов. Нулевой уровень инверсного выхода под— ключает на соответствующие входы памяти выходы счетчика 6 и регистра. 4 регенерапии, Фронтом этого сигнала

2() произвоцится добавление единицы к содержимому счетчика б.

Спустя цикл регенерации, при совпадении текущего адреса регенерации

25 с содержанием дополнительного регистра 10, r.å. того адреса, по которому в считанном слове обнаружена ошибка, открывается злемент 12.5 и Вместо такта регенерации-считывания информации производится запись скорректи рованной информации

В такте записи на информацоинную шину подается информация, подлежащая записи и память,, С адресной шины !3

35 на ре|истр 7 адреса поступает код адреса, По шине 17 на вход блока 12 управления поступает сигнал обращения, а по шине 18 — сигнал записи.

B формирователе ? корректирующих сигналов производится формирование дополнительных битов кода Хемминга, позголяющих обнаруживать 1 исправлять одиночные ошибки. С выхода формирова45 . ;епя 2 корректирующих сигналов информационные биты и биты кода Хемминга подаются íà BxoU, второго коммутатора 5. Единичный сигнал с третьего выхода блока 12 управления подключает через первый коммутатор 8 на адресчые входы памяти 1 и вход дешифратора 9 содержимое регистра 7 адреса. Через второй коммутатор 5 и информационные входы l памяти под ключаются выходы формирователя 2 корректирующих сигналов. Под действием управляющих сигналов с первого и второго выходов блока 12 управле1244726 ния в накопителе l производится запись информационных битов и дополнительных битов кода Хемминга.

В такте считывания с адресной шины 13 поступает код адреса, с шины

17 — сигнал обращения, с шины 18 сигнал считывания, Работа адресной .части аналогична циклу записи. ITop, воздействием управляющего сигнала с второго выхода блока 12 управления в накопителе 1 происходит считывание информации по адресу, принятому на регистр 7 адреса ° Считанные биты информации и биты кода Хемминга поступают в блок 3 коррекции информации, где, в случае обнаружения одиночной ошибки, происходит ее исправление и выдача на выходную информационную шину 13. Одновременно эта информация заносится на регистр 4 регенерации, если последний в это время не занят, Занесение скорректированной информации и адреса,по которому эта информация хранится в памяти, производится под воздействием сигнала, поступающего по четвертому управляющему выходу блока 12 управления.

В следующем такте блок 12 управления нулевым уровнем на третьем выходе подключает через первый коммутатор 8 на адресные входы накопителя I и входы дешифратора 9 содержимое счетчика 6. Под воздействием сигнала с второго выхода блока 12 управления происходит считывание из накопителя 1 информационных и контрольных битов в блок 3 коррекции. Если ранее в такте регенерации или в такте считывания по обращению была обнаружена ошибка, то при совпадении текущего адреса регенерации с адресом, записанным в дополнительо ном регистре 10, блок 11 сравнения выдает сигнал,по которому в этом такте происходит запись-регенерация скорректированной информации.

Если в процессе регенерации возникает несколько одиночных ошибок, .то устройство фиксирует первую ошибку, исправляет ее через цикл регенерации, а затем фиксирует следующую и т.д.

Формула изобретения

I. Запоминающее устройство с самоконтролем, содержащее. накопитель, регистр адреса, счетчик, дешифратор, первый коммутатор, формирователь корректирующих сигналов, второй коммутатор, блок коррекции, блок управления, причем один выход первого коммутатора соединен с первым входом нако-. пителя, другой выход — с входом де-. шифратора, выход которого подключен к второму входу накопителя, первый

10 вход первого коммутатора соединен с выходом регистра адреса, вход которого является адресным входом устройства, выход счетчика соединен с вторым входом первого коммутатора, Первый вход второго коммутатора соединен с выходом формирователя корректирующих сигналов, вход которого является информационным входом устройства, выход регистра регенерации соединен с вторым входом второго коммутатора, выход которого подключен к третьему входу накопителя, выход которого соединен с входом блока кор. рекции, один выход которого подключен к первому входу регистра регенерации и является информационным выходом устройства, первый, второй и третий входы блока управления являются управляющими вхоДами устройства, четвертый вход блока управления соединен с другим выходом блока коррекции, первый и второй выходы блока управления подключены к третьему и четвертому входам накопителя, третий выход блока управления подключен

35 к третьим входам коммутаторов и входу счетчика, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены

40 дополнитепьный регистр адреса и блок сравнения, причем выход счетчика подключен к первым входам блока сравнения и дополнительного регистра адреса, выход которого соединен с

45 вторым входом блока сравнения, выход которого подключен к пятому входу блока управления, четвертый выход которого соединен с вторым входом дополнительного регистра адреса и вторым входом регистра регенерации.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок управления содержит первый и второй триггеры, элементы И, элементы ИЛИ, при55.чем первый выход первого .триггера соединен с первым входом третьего элемента И и с вторым входом второго ( элемента ИЛИ, первый выход второго

124472б

12.8

Составитель О. Кулаков

Техред H.Попови-. Корректор Е. Сирохман

Редактор И. Касарда

Заказ 3924/55 . Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская.наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 триггера соединен с третьим входом третьего элемента И, второй выход второго триггера подключен к первому входу четвертого элемента И, второй вход которого соединен с вторым входом первого элемента И, второй вход которого подключен к первому входу первого триггера, второй вход которого соединен с первым входом второго 10 элемента ИЛИ и вторым входом второго элемента И, выход которого подключен к первому входу первого элемента

ИЛИ, второй вход которого соединен с выходом третьего элемента И и вторым входом второго триггера, первый вход которого подключен к выходу первого элемента И, входы второго элемента И, первый вход первого триггера, второй вход первого элемента И и второй вход. третьего элемента И являются входами блока управления, выходами которого являются выходы элементов ИЛИ,второйвыход первого триггера ивыходы четвертого элемента И.