Устройство для контроля полупроводниковой оперативной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть, использовано для функционального контроля микросхем оперативных запоминающих устройств. Целью изобретения является повышение достоверности контроля. Устройство содержит генератор тактовых сигналов, счетчик адреса, счетчик циклов, счетчик подциклов, блоки сравнения, блок пускаостанова, элемент ИЛИ-НЕ и элементы НЕРАВНОЗНАЧНОСТЬ. В устройстве реализуются четыре подцикла контроля, образующие полный цикл: запись тестовой последовательности в память, ее считывание из памяти, запись инвертированной тестовой последовательности в память, считывание последней из памяти, 3 ил. с (Л С Н fe 4;а 4 1С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (so 4 G 11 С 29/00

® гор,".. 1- 4М

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМ У СВИДЕТЕЛЬСТВУ щлюткы

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3832291/24-24 (22) 25.12.84 (46) 15.07.86. Бюл. Ф 26 (72) Ю.А. Марков и С.Н. Семенов (53) 681.327(088.8) (56) Авторское свидетельство СССР

N 622174, кл. G II С 29/00, 1978.

Авторское свидетельство СССР

N 407398, кл. G 1! С 29/00, 1972. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОЛУПРОВОДНИКОВОЙ ОПЕРАТИВНОЙ ПА11ЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для функционального контроля микросхем оперативных запоми„„Я0„„1244727 А 1 нающих устройств. Целью изобретения является повышение достоверности контроля. Устройство содержит генератор тактовых сигналов, счетчик адреса, счетчик циклов, счетчик под циклов, блоки сравнения, блок пускаостанова, элемент ИЛИ-НЕ и элементы

НЕРАВНОЗНАЧНОСТЬ. В устройстве реализуются четыре подцикла контроля, образующие полный цикл: запись тестовой последовательности в память, ее считывание из памяти, запись инвертированной тестовой последовательности в память, считывание последней из памяти. 3 ил.

1244727

Изобретение относится к вычисли- тельной технике и может быть исполь- зовано для функционального контроля микросхем оперативных запоминающих устройств (ОЗУ), Цель изобретения — повышение достоверности контроля.

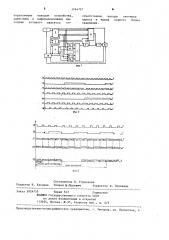

На фиг. представлена функциональная схема устройства; на фиг. 2 и 3 — диаграммы, поясняющие работу устройства для контроля, например, двухадресной оперативной памяти.

Устройство содержит генератор 1 тактовых сигналов, счетчик 2 адреса, счетчик 3 подциклов, счетчик 4 циклов, элемент ИЛИ-НЕ 5, первый 6 и второй 7 блоки сравнения, блок 8 индикации, элементы 9 -9„, НЕРАВНОЗНАЧНОСТЬ и блок 10 пуска — останова 20 (il — разрядность счетчика 2) . На фиг. 1 показана проверяемая память

11; на фиг. 2 — диаграммы сигналов

12 на выходе младшего разряца счетчика 2, сигналов 13 на выходе младшего разряда счетчика 4, сигналов 14 на выходе первого элемента 9 НЕРАВНОЗНАЧ-: !

НОСТЬ, сигналов - !э па выходе старшего разряда счетчика 2, сигналов 16 на выходе старшего разряда 3G счетчика 4 циклов, сигналов 17 на выходе второго элемента 9 НЕРАВНОЗНАЧНОСТЬ, сигналов 18 на втором входе блока 6 сравнения; на фиг. 3 диаграммы сигналов 19 и 20 соответственно на втором и первом входах блока б сравнения, тестовая последовательность сигналов 21 записи на выходе блока 6 сравнения, диаграммы сигналон 22 с выхода младшего разряда 0 счетчика 3, диаграмма 23 полного цикла контроля; на фиг,. 3 и 4 обозна.— чены оси времени t, Устройство работает следующим образом.

При работе устройства проверяемая оперативная полупроводниковая память

ll (фиг. 1) запоминает последовательно вводимую информацию н порядке ее поступления и последовательно выдает информацию в порядке, определяемом очередностью записи этой информации.

Устройство реализует четыре подцикла контроля, образующие малый цикл контроля — запись тестовой последовательности в память; считыва.ние тестовой последовательности> запись инвертированной тестовой последовательности в память; считывание инвертированной тестовой последовательности из памяти.

Перед началом рабаты счетчики 2-4 находятся в нупевом состоянии. По команде "Пуск" блок 10 запускает генератор 1, который начинает выдавать тактовые импульсы на вход блока 8 и счетный вход счетчика 2 С установкой в "1" счетчика 2 начинается цикл контроля тестом. Все счетчики 2-4 работают в режиме непрерывного пересчета.

Счетчик 2 формирует код адреса, по которому производится обращение к ячейке проверяемой памяти, который поступает на первые входы соответствующих элементон 9 НЕРАВНОЗНАЧНОСТЬ, на нторые входы которых поступает код с выхода счетчика 4. Переполнение счетчика 2 означает окончание однаг о подцикла .

Импульсы переполнения счетчика 2 подсчитываются счетчиком 3, импульсы переполнения которого подсчитываются счетчиком 4. Переполнение счетчика 4 означает прохождение одного большого цикла контроля.

Младший разряд счетчика 3 формирует код, обеспечивающий реализацию рег<имов "ЗАПИСЬ" и "СЧИТЫВАНИЕ" ("0"

"ЗАПИСЬ", "1" — "СЧИТЫВАНИЕ" ) информации,цля контролируемой памяти.

В режимах "ЗАПИСЬ" и "СЧИТЫВАНИЕ" счетчик 2 формирует идентичные последовательности адресов. Блок б формирует тестовую последовательность импульсов, поступающую как на информационный вход контролируемой памяти 11 для записи, так и на второй вход блока, на первый вход которого по,цается считываемая из контролируемой памяти информация. Блок 7 слжит для поразрядного сравнения данных, считанных из проверяемой памяти по заданным последовательностям адресов, с данными, которые были записаны по тем же адресам, Обнаружение несовпадения кодов, записанных и считываемых из памяти, свидетельствует о наличии неисправности (например, наличие постоянной "1" или "О"), При сонпадении на протяжении всего цикла контроля записанной и считанной информации осуществляется следующий цикл записи и считывания.

Такие запись и считывание со сравне1244727 нием выявляют взаимное влияние между ячейками контролируемой памяти. Кроме того, возможно выявление адресных цепей, находящихся в состоянии постоянного "0" или "1", и короткозамкнутых адресных цепей. При неисправных цепях в отдельных ячейках данные будут записаны в другие ячейки памяти, что выявляется в последующем цикле считывания.

По результатам сравнения в блоке

7 записанной и считанной информации формируется сигнал "ГОДЕН-БРАК", который с выхода блока 7 поступает на блок 8, где фиксируется отказ или сбой и формируется сигнал "ОСТАНОВА", по которому устройство прекращает формирование тестовой последовательности.

Таким образом, данное устройство производит тестовый контроль взаимосвязей между адресными цепями и разрядами ячеек памяти модифицированным .динамическим тестом типа "бегущая I" или "0".

Например, во время первого малого цикла {фиг. 3-21) в первом подцикле в первый адрес записывается l", а во все остальные адреса †. "0". Во время второго подцикла записанная информация считывается. Во время третьего подцикла происходит инверсия записываемой информации, т.е. в первый адрес записывается 0", а в остальные адреса — "1 . В четвертом подцикле происходит считывание записанной информации.

Во втором малом цикле в его первом подцикле записывается по второму адресу "1, а по остальным — 0 .

Затем во втором подцикле считывается информация. В третьим подцикле во второй адрес записывается О, а в остальные адреса — "1".

В третьем малом цикле в его первом подцикле происходит запись"1" в третий адрес, а в остальные — "0".

В третьем подцикле записывается в третий адрес "0", а в остальные "1", Во втором и четвертом подциклах записанная информация считывается.

В четвертом малом цикле в первом подцикле происходит запись "1" в четвертый адрес, а в остальные — "0".

В третьем подцикле в четвертый адрес записывается "0, а в остальные

"l". По окончании четвертого подцикла заканчивается полный цикл контроля.

Таким образом, в данном частном случае цикл контроля включает четыре малых цикла, причем в первых двух подциклах происходит проверка динамическим тестом типа "бегущая !", а в третьих и четвертых подциклах имеет место тест "бегущий О" 1фиг. Э-21. и 22);

10

Формула изобретения

Устройство для контроля полупроводниковой оперативной памяти, содержащее счетчик адреса, счетчик циклов, первый и второй блоки сравнения и блок пуска-останова, первыйвыход которого подключен к входу сброса счетчика адреса, причем первый вход втоf5

20 рого блока сравнения является входом. устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены генератор тактовых сигналов, счетчик подциклов, элементы НЕРАВНОЗНАЧНОСТЬ, блок индикации и элемент ИЛИ-НЕ, входы которого соединены с выходами элементов НЕРАВНОЗНАЧНОСТЬ, а выход под. ключен к первому входу первого блока

30 сравнения, второй вход которого соединен с выходом старшего разряда счетчика подциклов, вход запуска .которого подключен,к выходу переполнения счетчика адреса, а вход сброса

35 соединен с первым выходом блока пуска-останова и входом сброса счетчика циклов, вход запуска которого подключен к выходу переполнения счетчи-. ка подциклов, первые входы элементов

НЕРАВНОЗНАЧНОСТЬ соединены с выходами счетчика адреса, а вторые входыс выходами счетчика циклов, выход переполнения которого подключен к первому входу блока пуска-останова, пер45 вый выход генератора тактовых сиг- налов соединен с входом запуска счетчика адреса, а второй вьгход — с первым входом блока индикации, второй вход и выход которого подключены к второму выходу и ко второму входу блока пуска-останова, третий выход которого соединен с входом генератора тактовых сигналов, третий вход

:блока индикации подключен к выходу

55 второго блока сравнения, второй вход которого соединен с выходом первого блока сравнения, выход младшего разряца счетчика подциклов является

1244727

Фиг 2

zt сРиг. 3

Составитель В, Гордонова

Редактор И. Касарда Техред И.Попович Корректор Е. Сирохман

Заказ 3924/55 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. .Ужгород, ул. Проектная, .4 управляющим выходом устройства, адресными и информационными выходами, которого является со ответственно выходы счетчика адреса и выход первого блока сравнения.