Цифровой фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах цифровой обработки информации. Повьппается качество фильтрации зашумпенных сигналов. Устройство осуществляет нелинейную фильтрацию входного сигнала согласно уравнению Уц -.и-и .)5 В частности ранговую фильтрацию. Двоичный код коэф. усиления PI записывается в блок 9 памяти коэф. п разрядныё двоичные коды вес. коэф. е(. (i I, п) записываются в п-разрядный кольцевой сдвиговый регистр (КСР) 5. Содержание 1-го разряда КС 5 равно значению (, m-разрядные отсчеты входного сигнала поступают на блок памяти (ВП) 2. По тактовым импульсам формирователя 1 тактовых импульсов коды отсчетов сигнала Х|. ,...,х поразрядно параллельно поступают с БП 2 на блок 3 определения последовательности экстремумом . В этом блоке определяются значения всех, п порядковых статистик R; :ц ) последовательности отсчетов. Порядковые статистики определяются путем последовательного вычисления максимумов. Элемент И 4 осуществляет операцию умножения кода 1-й порядковой статистики на вес, 1C (Л Фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) Н 03 Н 706

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А8ТОРСКОМУ СВИДЕТЕЛЬСТВУ л

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3843964/24-09 (22) 16.01.85 (46) 15.07 ° 86. Бюл . № 26 (71) Физико-механический институт им. Г. В. Карпенко (72) В. В. Грицык, А. Ю, Луцык и P. M. Паленичка (53) 621.396.6(088.8) (56) 1. Авторское свидетельство СССР № 586459, кл. G 06 F 15/34, 1977, 2. Авторское свидетельство СССР ,№ 758166, кл. G 06 F 15/31, 1980.

3. Авторское свидетельство СССР

¹ 966690, кл. G 06 F 7/02,,1981, (54) ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах цифровой обработки информации. Повышается качество фильтрации зашумленных сигналов. Устройство осуществляет нелинейную фильтрацию входного сигn tl нала согласно уравнению у„= р к; R, 1 1 (х „„,,,..., "-, ), в частности ранговую фильтрацию. Двоичный код коэф. усиления записывается в блок 9 памяти коэф. п-разрядные двоичные коды вес. коэф. К; (i = I, n) записываются в и-разрядный кольцевой сдвиговый регистр (КСР) 5. Содержание i-ro разряда KCP 5 равно значению „., m-разрядные отсчеты входного сигнала по- . ступают на блок памяти (БП) 2. По тактовым импульсам формирователя 1 тактовых импульсов коды отсчетов сигнала х,„, . ..х поразрядно параллельно поступаю с БП 2 на блок 3 определения последовательности экстремумом. В этом блоке определяются значения всех п порядковых статистик

tl

1 (х „,..., х„) последовательности отсчетов. Порядковые статистики определяются путем последовательного вычисления максимумов. Злемент И 4 осуществляет операцию умножения кода

i-й порядковой статистики на вес.! 244786 к у = — „ х

"к и — к-1 1

1 .- 1

30 коэф. « ., »o<.тупающий < К(:Р 5. (;игнал < элемента И 4 через преобразОватель 6 последовательного кода в параллельный поступает на накапливающий <.умматор 7. После II öèêëîâ ðàИзобретение относится к радиотехнике и вычислительной технике и может быть использовано в системах цифровой обработки информации.

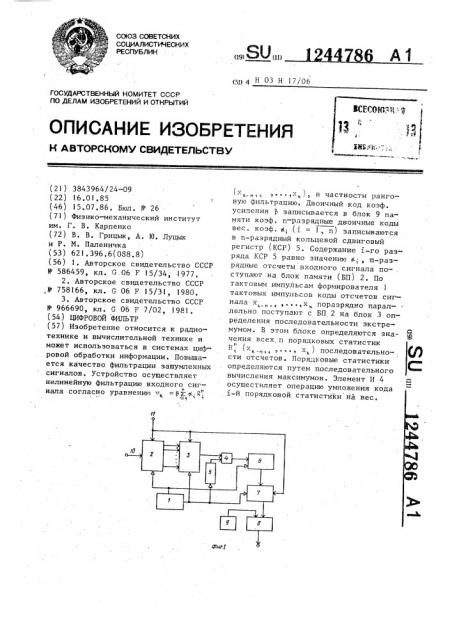

Цель изобретения — повышение качества фильтрации зашумленных сигналов, На фиг., 1 приведена структурная электрическая схема цифрового фильтра, на фиг. 2 и 3 — структурные электрические схемы блока памяти и блока определения последовательности экстремумов сигнала соответственно, входящих в состав цифрового фильтра.

Цифровой фильтр содержит формирователь 1 тактовых импульсов,, блок 2 памяти, блок 3 определения последовательности экстремумов сигнала, элемент И 4, кольцевой сдвиговый регистр

5, преобразователь 6 последовательного кода в параллельный, накапливающий сумматор 7, умножитель 8, блок 9 памяти коэффициента, информационный вход 10 цифрового фильтра и управляющий вход 11 цифрового фильтра.

Блок 2 памяти содержит и регистров 12 (где n — порядок фильтра), и мультиплексоров 13, счетчик 14, информационный вход 15 установочный вход 16, вход 17 синхронизации и выходы 18.

Блок 3 определения последовательности экстремумов сигнала содержит и элементов И 19, и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 21, и триггеров 22 первой группы, п триггеров 23 второй группы, селектор 24, п информационных входов 25, установочный вход 26 и вход 27 синхронизации.

Цифровой фильтр работает следующим образом.

Предлагаемое устройство осуществляет в общем случае нелинейную цифровую фильтрацию входного сигнала. согласно следующему уравнению. боты цифрового фильтра двоичный код с накапливающего сумматора 7 поступает на умножитель 8, где происходит умножение на коэф, усиления з . II ф-Ilbl 3 HJI .

<1 где Б,. (х„„,„,..., х„) — -ая поряд5 ковая статистика текущих отсчетов (выборок) входного сигнала х х„; у, — значение К-го отсчета сигна

h ла на выходе фильтра; ; — весовой коэффициент, имеющий значение 0 или

1; 1- — коэффициент усиления. Когда

1 и только один коэффициент <к.

1, то предлагаемый цифровой фильтр осуществляет ранговую фильтрацию входного сигнала. Например, когда (и+1)/2, где п — нечетное, то г<редлагаемый цифровой фильтр осуществляет медианную фильтрацию сигнала, которая является очень эффективной для сглаживания импульсного шума. Ne20 диана является порядковой статистикой с номером (и+1)/2 при нечетном и.

Еслй пОлОжить, что <к1 1, < 1 1, и и = 1/и, то получаем обычный сглаживающий фильтр, который реализует

25 операцию скользящего усреднения IIo формуле

Перед началом работы цифрового фильтра двоичный код коэффициента усиления записывается в блок 9 памяти коэффициента (регистр), à и-разрядный двоичный код всех весовых коэффициентов 1,, i 1, и запи< сывается в,п-разрядный кольцевой сдвиговый регистр 5, при этом содержимое i-го разряда сдвигового регистра 5 равно значению <<;.

Отсчеты входного сигнала, каждый из которых имеет m разрядов, последовательно поступают на информационный вход 5 блока 2 памЯти, оДновРеменно

1244786

5 !

О

20 на установочный вход 16 блока памяти

2 с управляющего входа 11 фильтра поступает импульс записи нового отсчета и сдвига информации, записанной в и регистрах I 2 блока памяти.

В n m-разрядных регистрах 12 временно хранятся коды и последовательных отсчетов сигнала х„ „,„,..., х„. Блок

2 памяти также содержит п мультиплексоров 18 и счетчик 14 с коэффициентом пересчета равным ш, С помощью этих схем осуществляется последовательное поразрядное считывание из регистров

12 кодов отсчетов х х„,, наК-И+1 чиная со старшего разряда. Счетный вход счетчика 14 соединен с тактовым выходом формирователя 1, который является выходом генератора тактовых импульсов. Таким образом, с каждым тактом работы цифрового фильтра на выходах блока 2 памяти параллельно образуются сигналы, соответствующие значениям определенного разряда (с помощью счетчика 14) всех регистров 12.

Коды отсчетов сигнала х х поразрядно параллельно поступают к на соответствующие информационные входы блока 3. Перед .поступлением первых разрядов всех и отсчетов из блока 2 памяти, все и триггеров 23 второй группы устанавливаются в единичное состояние при поступлении импульса с управляющего входа 11 цифрового фильтра. Блок 3 последовательно поразрядно вычисляет значения всех

tl порядковых статистик последователь. ности отсчетов, которые хранятся в блоке 2 памяти. Порядковые статистики вычисляются путем последовательного вычисления максимумов соответствующих последовательностей отсчетов сигнала (3). С помощью элементов И 19, ИСКЛЮЧАЮЩЕЕ ИЛИ 21, триггеров 22 первой группы, и-входового элементаИЛИ 20 поразрядно вычисляется максимальное значение входной последовательности кодов. На выходе элемента

ИЛИ 20 появляется поразрядно m-разрядный код максимального значения последовательности x„ „„,...., х„. т,е. код первой порядковой статисти- ки R", (х„„,„,..., х,). В результате этого после m тактов работы устройства все триггеры 22 первой группы устанавливаются в нулевое состояние, кроме триггера (триггеров), номер которого соответствует максимальному отсчету.

Селектор 24 реализует следующую функцию. Если i-й триггер 22 первой группы находится в единичном состоянии, а все триггеры 22 первой группы с номерами, меньшими х, находятся в нулевом состоянии, то на i-м выходе селектора 24 появляется сигнал

"1", а на всех остальных (п-1) выходах селектора — "0". Такой селектор может быть реализован с помощью п параллельно действующих элементов И, причем К-й элемент И имеет (К+1) входов. Входы К-го элемента И соединены соответственно с инверсными выходами триггеров 22 первой группы с номерами, меньшими К, с прямыми выходами

К вЂ” го триггера 22 первой группы и с тактовым входом селектора

24.

После вычисления всех m разрядов максимума на вход 27 синхронизации блока 3 поступает импульс синхрониз ации с выхода управления формирователя

1. Выход управления формирователя 1 является выходом делителя частоты, вход которого соединен с выходом генератора тактовых импульсов. Частота импульсов на этом выходе формирователя 1 в m раз меньше частоты на тактовом выходе. При поступлении импульса на вход 27 синхронизации блока 3 определения последовательности экстремумов сигнала осушествляется установка в единичное состояние триггеров

22 первой группы и запись лнформации с выходов селектора 24 в триггеры 23 второй группы. При поступлении импульса синхронизации на тактовый вход селектора 24 на его к-м выходе будет сигнал "1", если К-й триггер

22 находится в единичном состоянии и все триггеры 22 с номерами, меньшими

К, находятся в нулевом состоянии. В результате связи триггеров 23 с входами элементов И 19 код определенного ранее максимума не учитывается при определении максимума в следующем цикле работы цифрового фильтра. Таким образом, во втором цикле работы цифрового фильтра на выходе элемента

ИЛИ 20 появляется поразрядно код второй порядковой статистики R (õ„ „,„, х„ ). В и-м цикле работы цифрового фильтра на выходе элемента

ИЛИ 20, т.е. на выходе блока 3, появляется код числа R (х„„,,,...,.х„), т.е. минимум последовательности отсчетов сигнала х„ „,„,..., х

В 244 7 (С выхода блока 3 кад 1-й порядкаН / най счатистики П (х ь ° в ° х ) поразрядно (начиная са старшего разряда) поступает на первый нхад элемента И 4, На второй вход элемента

И 4 с выхода кольцевого сднигового регистра 5 поступает одноразрядный кад коэффициента к; . Элемент И 4 реализует операцию умножения и ;Р, (х„ „,,,...., Х,.). Последовательный коц на выходе элемента И 4 преобразуется н соответствующий .параллельный кад на выходе преобразователя 6, который может быть реализован и виде сдвигаваго регистра, Код произведения 6;II;(x„ „,, x ). поступает на информационный вход накапливающего сумматора 7. При постуI плении очередного отсчета на информаЦионный вход 10 Цифрового фильтра им пульс управления с управляюшего входа 11 устанавливает накапливающий сумматор 7 в нулевое состояние (происходит сброс сумматора).

Таким образом, после п циклов работы цифрового фильтра в накапливающем сумматоре 7 сформируется двоичный ь код числа у = + oc 1 .. Умнажитель е К < 1

8 реализует операцию умножения кода числа на выходе наканливающега сумматора 7 на кад содержимого блока 9 памяти коэффициента, т.е. на двоичный код значения коэффициента усиления

Эа счет возможности осуществления ранганай фильтрации сигналов предлагаемый цифровой фильтр позволяет повысить качество фильтрации зашумленных сигналон по сравнению с известными цифровыми фильтрами, Например, за счет возможности реализации медиан4О ной фильтрации сигналов данный цифровой фильтр позволяет хорошо сглацить импульсный шум и при этом не исказить значительно полезный сигналС помощью предлагаемого цифрового фильтРа можно осуществлять также сглаживание шумов других видов, например сглаживание белого шума путем выполнения скользящего усреднения сигнала.

Формула изобретения

1. Цифровой фильтр, содержащий блок памяти, элемент И, накапливающий сумматор, блок. памяти коэффициентов, формирователь тактовых импульсов и умнажитель, первый вход которого соединен с выходом блока памяти каэффи86 б циентав, а т л и ч а ю шийся тем, что, с целью повьппения точности фильтрации зашумленных сигналов, введены блок; определения последовательности экстремумов сигнала, кольцевой сдниговый регистр и преобразователь последовательного кода в параллельный, выходы блока памяти соединены с соответствующими информационными входами блока определения последовательности экстремуман сигнала, выход которого подключен к первому входу элемента И, второй вход которого соединен с выходам кольценого сдвигового регистра, выход элемента И подключен к:информационному входу преобразователя последовательного кода в параллельный код, выход которого соединен с входом накаплинающего сумматора, второй вход умнажителя подключен к выходу накапливающего сумматора, выход которого является выхо,цом цифрового фильтра, тактовый выход формирователя тактовых импульсан саецинен с входами синхронизации преобразователя кода и блока памяти, а выход управлений подключен к входам синхронизации накапливающего сумматора, кольцевого сдвигового регистра и блока определения последовательности экстремумов сигнала, установочные входы накапливающего сумматора, блока определения последовательности экстремумов сигнала и блока памяти объединены между собой и являются управляющим входом цифрового фильтра, а информационный вход блока памяти является информационным входом цифрового фильтра.

2 Фильтр по п. 1, о т л и ч а— ю шийся тем, что блок определения последовательности экстремумов сигнала содержит и элементов И, где — 1, 2р 3,. ° . — порядок цифранога фильтра, и элементов ИСКЛЮЧАЮЩЕЕ HJIH, п триггеров первой группы, п триггеров второй группы, селектор и элемент

ИЛИ,, входы которого соединены с выходами сп элементов И, первые входы которых являются соответствующими информационными входами блока определения последовательности экстремумов сигнала, а вторые и третьи входы и элементов И соединены соответственно с выходами п триггеров первой и второй групп, выходы и элементов И подключены к первым входам элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с выходом элемента ИЛИ явт

1244

is

Составитель А. Осипович

Редактор М, Товтин Техред Н.Бонкало Корректор О. Луговая

Заказ 3927/58

Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ляющимся выходом блока определения

-.последовательности экстремумов сигнала, выходы п элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ подключены к входам установки в

"Оп триггеров первой группы, выход

i-ro из которых (где 5. = 1, n), соединен с i-м входом селектора, i-й вы ход которого подключен к входу установки в "О" i-ro триггера второй

786 8 группы, причем входы установки в "1" и триггеров второй группы объединены между собой и являются установочным входом, а тактовый вход селектора и входы установки в "1" триггеров первой группы объединены между собой и являются входом синхронизации блока определения последовательности экст-. ремумов сигнала.