Устройство для отображения информации

Иллюстрации

Показать всеРеферат

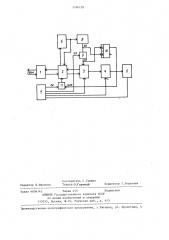

Изобретение относится к области вычислительной техники и может быть использовано при проектировании устройства отображения информации. Цель изобретения - повышение быстродействия устройства, которая достигается введением первого и второго элементов И, триггера, дешифратора и функциональных связей, что обеспечивает вьтолнение микрокоманд, не требующих обращения процессора к первому блоку памяти, независимо от развертки индикатора , и только микрокоманды, требующие обращения к первому блоку памяти , вьшолняются во время обратного хода развертки индикатора. 1 ил. i (Л N9 42ь to 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU 124 128 и11 4 С 09 С 1/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АSTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 356 1580/24-24 (22) 10.01.83 (46) 23.07.86. Бюп. В 27 (71) Ордена Ленина институт кибернетики им. В.М. Глушкова (72) К.Н,Данильченко, А.А.Свергин, В.С.Смирнов и В.Б.Солдатов (53) 681 327.11 (088.8) (56) Телевизионные методы и устройства отображения информации./ Под ред. М.И.Кривошеева. - М.: Советское радио, 1975, с.8-12.

Патент США У 3675208, кл. 340-172.5, опублик, 1972. (54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано при проектировании устройства отображения информации. Цель изобретения — повышение быстродействия устройства, которая достигается введением первого и второго элементов И, триггера, дешифратора и функциональных связей, что обеспечивает выполнение микрокоманд, не требующих обращения процессора к первому блоку памяти, независимо от развертки индикатора, и только микрокоманды, требующие обращения к первому блоку па- Я мяти, выполняются во время обратного хода развертки индикатора, 1 ил. >чн! >т),:Ыт Ь НС (O- Ii— .,-.>с-,.;аа„а)-гЦ-; -, стРО.-(СТВ.,>;)-,! «=н)- ()ы! !

>! — 5s)ак 1 cапря,— с; и ?,::.->,) нь(>э 6.)1Ок 3

: тт,>,! > О) ов, а .) О: O>:" :а Г>ЯМЯ И 9 CHH— -p= ОT: .,—,ет;(;:тфрагар 8, первый

О !> ",! !" r т) 1 О (этopoH т! ! ». . TI >(Я: > а Ч P )-1 для ..":, ...: — „. Н,)апь(ы-и ме)кду 3В1! .,-. -:.")o.r .,: о.(ержит pe

--T -; — —;; — .. —.. -сведачи инрарГ. ), - .:.: ".. ред >азначен для

>!" - : --. -.-,, „-: яс-.ç"ykij(ей в .-: —. -.О(С Салр>т КЕ: ИЕ С ЭВМ а (я- пт (. «с) .Т..псрокамандам

:..а ввт. а-) =:)! блоке > ; памяти ,-)-.; — П -ъ „тю)! Ь) 1 1 —; ) еп.-...-, (явен ((,ля обмена !

)т(>т(> Г:-;>;: Iir.. ." (.-.Of> С -1М .:.> Ia яц») ЕС Oтоб

p=";êj j- я, - poör- ссорам ? -,-(о ко (aa)3aM

:эт и: — ":;:- (.."-: .1(;f ч:-.: .. Ярь)вания регене>)а >).Я) г: Э (З.Г1,.-, ((:, =; такжЕ ДЛЯ

;э."-;; —,;.;a трт=: це

"И:-,:-.,:.О> С ...; .Я . „-; В::; ЕОСИтгНЯЛ

З(Ь1; »"Э :. Я) . Н r.. >.",I j, К - I O I) .) - ИНД)1 К:> тар .; ) i., — -; (с =,,;)! . ;. зебра.зспза-(е>)! E>п.!. -,,->,=::=,,: I)!i . = !T сcnHg> а! эа з.!

:.1Or. > — =,r>l >:.,, 1 С (j, -; I; —, C )>3 g;ЯТ ОРЯ в >эт;,п.с,тс = - —,,-!;.:;к .-Н> -"1 О;т(-тэжи,, Э.П )

pr-. >- >>,,;), с > г .— >э >; !те!! !(1)oa

I: ме и; ° ; .:, .- >) тab:-тлиирс,--;;-: -;— :«! »:— ::= --. . - >:, . ((телa)f

ЧЯC . > Ы -,,) I >i> Ii>ав:! > :.Г и 11".>»- ">ЛЬ-.ОВ ! )(сс . - г >I/>,, » "IL я,"> . -. > Ор .. Bp! д.=:Яз кт) с. - .тя - вь, =!"...т T";г я -:имва)та На г е/

3 rr : В СаатвагСтВИИ С ядра .: а ",-.:p;-;,;:,a(> . "т синхрогенерага>-,:: ":.-.р= .то;: .:.:H i>aoëo)3 прзц— с„п.- . -c ". :., . : — >>, . О -, Ьпака 3 —:=."Er! -н, ("."= ((,,. 1Я j-, ЫЧ >ЬПЕНттн > В (КРОК ОМЯ НД ТРС буюк!их О()ра)пения T(poцессора ? к = -аку = .-тамяти и формирования СИгнала Обраще ))E к памя ги (ОП) и выдачи ега; злементы 9 и 10. Э (eMe)(v И 9 гре>T).а.-;ía÷oí дпя формирования сигнаТТ8 Пт) ЕРЬИэа НИЯ P Bl BHCPBUHH ПГ ) ПО ."::--(:гна::.-;, ОП, пас тупающему от де(!п фрагора 8. и сигналу обратного хада раaâåpòêè инцикатара (ОХ), поступающему с>f си(.хрогенератора 7 и выдачи его в блок 3 памяти 3 и триггер 10.

Тр))гге» 10 (R!9-триггер) предназначен цл-. формирования сиг )ала блокировки п>роцессора (БЛ)С) по сигналам ОП и

ГР, Элемент И I 1 предназ начен для фсрмирс вяния сигналов синхронизации процесс.ора 2 по синхраимпупьсям (СИ), IIocтуп;.ю ((H(от синхрогенератара 7, сигналу Э!1К,. поступающему от триг сра О, Усгройство работaeт следующим оаРЯ .! О "(, Инф(>р Ta)(HH, хранящаяся в блоке 3 памят : > через генератор А cHMBoëo)3 псступае" з индикатор 5 для отображения,бинхрагенератор 7 выдает на индикатор сигналы кадровой и строчнс - -, ci(E)xpo÷Haaö(HH, га генератор 4

СИМВО)1(>В Ка С ГРОКИ И КОЛОНКИ В Мат рице разложения символов, и в блок 3 пaM)=.j-. - а:,:рac отображения, Этим абеспе-(H)3a.ется регенерация отображаемой информации на индикаторе 5 с тясTатсй кадровой развертки в соотзе стг>ь и . кодами с)(.!волoH. храня> (, ) 1J я. с. =. в бл О к е 3 пЯмя ти си ф0\змой с)=.мва.:с в „задаваемой генера гором смыва :r.в. 11ри этом за период кядро)3Cй Ра ЗВЕРТКИ -(ОСЛЕЦОВате 11>НО ÎПРаьтиваю.r.;ся T)c е ячейки блока 3 памяти, .<ажцая из которых соотг етствует оп—

p:=;> Å„-(Ет НОМУ -,Ía-"TÎMÅÑòó На ЭКраНЕ и -!»>и)сс! ора э, !1ереклю-!ение. блока 3

П.-;Ятт- И.-: РЕжн()..! РЕГЕНЕРЯ r))H В РЕжим Об. ет(а инфармациеи с процессором 2 прои-;водится сигналом прерывания рег- -(ера)HH IIP от злемента И 9.

Б 3 Гаемя Ос>меня информяцией ме)кцу

>войства--.! и ЭВМ блок 1 сопряжения (-. Нимает Оj ЭБМ команды H в соотв .сгвт-:и с этими командами принимает тз аз — 1 H !r:=редяет процессору 2 или

НОИНHMaåò ат процессора 2 и передает в ЭВМ инфо=-ацию., участвующую в обме-;c.. (1о команде, поступающей из бло.ка 1 сопряжения с ЗВМ, про>;ессор 2 вычис.гтяет:=> выдает начальный адрес

cooTBе;ствующей микропрогряммь: в

1246

10 блок 6 памяти, получает от блока 6 памяти код микрокоманды и начинает обработку информации в соответствии с этой микропрограммой (вычисление последующего адреса микрокоманды для передачи его в блок 6 памяти, вычис— ление адреса отображения информации для передачи его в блок 9 памяти, прием информации от блока 1 сопряже— ния с 3BN или блока 3 памяти, преобразования принятой информации, пе— редача результатов преобразования в блок 1 сопряжения или блок 3 памяти) .

Адрес микрокоманды изменяется сигналом синхронизации от элемента И 11. 1

При поступлении микрокоманды, требующей обращения процессора 2 к блоку 3 памяти, дешифратор 8 формирует сигнал ОП, который устанавливает триггер 10 в нулевое состояние. Вырабо- 2п танный триггером сигнал БЛК блокирует прохождение синхроимпульса СИ через элемент И 11 на процессор 2,прерывая дальнейшее выполнение микропрограммы. Такое состояние будет со- 2s храняться до прихода от синхрогенератора 7 сигнала обратного хода развертки индикатора (ОХ). По сигналу

ОХ элемент И 9 формирует сигнал прерывания регенерации ПР, которым разрешается обмен информацией между процессором 2 и блоком 3 памяти и устанавливается B единичное состояние триггер 10. При этом снимается блокировка с элемента И 11, разрешает—

35 ся формирование сигналов синхронизации процессора 2, дальнейшее выполнение микропрограммы и переключение блока 3 памяти в режим регенерации.

Таким образом обеспечивается выполнение микрокоманд, не требующих обращения процессора 2 к блоку 3 памяти, независимо от развертки индикато128 4 ра, и только микрокоманды, требующие обращения к блоку 3 памяти, выполняются во время обратного хода развертки индикатора.

Формула изобретения

Устройство для отображения информации, содержащее блок сопряжения, первый вход-выход которого является выходом-входом устройства, второй вход-выход которого соединен с первым выходом-входом процессора, второй вход-выход которого подключен к выходу-входу первого блока памяти, вход и первый выходы прецессора соединены соответственно с выходом и входом второго блока памяти, выход первого блока памяти соединен с первым вхо- . дом генератора символов, второй вход которого соединен с первым выходом синхрогенератора, выход генератора символов подключен к блоку индикации, соединенному с вторым выходом синхрогенератора, третий выход которого подключен к первому входу первого блока памяти, о т л и ч а ю щ е е— с я тем, что, с целью повышения быстродействия, оно содержит первый элемент И, первый вход которого соединен с четвертым выходом синхрогенератора, а выход — с вторым входом процессора, и последовательно соединенные дешифратор, вход которого подключен к выходу второго блока памяти, второй элемент И, второй вход которого подключен к пятому выходу синхрогенератора, а выход — к второму входу первого блока памяти, и триггер, второй вход которого подключен к выходу дешифратора, а выход триггера подключен к второму входу первого элемента И.

1246128

Составитель С.Гришин

Техред О.Гортвай

Корректор Г.Решетник

Редактор В.Иванова

Заказ 4004/43 Тираж 455

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно †полиграфическ предприятие, г.Ужгород, ул. Проектная, 4