Приемное устройство многоканальной системы связи

Иллюстрации

Показать всеРеферат

Изобретение обеспечивает повышение помехоустойчивости. Принимаемые приемником 4 двоичные последовательности поступают на тракты записи, содержащие элементы И 11, 13, .14, 16 и регистры сдвига 12, 16. По управляющим сигналам синхронизатора 5 четные иоследовательности записываются в регистр сдвига 12, а. нечетные - в регистр сдвига 15. Формирователь импульсов -1 (генератор функций Уолша), ключи 2 и мажоритарньй элемент 3 образуют генератор адресного сигнала . Сформированная им последовательность через элемент И 17 поступает на преобразоват ель импульсов (ПИ) 9, с помощью которого выполняется прямое преобразование в базисе Уолша. Через элемент И 18 результат этого преобразования записывается в блок памяти (БП) 19. В умножителе 8. осуществляется почленное перемножение преобразованных в ПИ 9 адресного сигнала, поступившего с БП 19, и принятого сигнала. Полученная последовательность поступает на Щ 10, осуществляющий обратное преобразование Уолша. На выходе ПИ 10 будут последовательности, имеющие единственную макс, компоненту. Ее временное положение однозначно определяется ВИДОЦ принимаемой последовательности . С ПИ 10 последовательности поступают на решающий блок, содержащий компараторы 6 и кодопреобразователь 7. В нем осуществляется преобразование двухэлементного кода в п-элементный, соотв. информационной посьшке. 1 ил. I 2 с & (Л С Ю г . 6

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„ЯО„„12463 1 (5D 4 Н 04 J 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСИОМ,К СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3804388/24-09 (22) 23.10.84 (46) 23.07.86. Бюл. Ф 27 (72) О.А,Павлов и А.P. Худобко (53) 621.395.42(088.8) (56 ) Авторское свидетельство СССР

В 786027, кл. Н 04 3 11/00, 1980.

Тепляков И.М., Калашников И.Д., Рощин Б.В. Радиолинии космических систей передачи информации, — М.:

Сове гское радио, 1975, рис. 164. (54) ПРИЕМНОЕ УСТРОЙСТВО МНОГОКАНАЛЬНОЙ СИСТЕМЫ СВЯЗИ (57) Изобретение обеспечивает повышение помехоустойчивости. Принимаемые приемником 4 двоичные последовательности поступают на тракты записи, содержащие элементы И 11, 13, 1 4, 16 и регистры сдвига 1 2, 16. По управляющим сигналам синхронизатора 5 четные последовательности записываются в регистр сдвига .12, а нечетные— в регистр сдвига 15. Формирователь импульсов .1 (генератор функций Уолша), ключи 2 и мажоритарный элемент

3 образуют генератор адресного сигнала. Сформиров анная. им последовательность через элемент И 17 поступает на преобразователь импульсов (IIH) 9, с- помощью которого выполняется прямое преобразование в базисе

Уолша. Через элемент И 18 результат этого преобразования записывается . в блок памяти (БП) 19. В умножителе

8 осуществляется почленное перемножение преобразованных в ПИ 9 адресного сигнала, поступившего с БП 19, и принятого сигнала, Полученная последовательность поступает на ПИ .10, осуществляющий обратное преобразование Уолша. На выходе ПИ 10 будут последовательности, имеющие единственную макс. компоненту. Ее времен ное положение однозначно определяется видом принимаемой последовательности. С ПИ 10 последовательности поступают на решающий блок, содержащий компараторы 6 и кодопреобразователь 7, В нем осуществляется преобразование двухэлементного кода в п-элементный, соотв. информационной посылке 1 ил

1246391

1-11 А У (2) 1 1 1 1 1 1 1 1

1-1 I 1 1-1 1-1

1 1-1-1 1 1-1-1

1-1-1 1 1-1-1 1

Н=

1 1 1 1-1-1-1-1

1-1 1-1-1 1-1 1

1 1-1-1-1-1 1 1

1-1-1 1-1 1 1-1

Изобретение относится к электросвязи и может быть использовано в многоканальных системах различного назначения.

Цель изобретения — повышение помехоустойчивости.

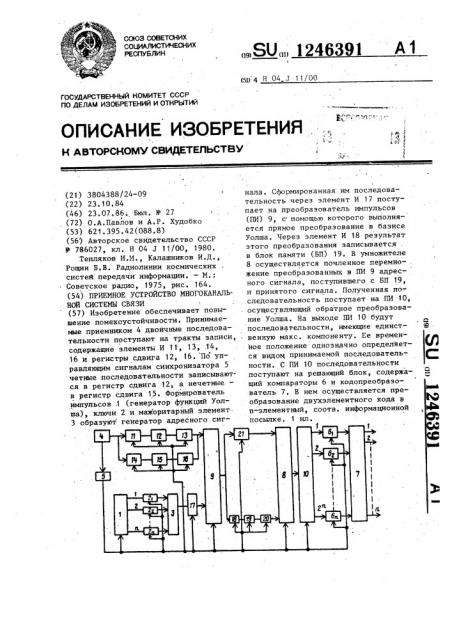

На чертеже приведена электрическая структурная схема приемного устройства многоканальной системы связи.

Устройство содержит формирователь

1 импульсов, и ключей 2„ -2„, -мажоритарный элемент 3, приемник 4, синхронизатор 5> и компараторов 6„ -6„, кодопреобразователь 7, умножитель 8, первый 9 и второй 10 преобразователи импульсов, первый элемент И 11, первый регистр 12 сдвига, второй 13 и третий 14 элементы И, второй регистр

-15 сдвига, четвертый 16, пятый 17 и шестой 18 элементы И, блок 19 памяти, седьмой 20 и восьмой 21 элементы И. .Приемное устройство многоканальной системы связи работает следующим образом.

Положим число каналов равным трем, тогда при информационных посылках, принимающих значения "1" и "-1" и поступающих на вход каждого канала передающей. стороны, имеем восемь (2 ) различных сочетаний: 111, »-1, 1-11, -111,-1-11,-11-1, 1-1-1, -1-1-1. Каждому такому сочетанию информационных символов на передающей стороне ставится в соответствие одна из восьми двоичных последовательностей..

Конкретный вид двоичной последо-.. вательности зависит от структуры генератора адресного сигнала.

В устройстве многоканальной системы связи генератор адресного сигнала содержит (генератор функций Уолша) формирователь 1 импульсов, работа которого синхронизируется сигналами от синхронизатора 5, ключи 2„ -2„ и мажоритарный элемент 3. При трех каналах иэ общего ансамбля функций

Уолша необходимо использовать только три. Если в качестве таких функций выбрать функции Радамахера (которые ,входят в ансамбль функций Уолша) и подать их на первые входы ключей

2, -2„, а на вторые входы этих ключей

2» -2„ — сигна от си ро затора 5. то на вход мажоритарного элемента 3 поступают следующие функции: 1111-1-1-1-1, 1 1-1-1 11-1-1, 1-1 1-11-11-1 .

В результате мажоритарной обработки на выходе мажоритарного элемента 3 получаем сигнал вида A, = 1» — » — 1-1-1 .

Из последовательности А путем

1 сдвига по модулю два можно получить остальные семь последовательностей:

А. =/ »-11-»-1-1-/ ° L

А„. =/1- » 1-1 — » — 1/;

А, =/-1111-1-1-11/;

А,- /111 1 1 1111 1/, А =/-»-1 — 1»-»/;

A7=/-1-11-11-111/;

A =/-1-1-11-11» /.

Эти последовательности используются на передающей стороне: каждому сочетанию трех информационных симво.лов ставится в соответствие одна из восьми последовательностей:

111 А; »-1 A

20 й

-111 А -1-» А -»-1 А

4ю 5У 6

1-1-1 А - -1-1-1 А у9 S

На приемной стороне приемного устройства необходимо использовать одну двоичную последовательность (например, последовательность А„).

Сформированная генератором адрес30 ного сигнала последовательность А

1 подается через элемент И 17 (если на его втором входе присутствует управляющий сигнал от синхронизатора 5) на первый преобразователь 9 импульЗ5 сов, с помощью которого выполняется прямое. преобразование в базисе Уолша, т.е. для данной последовательности А„ и заданного базиса Уолша,: матрица которого имеет вид

40 получаем на выходе первого преобразователя 9 импульсов следующий результат:

1246391

Н Л =/0440400-4/.

Н А =/0440-4004/.

H А =/0-440-400-4/. б то

С поступлением управляющего сигнала от синхронизатора 5 на шестой элемент И 18 результат Н А» записывается в блок 19 памяти.

Принимаемые и выделяемые приемником 4 двоичные последовательности

А„,А, .. °,А поступают на тракты записи, каждый иэ которых содержит элементы И 11 и 13 и регистр 12 сдви- га, или элементы И 14 и 16 и регистр

15 сдвига, причем управляющие сигналы от синхронизатора 5 позволяют записывать четные последовательности в регистр 12 сдвига, а нечетные — в регистр 15 сдвига.

Рассмотрим работу для случая, когда первая принятая двоичная последо- вательность имеет вид А4, а вторая

А . Последовательность А проходит через элемент И 11 при наличии на его втором входе управляющего сигнала от синхронизатора 5 и записывается в регистр 12 сдвига. Когда последовательность А6 полностью записана, поступает сигнал от синхронизатора 5 на второй вход второго элемента И 13 и последовательность А6 подается через второй элемент И 13 на первый преобразователь 9 импульсов, на выходе которого имеем результат:

При наличии на вторых входах элементов И 21 и 20 управляющих сигналов от синхронизатора 5 результат

Н А от первого преобразователя .9 им6 пульсов и результат Н А» от блока 19 памяти поступают на умножитель 8, с помощью которого осуществляется почленное перемножение. В итоге получаем последовательность следующего вида:

Н А Н A /0,-16, 16,0-16,0,0, 16/, которая поступает на второй преобра.зователь 10 импульсов, осуществляющий обратное преобразование Уолша.

В результате обратного преобразования получаем-следующую последовательность:, 1. — Н ° (Н А ° Н ° А )= 0,0,-8,0,0,8,0,0, (3) в которой имеется одна компонента с максимальным значением.

В интервале времени, когда вычисляется результат Н А, осуществляется запись второй последовательности

А во второй регистр 15 сдвига при наличии управляющего сигнала от синхронизатора 5 на втором входе элемента И 14. В промежуток времени вычисления результата перемножения

H А(, ° Н А» и последующего нахождения

1О обратного преобразования Уолша последовательность А подается на вход первого преобразователя 9 импульсов (когда эта последовательность полностью записана во второй регистр 15

15 сдвига и на второй вход элемента

И 16 поступает управляющий сигнал от синхронизатора 5) и находится прямое преобразование Уолша последовательности АО.

20 Такое распределение во времени вычислений позволяет обеспечить работу приемного устройства в реальном масштабе времени.

Вычисление прямого преобраэова25 ния Уолша последовательности А осу8 ществляется как и для последовательности .А„. Результат вычисления имеет вид

В дальнейшем над последовательностью Н А> проводятся такие же преобразования, как и для последовательности Н А . В итоге последо.вательно получаем Н А Н А,= 0,-16, 16,0, 16,0,0,-16), 1

40 8 — Н (Н А ° Н А )=(О 8 0000-80). (4) 5

Если принимаемая последовательность

45 А = 1 111-1 — 11 1 — Н.(Н А Н А )=(000 — 88000).

8 (Последняя последовательность имеет, как и последовательности (3) и (4), только одну максимальную компоненту.

Аналогичнф м способом можно полу-. чить последовательности на выходе второго преобразователя 10 импульсов для оставшихся пяти исходных

1246391 последовательностей вида (1). Из рассмотрения структуры последовательностей на выходе второго преобразователя 10 импульсов следует, что

5 при одном и том же виде адресного сигнала (в рассмотренном случае это последовательность А„) и различных последовательностей вида (1), принимаемых приемником 4, на выходе вто-, 1О рого преобразователя 10 импульсов будут последовательности, имеющие единственную максимальную компоненту, причем временное положение этой компоненты однозначно определяется t5 видом принимаемой последовательности.

Последовательности с выхода второго преобразователя 10 импульсов поступают на решающий блок, который содержит компараторы 6 -6> и кодо- 20 преобразователь 7. С помощью компараторов 6 -6 осуществляется сравнеИ ние по уровню входного и порогового c сигналов, а также формирование выходного напряжения с одним из двух 25 уровней, соответствующих "0" или

"1", в зависимости от того, превышает или нет входное напряжение пороговое. В результате последовательность, поступающая на вход решаю- ЗО щего блока, первоначально преобразуется в кодовую последовательность, содержащую единичные и нулевые элементы. Так, например, если последовательность имеет вид /00-80-0800/, то на выходе компараторов 6, -6„ имеем кодовую последовательность

/00000100/.

Затем кодовая последовательность поступает на кодопреобразователь 7, 40 который позволяет реализовать преобразование в общем случае 2х-элементного кода в п-элементный код, элементы которого соответствуют передаваемым информационным символам. Так, в 45 рассматриваемом случае, когда число каналов п=З если на передающей сто7 роне по первому, второму и третьему каналам передаются соответственно информационные символы "-1", "1" и . "-1", то на выходе приемника 4 имеем согласно выражению (2) последовательность Аь. Этой последовательности соответствует на выходе второго преобразователя 10 импульсов последова- 55 тельность /00-80-0800/, которая содержит шестую компоненту с максимальным значением. При такой последовательнос ги с выходов компараторов 6 —

6 „ получаем последовательность

/00000100/, а на выходе кодопреобразователя 7 — 11-1. Элементы этой последовательности соответствуют информационным символам, передаваемым по первому, второму и третьему кана— лам соответственно.

Управление работой элементов И 11, 13,14, 16-18, 20 и. 21, регистров 12 и 15 сдвига, блока 19 памяти, умножителя 8, компараторов 6 -6, а также

1 первого 9 и второго 10 преобразователей импульсов осуществляется сигналами, формируемыми синхронизатором

5, работа которого синхронизируется сигналом, поступающим на вход синхронизатора 5 с второго выхода приемника 4.

Предложенное приемное устройство многоканальной системы связи осуществляет преобразование вида — ° И(Н А .Н А ), 1

N J где Н вЂ” матрица Уолша;

N — число строк в матрице Уолша, Ф о р м у л а изобретения

Приемное устройство многоканальной системы связи, содержащее формирователь импульсов, выходы которого соединены с первыми входами и ключей, выходы которых соединены с соответствующими входами мажоритарного элемента, а также приемник, первый выход которого соединен с входам синхрони- затора, выход которого соединен с входом формирователя импульсов и вторыми входами и ключей, а также и компараторов, выходы которых соединены с входами кодопреобразователя а первые входы п компараторов объединены и соединены с выходом синхронизатора и первым входом умножителя, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введены первый и второй преобразователи импульсов, первый вход второго преобразователя ймпульсов соединен с выходом умножителя, второй вход второго преобразователя импульсов соединен с первым входом умножителя, а также последовательно соединенные первый элемент И, первый регистр сдвига, второй элемент И, Составитель А. Левитская

Техред П.олейник

Корректор Е. Сирохман

Редактор О. Головач

Тираж 624

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Закаа 4024/57

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

7 1246391 . 8 выход которого соединен с первым жоритарного элемента, а выход пятовходом первого преобразователя им- го элемента И соединен с третьим пульсов, второй вход которого соеди- входом первого преобразователя имнен с выходом синхронизатора, а также, пульсов, второй вход пятого элеменпоследовательно соединенные третий та И соединен с выходом синхрониза, элемент И, второй регистр сдвига, . тора, а также. последовательно соедичетвертый элемент И, выход которого ненные шестой элемент И, блок памясоединен с выходом второго элемен- ти, седьмой элемент И, выход которота И, а входы первого и третьего го соединен с вторым входом умножиэлементов И объединены и соединены о теля, а вход шестого элемента И с вторым выходом приемника, вторые соединен с выходом первого преобравходы первого, второго, третьего и зователя импульсов и входом восьмочетвертого элементов И, первого и го элемента И, выход которого..соедивторого регистров сдвига объединены нен с третьим входом умножителя, и соединены с выходом синхронизато-, 15 вторые входы шестого, седьмого,восьмора, а также пятый элемент И, первый ro элементовИ иблока памятиобъединевход которого соединен с выходом ма- ны исоединены свыходом синхронизатора