Устройство для ввода-вывода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназна чено для обмена данными между ЭВМ и внешними устройствами, между двумя ЭВМ, соединенными.друг с другом по принципу внешнего устройства. Целью изобретения является повышение помехозащищенности устройства за счет сравнения передаваемого и принятого внешним устройством байтов. В случае наличия помех и искажения сообщения осуществляется повторная передача того же байта до тех пор, пока он не будет принят без искажений внешним устройством. Для подтверждения правильности приема используется иМ- пульс-квитанция, по приеме которого передается следующий байт, Устройство содержит блок элементов ИЛИ-, последовательно соединенные регистры за-г писи данных и адресов, регистры вывода данных и адресов, схему ИЛИ, триггер вывода, первую,, вторую и третью схемы И, коммутатор, регистры ввода данных и адресов, блок сравнения , формирователь, селектор длительности импульсов, регистры чтения данных и адресов, триггер готовности, дешифратор адреса. С ЭВМ устройство соединяется с помощью шины данных и адресов и линий запроса ввода, вывода и готовности. Передача информации осуществляется в последовательном коде . 1 ил. .с (О (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУ БЛИН (gg 4 G 06 F 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3878092/24-24 (22) 25, 02. 85 (46) 30,07. 86. Бюл. Ф 28 (72) Т.А. Сычева, Е.А. Скурко, Е.В.Иванов и B.È.Ìàëüêoâ (53) 681 ° 14(088.8) (56) Авторское свидетельство СССР

N -708339, кл. С 06 F 3/02, 1980, Авторское свидетельство СССР

Ф 737937, кл, G 06 F 3/00, 1980. (54) УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и предназначено для обмена данными между ЭВМ и внешними устройствами, между двумя

ЭВМ, соединенными. друг с другом по принципу внешнего устройства. Целью изобретения является повышение помехозащищенности устройства за счет сравнения передаваемого и принятого внешним устройством байтов. В случае

ÄÄSUÄÄ 1247856 А1 наличия помех и искажения сообщения осуществляется повторная передача того же байта до тех пор, пока он не будет принят без искажений внешним устройством. Для подтверждения правильности приема используется импульс-квитанция, по приеме которого передается следующий байт. Устройство содержит блок элементов ИЛИ, последовательно соединенные регистры за-. писи данных и адресов, регистры вывода данных и адресов, схему ИЛИ, триггер вывода, первую, вторую и третью схемы И, коммутатор, регистры ввода данных и адресов, блок сравнения, формирователь, селектор длительности импульсов, регистры чтения данных и адресов, триггер готовности, дешифратор адреса. С ЭВМ устройство соединяется -с помощью шины данных и адресов и линий запроса ввода, вывода и готовности. Передача информации осуществляется в последовательном коде, 1 ил.

1 247856

Изобретение относится к вычисли тельной технике и предназначено для обмена данными между ЭВМ и внешними устройствами, между двумя ЭВМ, подключенными друг к другу по типу внешних устройств °

Цель изобретения — повышение помехозащищенности устройства.

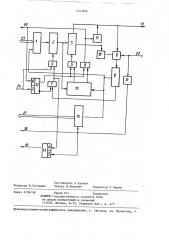

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 элемен— тов ИЛИ, третий регистр 2, первый регистр 3, элемент ИЛИ 4, .первый 5, второй 6 и третий 7 элементы И, коммутатор 8, второй регистр 9,„ блок

10 сравнения, формирователь 11, первый 12 и второй 13 триггеры, четвертый регистр 14, селектор 15 длительности импульсов, дешифратор 16. На схеме указаны входы и выходы устройства 17-24.

Устройство работает следующим образом.

В режиме передачи данные и адрес из ЭВМ в параллельном коде поступают по шинам вывода данных и адреса 23 через блок 1 элементов ИЛИ в регистр 2, переписываются в регистр

3, иэ которого информация в последовательном коде поступает через выход 17 устройства в линию связи с внешним устройством. В регистр 2 код заносится по сигналу, поступающему со входа 24 через схему ИЛИ 4.

Одновременно по этому сигналу срабатывает триггер 12, на прямом выходе .которого появляется положительный потенциал, открывающий первую и вторую схемы И 5 и 6. Код, принятый внешним устройством, возвращается по линии связи через вход 22 и коммутатор 8, проходит на вход регистра 9 для записи, откуда в параллельном виде подается на входы блока 10 сравнения, где сравнивается с кодом, хранящемся в регистре 2. Если не было искажений при передаче и коды одинаковы, на выходе блока сравнения "равно" появляеФся сигнал, проходящий через вторую схему И 6 для формирования на выходе 20 запроса вывода из ЭВМ следующего кода, для перевода триггера 12 в нулевое состояние, и для посыпки сигнала подтверждения безошибочной передачи, образованного формирователем 11 в линию связи через выход 17 устрой,ства.

45 да селектора 15 служит для формирования запроса ввода на выходе 18 для записи кода из регистра 9 в регистр

14 и для переключения триггера 1 3 в единичное состояние. На выходе 19 устройства появляется сигнал готовности.

Если же вернувшийся иэ устройства ввода-вывода информации код не равен переданному, то внешнее устройство передает этот код повторно, и так до тех пор пока передача осуществится без искажений и коды совпадут °

Дешифратор адреса 16 служит для использования в режиме контроля исправности устройства ввода-вывода информации..

Использование предлагаемого устройства позволяет повысить помехоЕсли коды не одинаковы, т ° е. имеет место искажение, на выходе блока

10 сравнения неравно появляется сигнал, который проходит через первую схему И 5 на управляющий вход регистра 3, что приводит к записи в регистр 3 кода, хранящегося в регистре 2. Происходит повторная передача кода в линию связи через выход

10 17 устройства. Далее работа будет повторяться до тех пор, пока внешнее устройство не примет неискаженный код.

В режиме приема последовательного кода с линии связи через вход 22 устройства происходит запись кода в регистр 9. Триггер 12 в режиме приема находится в нулевом состоянии, поэтому открыта третья схема

И 7, через которую сигнал окончания записи последовательного кода с регистра 9 проходит на R — вход триггера

13. На выходе 19 устройства появляется низкий потенциал, означающий, что устройство не готово к обмену с ЭВМ.

Код регистра 9 через блок элементов

ИЛИ l поступает на вход и записывается в регистре 2 по сигналу, пришедше.

30 му с третьей схемы И 7 через схему

ИЛИ 4., Полученный из линии связи код переписывается в регистр 3 и посылается назад во внешнее устройство для проверки через выход 17 устройства.

Если код получен без искажений, внешЗ5 нее устройство посылает удлиненный импульс, представляющий собой сигнал подтверждения безошибочной передачи, который фиксируется селектором длительности сигнала 15. Сигнал с выхоl24 защищенность и в результате приводит к экономии машинного времени, так как устройство ввода информации работает с терминалом самостоятельно в режимах приема, передачи и контроля информации, передаваемой в обоих направлениях, выставляя ЭВМ запрос на ввод или вывод лишь при положительном результате проверки после множества повторных передач. 1О

Формула изобретения Устройство для ввода-вывода информации, содержащее первый и второй ре->5 гистры, дешифратор, коммутатор, первый выход первого. регистра соединен с входом дешифратора, выход которого соединен с первым входом коммутатора, второй вход которого является вторым входом устройства, а выход соединен с входом второго регистра, второй выход первого регистра соединен с третьим входом коммутатора и является первым выходом устройства, о т л и — д ч а ю щ е е с я тем, что, с целью повышения помехозащищенности, в него введены блок элементов ИЛИ, третий и четвертый регистры, первый и второй триггеры, с первого по третий ЗО элементы И, элемент ИЛИ, -блок сравнения, селектор длительности импульсов, формирователь, входы первой группы блока элементов ИЛИ являются входами группы устройства, выходы блока эле35 ментов ИЛИ соединены с входами группы третьего регистра, выходы которого соединены с входами группы перво7856 4 го регистра и входами второй группы блока сравнения, первый вход первого триггера соединен с первым входом элемента ИЛИ и является первым входом устройства, первый выход первого триггера соединен с первыми вхо-. дами первого и второго элементов И, а второй выход — с первым входом третьего элемента И, выход которого соединен с вторыми входами элемента

ИЛИ и второго триггера, выход элемента ИЛИ соединен с входом первого регистра, выходы группы, второго регистра соединены с входами второй группы блока элементов ИЛИ, с входами первой группы блока сравнения и четвертого. регистра, выход второго регистра соединен с вторым входом третьего элемента И, вход селектора длительности импульсов соединен с вторым входом коммутатора, а выход соединен с входом четвертого регистра, первым входом второго триггера и является вторым выходом устройства, выход второго триггера является третьим выходом устройства, выходы четвертого регистра являются выходами группы устройства, выход второго элемента И соединен с входом формирователя вторым входом первого триггера и является четвертым выходом устройства, выход первого элемента И соединен с входом первого регистра, выход формирователя соединен с третьим входом коммутатора, первый и второй выходы блока сравнения соединены с вторыми входами первого и второго элементов И соответственно, 1247856

Составитель А.Трунов

Техред М.Ходанич Корректор С.Черни

Редактор И.Сегляник

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 8-35, Раушская наб., д. 4/5

Заказ 4126/48

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4