Многоканальная система ввода аналоговой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в системах многопозиционного контроля датчиков. Цель изобретения - повьшение пропускной способности устройства - достигается введением триггера, счетчика, мультиплексора и блока оперативной памяти, которые позволяют расположить р.езультаты измерения по порядку нумерации датчиков и дают возможность заменить передачу адресной информации с выхода устройства на информацию с измерительных датчиков. Изобретение - дополнительное к авт.св. № 450157. 1 ил. i

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСГ1УБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ИБАК01ЕЫА

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 450157 (21) 3769302/24-24 (22) 06.07.84 (46) 30.07.86. Бюл. ¹ 28 (71) Казанский ордена Трудового Красного Знамени и ордена Дружбы народов авиационный институт им. А.Н.Туполева (72) 1О.К.Евдокимов, Д.В.Погодин, Е.Ф.Базлов и С.Н.Варнавский (53) 681.327,21(088.8) (56) Авторское свидетельство СССР № 450157, кл. G 06 Р 3/05, 1968. (54) МНОГОКАНАЛЬНАЯ СИСТЕМА ВВОДА

АНАЛОГОВОЙ ИНФОРМАЦИИ

„„SU„124 5 А 2 (ц 4 С Об F 3/05 (57) Изобретение относится к области вычислительной техники и может быть использовано в системах многопозиционного контроля датчиков. Цель изобретения — повышение пропускной способности устройства — достигается введением триггера, счетчика, мультиплексора и блока оперативной памяти, которые позволяют расположить результаты измерения по порядку нумерации датчиков и дают возможность заменить передачу адресной информации с выхода устройства на информацию с измерительных датчиков. Изобретение — дополнительное к авт.св. № 450157.

1 ил.

)2478

Изобретение относится к вычислительной технике и может найти применение в информационно-измерительных системах, в автоматизированных системах для научных исследований и в системах автоконтроля и является усовершенствованием изобретения по авт.св.

N - 450157.

Цель изобретения — повышение пропускной способности системы. (0

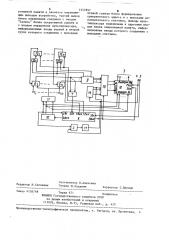

На чертеже приведена блок-схема. многоканальной системы ввода.

Система содержит входы аналоговых величин 1 -1„ дополнительный триггер 2, информационные выходы 3, 15 управляющий выход 4, управляющий вход 5, схемы сравнения 6„ -6„, элемент ИЛИ 7, блок управления 8, блок формирования приоритетного адреса 9, счетчик 10, цифро-аналоговый преобра- 20 зователь (ЦАП) 11, элементы И 12 — 12„ .и триггеры 13 — 13„, дополнительный счетчик 14, мультиплексор )5, блок оперативной памяти 16, генератор 17, Многоканальная система ввода работает следующим образом.

Аналоговые сигналы подаются на входы аналоговых величин 1, -)т, На суммирующий вход счетчика 10 блок управления 8 подает последователь- Ç0 ность импульсов. Цифро-аналоговый преобразователь 11 преобразует циф.ровой код на выходе счетчика 10 в аналоговую величину, поступающую на выходы схем сравнения 6 -6>, кото- З5 рые сравнивают эту аналоговую величину с аналоговыми величинами на входах 1„ -1„ . Если укаэанные величины на входах некоторой схемы сравнения, например 6., совпадают, то на ее вы- 40 ходе устанавливается единичное состояние.

Если хотя бы одна из схем сравнения 6 -6, находится в единичном состояний, то элемент ИЛИ 7 вырабатыва- 4 ет сигнал, поступающий в блок управления 8.

Одновременно с этим блок формирования приоритетного адреса 9, входы .которого соединены с выходами схем сравнения 6, -6„, формирует на своих выходах позиционный и двоичный коды номера старшей по установленному приоритету схемы сравнения иэ всех тех, которые находятся в данный момент в единичном состоянии.

С момента появления единичного сигнала на входе элемента ИЛИ 7 блок

57 2 управления 8 запрещает выдачу импульсов на вход счетчика 10 и формирует единичный сигнал Запись на третьем выходе. По сигналу Запись мультиплексор 15 подключает выходы блока формирования приоритетного адреса 9 к адресным входам блока оперативной памяти 16. Одновременно по сигналу Запись., поданного на управляющий вход "Запись блока 16, осуществляется запись кода результата преобразования, соответствующего амплитуде аналогового сигнала и поступающего с выходов счетчика 10 на информационные входы, в ячейку памяти блока 16. Причем адрес ячейки памяти определяет двоичный код адреса, соответствующий номеру входа аналоговой величины, для которого входная аналоговая величина равна аналоговой величине на выходе цифроаналогового преобразователя 11, сформированный на соответствующих выходах блока формирования приоритетного адреса 9. По окончании этой операции блок управления 8 формирует на четвертом выходе сигнал, который поступает на выходы всех элементов И )7„ †12 „. Вторые входы элементов И 12„-12 соединены индивидуально с выходами. блока формирования приоритетного адреса 9, на которых формируется позиционный код адреса входа аналоговых величин, дЛя которого входная аналоговая величина равна аналоговой величине на вьгходе цифроаналогового преобразователя 11. Поэтому, при наличии сигнала на какомлибо из этих выходов блока формирования приоритетного адреса, триггер 13 переходит в единичное состояние.. В силу того, что сигнал с нулевого выхода каждorо из этих триггеров 13 поступает на запрещающий вход соответствующей схемы сравнения 6, она принудительно устанавливается в нулевое состояние и удерживается в нем до окончания всего цикла преобразования.

Если при этом единичный сигнал, на выходе элемента ИЛИ 7 сохраняется, что указывает на,наличие единичного состояния еще одной или нескольких схем сравнения 6, то блок управления

8 вырабатывает очередной сигнал

II II

Запись на третьем выходе и описанный процесс записи информации в блок

16 повторяется ° Такой процесс продол1247857 жается до тех пор, пока присутствует единичный сигнал на выходе элемента

ИЛИ 7.

Когда сигнал на выходе элемента

ИЛИ 7 становится нулевым, т.е. принудительно с помощью соответствующе-. го триггера 13 устанавливается в нулевое состояние, последняя из схем сравнения 6, сработавших в данном такте преобразования, блок управле- 10 ния 8 разрешает дальнейшее поступление импульсов на вход счетчика 10.

Единичное состояние любого из триггеров 13 сохраняется до конца цикла преобразования, что обеспечива- 15 ет запоминание в конце каждого такта преобразования результатов преобразования только по тем входам аналоговых величин 1, схемы сравнения 6 которых устанавливаются в единичное состояние s данном такте преобразования .

В конце цикла преобразования все ячейки блока оперативной памяти 16 заполняются результатами преобразо- 2s .вания, соответствующими амплитуде входных аналоговых величин 1, -1„ .

Причем расположение данных по ячейкам в блоке 16 строго упорядочено, поскольку адресация ячеек памяти осу- З0 ществляется по двоичному коду адреса, соответствующему номеру входа аналоговых величин 1„ — 1„. Таким образом, в ячейку памяти Р 1 записывается результат преобразования по,входу 11- 1

35 аналоговой величины, в ячейку 11 2— результат преобразования по входу и: 2и тд, По окончании-цикла преобразования счетчик 10 переполняется. При этом 40 сигнал на выходе старшего разряда счетчика 10, подаваемый на второй вход блока управления 8, с единичного состояния переходит в нулевое, по которому блок управления 8 на первом 4 выходе вырабатывает сигнал сброса триггеров 13. Одновременно с этим . сигнал на третьем выходе блока управления 8 переключается в нулевое состояние, по которому блок 16 переводится в режим "Считывание., а мультиплексор 15 подключает выходы счетчика 14 к адресным входам блока оперативной памяти 16.

Одновременно по перепаду (фронту) сигнала со старшего разряда счетчика

10 взводится в единичное состояние триггер 2 и генератор 17 начинает генерировать импульсы, поступающие на счетный вход счетчика 14 и вход

"Считывание" блока оперативной памяти 16. Одновременно с этим. также формируется запрос на управляющем выходе 4 системы ввода.

Импульсы, поступающие на счетный вход счетчика 14, последовательно увеличивают содержимое счетчика 14 на единицу и этим обеспечивают последовательное считывание по адресам ячеек памяти результатов преобразования, хранящихся в блоке оперативной памяти 8, во внешнее устройство, подключенного к информационным выходам 3 системы ввода.

По окончании цикла считывания во внешнее устройство счетчик 14 переполняется; При этом сигнал на выходе его старшего разряда, подаваемый на нулевой вход триггера 2, с

Ф единичного состояния переходит в нулевое состояние, по которому (по фронту сигнала) триггер 2 переключается в нулевое состояние и генератор 17 прекращает выдачу импульсов.

Следующий цикл преобразования, аналогичный описанному, начинается после прихода сигнала на управляющий вход 5 системы ввода от внешнего устройства (на чертеже не показано).

Увеличение пропускной способности устройства достигается за счет исключения выдачи служебной адресной информации и замене ее информацией с измерительных датчиков.

Формула изобретения

Многоканальная система ввода аналоговой информации по авт. св.

Ф 450157, отличающаяся тем, что, с целью повьппения пропускной способности системы, в нее введены дополнительный триггер, генератор, дополнительный счетчик, мультиплексор и блок оперативной памяти, выходы которого являются информационными выходами устройства, выходы старших разрядов счетчика и дополни- . тельного счетчика соединены с входа- . ми установки в единицу и ноль дополнительного триггера, выход которого соединен с входом управления генератора, выход которого подключен к счетному входу дополнительного счет,чика, к входу "Считывание" блока опеСоставитель И.Алексеев

Техред M.Õîäàíè÷ Корректор С.Шекмар

Редактор И.Сегляник

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4126/48

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 1 ративной памяти и является управляющим выходом устройства, третий выход блока управления соединен с входом

"Запись" блока оперативной памяти и с входом управления мультиплексора, информационные входы первой и второй групп которого соединены с выходами

247857 б первой группы блока формирования приоритетного адреса и с выходами дополнительного счетчика, выходы мультиплексора подключены к адресным входам блока оперативной памяти, информационные входы которого соединены с выходами счетчика.