Устройство для нормализации избыточных кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники. Целью изобретения .является расширение класса решаемых задач за счет обеспечения возможности вьшолнения операции нормализации чисел, представленных в избыточных ри г-кодах. Это достигается за счет введения в устройство, содержащее две группы элементов И, элемент И, группу триггеров и группу элементов запрета, сумматора и изменения связей между известными элементами . Изобретение может быть использовано в специализированных вычислительных системах при помехоустойчивой обработке информации. 1 ил. 4; 00 а

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН (5D 4 G 06 F 7/49

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЬИЬ, 1ИИИ! А (21) 3823204/24-24 (22) 12 ° 12.84 (46) 30.07.86. Бюл. 11 - 28 (72) Н.А. Збродов (53) 681.3(088.8) (56) Авторское свидетельство СССР

Р 1005024, кл. G 06 F 5/00, 1981.

Авторское свидетельство СССР

У 842782, кл. G 06 F.5/00, 1979. (54) УСТРОЙСТВО ДЛЯ НОРИАЛИЗАЦИИ ИЗБЫТОЧНЫХ КОДОВ (57) Изобретение относится к области цифровой вычислительной техники. Це„„SU„„12478 1 А1 лью изобретения является расширение класса решаемых задач за счет обеспечения возможности выполнения операции нормализации чисел, представленных в избыточных р- и r-кодах. Это достигается за счет введения в устройство, содержащее две группы элементов И, элемент И, группу триггеров и группу элементов запрета, сумматора и изменения связей между известными элементами. Изобретение может быть использовано в специализированных вычислительных системах при помехоустойчивой обработке информации. l ил.

1247861

Устройство для нормализации избыточных кодов содержит группу элементов И,1.1-!.3, группу элементов 2.12,3 запрета, группу элементов И 3.1—

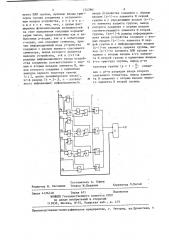

3.3, группу элементов ИЛИ 4, группу триггеров 5, сумматор 6, элемент И 7, информационный вход 8, установочныйвход 9 и выход 10 устройства.

Ф разряда

n °

2-код

9

108

Значения а -а разрядов соответсто венно со второго по девятый исходного числа поступают со входа 8 устройства на элементы И 1 группы, элементы 2 запрета группы и элемент И 7. !

Единичные сигналы формируются на выходе первого элемента И 1.1 и элемента 2.2 запрета. На выходе первых элементов И 1.2, 1.3, и элементов

2.1, 2.3 запрета формируются нулевые

35 сигналы. Единичный сигнал с выходаэлемента И 1.1 поступает на вход второго элемента ИЛИ 4 группы, единичным сигналом с выхода которого асин40 хронно устанавливается в единицу соответствующий триггер 5 и разрешается прохождение единичного сигнала с элемента 2.2 запрета через второй элемент И 3.2 на второй вход треть45 его. элемента ИЛИ 4, единичным сигналом с которого устанавливается в единицу триггер 5. На выходах вторых элементов И 3.1, 3.3 и 7 формируются нулевые сигналы. Следовательно, на выходах первого и четвертого элеS0 ментов ИЛИ 4 группы формируются нулевые сигналы. Единичные значения с выходов второго и третьего триггеров 5 группы поступают соответственно на четвертый и шестой разряды входа второго слагаемого сумматора 6, на входы остальных разрядов второго слагаемого поступают нулевые эначеИзобретение относится к вычислительной, аналого-цифровой, цифроаналоговой технике и может быть использовано в процессорах специализированных вычислительных машин. 5

Цель изобретения — расширение функциональных возможностей за счет выполнения операции нормализации чисел, представленных как в избыточных р-кодах, так и в избыточных r-кодах. !О

На чертеже представлена схема уст ройства для нормализации избыточных кодов (при r = 2, n = 9).

Вес h 1-ого разряда при представ1 лении натуральных чисел в r-кодах определяется следующим соотношением:

1, при i = 1;

h — 1 + h ° -2 при i = pr +2;

1 1

2h; -1, в остальных случаях, Одному и тому же числу в r-кодах соответствует несколько форм его записи. Процесс нормализации числа состоит в замене единиц в pr-ом и (рг+1)-ом разрядах исходная числа нулями и записи единицы в (рг+г)-ой разряд.

Устройство для нормализации избыточных кодов работает следующим об,разом.

Перед началом работы триггера 5 группы по входу 9 устройство устанавливается в нулевое состояние, Предположим, что необходимо нормализовать 2-код числа 54, представляемого следующим образом:

8 7 6 5 4 3 2

54 36 18 12 6 4 2

О 1, О 1 1 О О 0

I ния. В сумматоре 6 сформированные значения складшваются с числом, поступившим с информационного входа 8 устройства на вход первого слагаемого сумматора 6, по правилам двоич-. ной арифметики:

2-код ... О О 1 О 1 1 0 0 О триггера ... О О О 1 О 1 О 0 0

010 00 00 00=

= 54

Результат с выхода сумматора 6 поступает на выход 10 устройства.

Длительность периода следования управляющих импульсов считывания результата с выхода 10 устройства должна выбираться с учетом окончания переходных процессов в комбинационной логике и триггерах устройства.

Дополнительный эффект изобретения состоит в сокращЕнии аппаратурных затрат.

Формула изобретения

Устройство для нормализации избыточных кодов, содержащее две группы элементов И, группу элементов запрета, группу элементов ИЛИ, группу триггеров, элемент И, причем выходы элементов И первой и второй групп соединены соответственно с первым и вторым входами соответствующего эле10

Составитель А. Клюев

Редактор И. Сегляник Техред М.Ходанич Корректор Л.Патай

Заказ 4126/48 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Б-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул.Проектная, 4

3 1247 мента ИЛИ группы, нулевые входы.трит— геров группы соединены с установочным входом устройства, о т л и ч а— ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения операции нормализации чисел, представленных как в избыточных р-кодах, так и в избыточных

r-кодах, оно содержит сумматор, причем информационный вход устройства соединен с входом. первого слагаемого сумматора, выход которого является выходом устройства, г-й и (r+l)-й разряды информационного входа устройства соединены соответственно с пер- 15 вым и вторым входами элемента И, выход которого соединен с единичным выходом первого триггера группы (г ), 2, целое положительное число), kr-й разряд (k = ;,, n — разряд- N ность информации) информационного

86 4 входа устройства соединен с первым входом (k-1)-ro элемента И первой группы и с управляющим входом (k-l)го элемента запрета группы; выход которого соединен с первым входом соответствующего элемента И второй группы, (Кг+1)-й разряд информационного входа устройства соединен с вторым входом (k-1)-го элемента И первой группы и с информационным входом (k 1)-го элемента запрета группы, выход (k-1)-го элемента ИЛИ группы соединен с вторым входом k-ro элемента И второй группы и единичным входом

k-го триггера группы, выход р-ro

Il триггера группы (р = 1 — -) соедиг нен с pr-м разрядом входа второго слагаемого сумматора, выход элемента И соединен с вторым входом первого элемента И второй группы..