Устройство для сложения и вычитания чисел по модулю @

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах и устройствах, функционирующих в системе остаточных классов. Цель изобретения - повышение быстродействия выполнения операции модульного вычитания за счет исключения из схемы устройства сумматора по модулю Р , игравшего в прототипе роль инвертора по модулю Р второго операнда Ь. Повышение быстродействия выполнения оЯерации модульного вычитания достигается путем введения трех групп элементов И,двух групп элементов ИЛИ и двух элементов И, при этом при режиме модульного вычитания первый операнд А подается на вход второго входного регистра,а второй операнд В - на вход первого входного регистра. В предлагаемом устройстве для алгоритма определения результата операции модульного вычитания используется следукщее отношение А+ ( Р - &) (Р - fc) + А . 1 ил. в (Л ю . ч 00 О) сх

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

„„SU„„1247868

m 4 С 06 Р 7/72

i В ." "

1И,, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЬКБЛм".

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbITHA (21) 3852448/24-24 (22) 08.02.85 (46) 30.07..86, Бюл.. Р 28 (72) О,Н.Фоменко, В.А. Краснобаев, В.А,Каревский и .В.M.Ïàíêoâ (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР

К - 885999, кл. G 06 F 7/72, 1981.

Авторское свидетельство СССР

Ф 3705029, кл. G 06 F 7/72, 1983. (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ Р (57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах и устройствах, функционирующих в системе остаточных классов. Цель изобретения — повышение быстродействия выполнения операции модульного вычитания эа счет исключения из схемы устройства -сумматора по модулю Р, игравшего в прототипе роль инвертора по модулю P второго операнда В, Повышение быстродействия выполнения оПерации модульнога вычитания достигается путем введения трех групп элементов И,двух групп элементов ИЛИ и двух элементов И, при этом при режиме модульного вычитания первый операнд А подается на вход второго входного регистра, а второй операнд B — на вход первого входного регистра. В предлагаемом устройстве для алгоритма определения результата операции модульного вычитания используется следующее отношение

A+ (Р— Ь) = (P — Ь) +А. 1ил.

1 12478

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах и устройствах, функционирукнцих в системе остаточных классов °

Цель изобретения — повышение быстродействия.

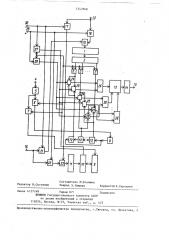

На чертеже представлена структурная схема устройства для сложения и вычитания чисел по модулю .

Устройство содержит первый входной регистр 1, дешифратор 2, первая группа элементов И 3, вход запуска устройства 4, генератор импульсов (ГИ) 5, первый и второй элементы

И 6 и 7, умножитель 8, суммирующий счетчик 9, схема сравнения 10, второй входной регистр 11, кольцевой сдвигающий регистр (KCP) 12, элемент

ИЛИ 13, выходной регистр 14, выход результата 15, первый информационный вход 16, пятая и шестая группы,элементов И 17 и 18, вторая группа элементов ИЛИ 19, второй информационный вход 20, четвертая группа элементов

И 21, третья группа элементов И 22, первая группа элементов ИЛИ 23, вторая группа элементов И 24, сецьмая группа элементов И 25, третья группа элементов HJIH 26, третий и четвертый элементы И 27 и 28, входы управления сложением и вычитанием 29 и 30.

Дешифратор 2 преобразует операнд из двоичного кода в унитарный. Kîличество выходных шин равно Р(0- . Р -1)

Умножитель частоты 8 В n = 35

j2og (Р-1))+1 раз увеличивает коли2 честно. выходных импульсов генератора 5.

Количество разрядов КСР 12 равно количеству возможных остатков по исходному модулю P . Каждый разряд

КСР 12 состоит из и —,.f og (Р 1)j +1 двоичных разрядов, необходимых для представления наибольшего вычита по модулю Р

Работу устройства удобно рассмотреть в двух режимах: режим определения результата операции модульного сложения и режим определения результа- 5О та операции модульного вычитания.

Исходное состояние устройства: нулевое состояние регистров 1 11 и 14,, а в разрядах KCP 12 записана первая строка таблицы модульноro сложения (вычитания) (А+В)modP.

Определение результата операции (А+В)шойР.

68 2

Присутствует сигнал шины 29..По входной шине 16 операнд я в двоичном коде через открытые элементы

И 18 шестой группы, элемент ИЛИ второй группы 19, регистр 1 поступает на вход дешифратора 2, с выхода которого сигнал, соответствующий значению Н, поступает на первый вход

Л (А = 0 P-1) элементов И первой группы 3. А по входной шине 16 второй операнд В в двоичном коде через открытые элементы И 22 третьей группы, элемент ИЛИ первой группы 23 поступает в регистр 11. По сигналу шины 4 с выхода ГИ 5 на вход открытых элементов И 6 и 7, с выхода элемента И 6 импульсы через умножитель 8 (где они увеличиваются в и= (1о8 (P-1))+

+1 раз) поступают на вход KCP 12, сдвигая его содержимое на В и двоичных разрядов влево (против часовой стрелки). Одновременно с выхода элемента И 7 имцульсы поступают на вход суммирующего счетчика 9. При совпадении содержимого счетчика 9 и ре гистра. 11, выходной сигнал схемы сравнения 10 закрывает элементы И 6 и 7, открывает А-й элемент И первой группы 3 и открывает элемент И 27, выходной сигнал которого открывает

А-й элемент И второй группы 24, через который содержимое А-ro разряда .КСР 12, через А-й элемент ИЛИ 13 поступает на вход регистра 14.

Определение результата операции (А-B)modP (поступает сигнал шины 30).

По входной шине 16 операнд A в двоич- ном коде через открытые элементы пятой группы И 17, элемент ИЛИ первой группы 23 поступает на вход регистра 11, По выходной шине ?О операнд Ь в двоичном коде через открытые элементы И четвертой группы 21, элементы

ИЛИ 19 второй группы, регистр 1 поступает на вход дешифратора 2, с выхода которого сигнал, соответствующий значению Ь, поступает на первый вход В-ro элемента И первой группы 3.

В данном случае содержимое КСР 12 сдвигается влево на А п разрядов, а выходной сигнал схемы 10 открывает

В-й элемент И первой группы 3 и открывает элемент И 28, .выходной сигнал которого открывает (Р-В)-й эле— мент И седьмой группы 25, через который содержимое (Р-В)-ro разряда KCP 12 через В-й элемент ИЛИ третьей груп1247868 пы 26, элемент ИЛИ 13 поступает на вход регистра 14. формула изобретения

Устройство для сложения и вычитания чисел по модулю Р, содержащее первый и второй входные регистры, дешифратор, генератор импульсов, первый и второй элементы И, умножитель, 10 суммирующий счетчик, схему сравнения, кольцевой сдвигающий регистр, элемент ИЛИ, выходной регистр, первую, вторую, третью и четвертую группы элементов И, первую группу элемен- 15 тов ИЛИ, причем выходы первого входного регистра подключены к входам дешифратора, выходы которого подключены к первым входам соответствующих элементов И первой группы, выходы 20 которых соединены с первыми входами соответствующих элементов И второй группы, вход запуска генератора импульсов является входом запуска устройства, а выход соединен с первыми 2S входами первого и второго элементов И, вторые входы которых подключены к выходу схемы сравнения и к вторым входам элементов И первой группы, выход первого элемента И соединен с входом умножителя, выход которого соединен с входом разрешения кольцевого сдвигающего регистра, выкоды разрядов которого соединены с вторыми входами соответствующих элементов И второй группы, выход второго .элемента И соединен с информационным @ходом суммирующего счетчика, выход которого соединен с первым входом схемы сравнения, второй вход которой соединен с выходом второго входного регистра, информационный вход которого соединен с выходами элементов

ИЛИ первой группы, первые входы которых соответственно соединены с вы- 45 ходами элементов И третьей группы, первые входы которых соединены соответственно с первыми входами элементов И четвертой группы и являются первым информационным входом устройства, вторые входы элементов И третьей и четвертой групп соединены соответственно с входами управления сложением и вычитанием устройства, выход элемента ИЛИ соединен с информационным входом выходного регистра, выход которого является выходом результата устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в устройство введены пятая, шестая, седьмая группы элементов И, вторая и третья группы элементов ИЛИ, третий и четвертый элементы И, причем второй.информационный вход устройства соединен с первыми входами элементов И пятой группы и с первыми входами элементов

И шестой группы, вторые входы элементов И пятой и шестой групп соединены соответственно с входами управления вычитанием и сложением устройства; выходы элементов И пятой группы соединены с вторыми входами элементов ИЛИ первой группы, выходы элементов И шестой группы соединены с первыми входами элементов ИЛИ второй группы, вторые входы которых соединены с выходами элементов И четвертой группы, выходы элементов ИЛИ второй группы соединены с информационным входом первого входного регистра, первые входы третьего и четвертого элементов И соединены соответственно с входами управления вычитанием и сложением устройства, а вторые входы подключены к выходу схемы сравнения, выход четвертого элемента И соединен с третьими входами элементов И второй группы, выход третьего элемента И соединен с первыми входами элементов И ! седьмой группы, вторые входы которых соединены соответственно с выходами . элементов И первой группы, третьи входы элементов И седьмой группы соединены с выходами соответствующих разрядов кольцевого сдвигающего регистра, выходы элементов ИЛИ третьейгруппы соединены с входами элемента ИЛИ, первый и второй входы k-ro элемента ИЛИ третьей группы (где

k = О, (P-1)} соответственно соединены с выходами k-ro элемента И второй группы и k-ro элемента И седьмой группы.

1247868

Составитель М.Есенина

Техред З.Чижмар

Корректор Е . Сир ох ма н

Редактор И.Сегляник

Заказ 4127/49 Тираж 671

ВНИИПИ Государственного коьытета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4