Логическая ячейка

Иллюстрации

Показать всеРеферат

Изобретение относится к импульс ной технике, в частности к лог№1еским элементам. Цель изобретения повьппение быстродействия логического элемента достигается введением третьего источника тока и новыми функциональными связями между транзисторами . Логическая ячейка содержит транзисторы 1,3,6,7 и 8, источники тока 4, 17 и 18, резисторы 14 и 15, шины 2 и 9 опорного напряжения, шину 16 питания. Для согласования уровней логических сигналов сигнал с первого логического входа 5 поступает на базу транзистора 3 через эмиттернмй повторитель. По сравнению с известной логической ячейкой предложенная ячейка обладает более высоким быстродействием при сохранении высокой помехозащигаенности. ил. сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (19) (11) (51) 4 Н 03 К 19/086

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ВСЕСОК)"-" e

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ц,"„ 13

Н А BTOPCHOIVIY СВИДЕТЕЛЬСТВУ висяноти

{54) ЛОГИЧЕСКАЯ ЯЧЕЙКА (57) Изобретение относится к импульсной технике, в частности к логическим элементам. Цель изобретения повьнпение быстродействия логическо(21 ) 3840078/24-21 (22 ) 08. 01 . 85 (46 ) 30. 07 . 86. Бюл. № 28 (72 ) А. П, Голубев, Л. Б. Богод, В.Н.Крылов и О.А.Лупал (53) 621.374 (088.8) (56) Авторское свидетельство СССР

¹ 1200413, кл. Н 03 К 19/086, 1984.

Алексенко А. Г., Шагурин И. И.

Микросхемотехника. M„: Радио и связь, 1982, с. 77, фиг. 2.24, го элемента достигается введением третьего источника тока и новыми функциональными связями между транзисторами. Логическая ячейка содержит транзисторы 1,3,6,7 и 8, источники тока 4, 17 и 18, резисторы 14 и 15, шины 2 и 9 опорного напряжения, шину 16 питания. Для согласования уровней логических сигналов сигнал с первого логического входа 5 поступает на базу транзистора 3 через эмиттерный повторитель. По сравнению с известной логической ячейкой предложенная ячейка обладает более высоким быстродействием при сохранении высокой помехозащишенности.

1 ил.

l 248056

Изобретение относится к импульсной технике, а именно к логическим элементам 30"»I типа.

11елп. изобретения — повышение быстродействия устройства.

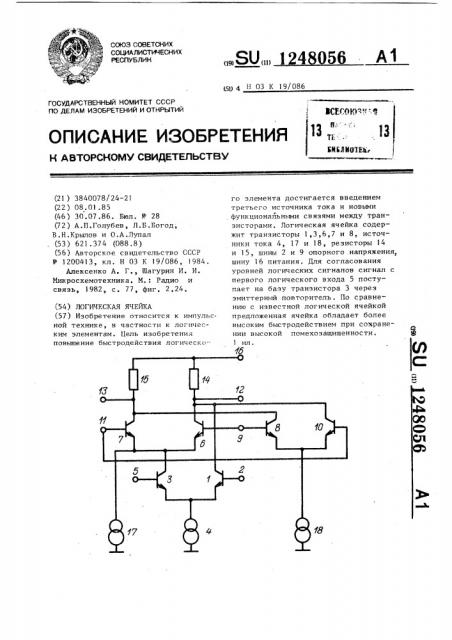

11а чертеже представлена принципиальная схема логической ячейки.

Логическая ячейка содержит первый транзистор l, база которого соединена с первой шиной 2 опорного напряжения, эмиттер соединен с эмиттером второго транзистора 3 и первым источником тока 4, база транзистора 3 подключена к первому входу 5, эмиттери третьего и четвертого транзисторон 6 и 7 подключены к коллектору транзистора 3, бази третьего и и" òîãî транзисторов

6 и 8 соединены с второй шиной 9 опорного напряжения, базы четвертого и шестого транзисторов 7 и 10 .подключены к второму входу ll, коллекторы транзисторон 6 и 7 подключены к первому и второму выходам 12, 13 и через первый и второй резистори 14 и 15 — к шине питания 16, кол1 лекторы транзисторов 6 и 7 соединены с коллекторами транзисторов 10 и 8, коллектор транзистора 1 соединен с коллектором транзистора 6, второй и третий источники тока 17 и 18 подключены к эмиттерам транзисторов 6 и 8.

Логическая ячейка работает следую. щим образом.

При уровне логического сигнала на входе 5, соответствующем уровню логического "0", т.е, ниже напряжения на первой IHHp 2 опорного напряжения ток I источника тока протекает через транзистор 1 и через резистор 14, создавая на выходе 12 сигнал логический "О™ в отсутствие то,а 1 через резистор 14.

В зависимости от уровня логического сигнала на входе 11 ток 1 источ— ника тока 17 будет протекать или через открыть2й транзистор 7 и резистор 15, создавая дополнитель2п2й

СИГНаЛ На НЫХОдЕ 13 Б л ГВы„= 11ллр

-I„R, или через откритый транзис— тор 6 и резистор 14, создавая вместе с током 1„ сигнал U

U — (I + Т ) R на выходе 12. ллп л 2

Таким образом, в зависимости от комбинации сигналов на входах 5, ll и испольэу-емого выхода 12 (13) урон ни логических сигналов на ниходе 12 (13) ячеек будут изменяться для уров;. ня логиче.ской единицы от 11щ, до 01лп IIК д я Уровня логического ип I R д UIIЯ (I1 +I т.е. логический перепад изменяется лл 1!лог,,ллллллс (Т + I ) R долТ1 ллплллллл (r, — Т ) R.

Транзисторы 8 и 10 подключены таким образом, что при любом уровне логического сигнала на входе 11 ток источника тока 18 протекает через резистор, по которому в данный момент не протекает ток источника тока

17. При этом для любой комбинации сигналов на первом и втором логических входах 5 и 11 независимо от используемого выхода уровень логичесуроненл логического "0" Uëîãüû„

= U — (л + Т ) R т.е. логичес ПП -! -2(3) кий перепад всегда одинаков и равен где О,п — напряжение на шине питания 16;

— сопротивление резисторов

14 и 15;

5LI„,à — логический перепад на выходах 12 и 13.

Принцип работы и эффект повышения быстродействия и/или помехозащищенности сохраняется, если: нагрузочные реэис.торы 15 и 14 подключены к шине питания 16 не непосредственно, а через общий резистор; к выходам

35 12 и 13 подключены согласующие эмиттерние повторители; база транзистора 1 является первым логическим входом, а к базе транзистора 3 подключен первый источник опорного нап4л! Рях;ения и/или объединенные базы транзисторов 6 и 8 являются вторым логическим входом, а к объединенным базам транзисторов 7 и 10 подключен второй источник опорного напряжения

45 для согласования уровней логических сигналов сигнал с первого логического входа 5 поступает на базу транзистора 3 через эмиттерный повторитель.

По сраннению с известной логичес5л2 кой ячейкой предложенная логическая ячейка обладает более высоким быстродействием при сохранении достаточно высокой помехоэащищенности. 5Формула изобретения

Логическая ячейка, содержащая дна источника тока, база первого

12480

Составитель А.Янов

Редактор M Бандура Техред N.Ходанич Корректор А.Зимокосов

Заказ 4141/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4 транзистора соединена с первой шиной опорного напряжения, эмиттер соединен с эмиттером второго транзистора и первым источником тока, база второго транзистора подключена кпервому входу, эмиттеры третьего и четвертого транзисторов подключены к коллектору второго транзистора, базы третьего и пятого транзисторов соединены с второй шиной опорного напряжения, базы четвертого и шестого транзисторов подключены к второму входу, коллекторы третьего и четвертого транзисторов подключены к первому и второму выходам и соот56 4 ветственно через первый и второй резисторы — к шине питания, эмиттеры пятого и шестого транзисторов соединены, от л и ч а -ю щ а я с я тем, что, с целью повышения быстродействия устройства, введен третий источник тока, коллекторы третьего и четвертого транзисторов соединены соответственно с коллекторами шестого и пятого транзисторов, коллектор первого транзистора соединен с кол" лектором третьего транзистора, а второй и третий источники тока подключены к эмиттерам третьего и пятого транзисторов.