Устройство для определения @ -экстремальных @ -разрядных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в информационно-вычислительных системах для текущего определения экстремальных значений параметров в процессе их измерения . Целью изобретения является расширение функциональных возможностей путем обеспечения выделения нескольких экстремальных чисел из неограниченного массива. С этой целью в устройство введены 2т межразрядных элементов И, тп элементов равнозначности , ( элементов И сдвига, 2 (т-1) управляющий элемент И, (т-I) элемент НЕ и (т-1) управляющий триггер. Выбранные из массива (т-1) экстремальных чисел записаны в триггеры. С помощью элементов И, элементов равнозначности, разрядных и межразрядных элементов И из этих чисел выбирается минимальное/ максимальное (при поиске (т-1)-го .максимального/минимального числа). Адрес этого числа записывается в управляющих триггерах , а затем, при приеме очередного числа из массива оно замещается путем сдвига числом из соседних триггеров и т. д. В освободившиеся триггеры записывается вновь поступающее число. 1 ил. со (Л СО СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

< 11 4 G 06 F 7 04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3841524/24-24 (22) 11.01.85 (46) 07.08.86. Бюл. № 29 (72) P. Э. Гут, В. В. Егоров, П. В. Маглышев и Е. Ф. Щеглова (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР № 824193, кл. G 06 F 7/04, 1979.

Авторское свидетельство СССР № 1007099, кл. G 06 F 7/08,,1981.

Авторское свидетельство СССР № 983703, кл. G 06 F 7/04, 1981. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

m ЭКСТРЕМАЛЬНЫХ и-РАЗРЯДНЫХ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть использовано в информационно-вычислительных системах для текущего определения экстремальных значений параметров в процессе их измереÄÄSUÄÄ 1249504 А1 ния. Целью изобретения является расширение функциональных возможностей путем обес печения выделения нескольких экстремальных чисел из неограниченного массива.

С этой целью в устройство введены 2m межразрядных элементов И, mn элементов равнозначности, (т — 1) и элементов И сдвига, 2 (m — 1) управляющий элемент И, (т — 1) элемент НЕ и (m — 1) управляющий триггер.

Выбранные из массива (m — 1) экстремальных чисел записаны в триггеры. С помощью элементов И, элементов равнозначности, разрядных и межразрядных элементов И из этих чисел выбирается минимальное/ максимальное (при поиске (m — 1) -ro максимального/минимального числа). Адрес этого числа записывается в управляющих триггерах, а затем, при приеме очередного числа из массива оно замещается путем сдвига числом из соседних триггеров и т. д. В освободившиеся триггеры записывается вновь поступающее число. 1 ил.

1249504

Изобретение относится к вычислительной технике и может быть использовано в информационно-вычислительных системах для текущего определения экстремальных значений параметров в процессе их измерения.

Целью изобретения является расширение функциональных возможностей за счет возможности выделения нескольких экстремаль ных чисел из неограниченного массива.

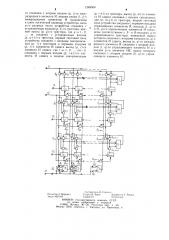

На чертеже приведена схема устройства.

Устройство содержит n><(m+ I ) триггеров I.,, I 2 . ° . 11,m+I> I2,! 2,2 .. 1 12,т+ь ..., 1„ l, l„,2, ..., 1.,„,ч I, и элементов ИЛИ 21-2„, п>((т+!) элементов равнозначности Зь;, 31 2 31 „,, ь 32д, 32,2Ç ..., 32,m+-1 3nд Зп,2i

Зл л,+ь (n — I))<(m+ I) разрядных элеменов

И 42 I, 42 2ь ..., 42 щ ь ..., 4л,ь 4п,2, ", 4л,гл+-1, nX(m+I) межразрядных элементов И 5I I, ol 2з, ..., оп,п ь 52 1, 52,2, -, 52,m+I, -, 5л,ь

5„,, ..., 5„m+I тКи элементов И сдвига 61 I

6l 2> ..., 6l,,. 62l, 622, ..., 62,л, ..., 6„,ь 6п,2>

6л и,, m управляющих триггеров 7 — 7m, 2Xm управляющих элементов И 81- — 8m и 9 — 9л„

m элементов HE 10I 10, входы разрядов числа устройства lll — Ilл, первый и второй тактовые входы 12 и 13, шина 14 логической единицы.

Устройство работает следующим образом.

Значения m экстремальных (пусть для опредсленности) максимальных чисел записаны в триггерах 1:р-й разряд q-ro числа, где р == 1, 2, ..., п, q = 1, 2, ..., m записан в триггере 1,,+ь причем первый разряд является старшим. Если р-е разряды всех чисел равны, то логическая единица будет на выходах всех элементов равнозначности

Зрl — 3p m II Если среди р-х разрядов чисел есть нулевые и единичныс, то на соответствующие элементы равнозначности 3, „поступает единичный (с выхода элемента ИЛИ 2 ) и нулевые сигналы (с инверсного выхода триггера Iр и) . В результате на выходах элементов равнозначности 3р „разрядов тех чисел, которые имеют единичные значения,-логический нуль, который запирает соответству|ощии межразрядный элемент И 5р,„.

Поэтому па входы всех разрядных элементов И 4, I „4 р+ х„, ..., 4.„более младших разрядов того же числа поступает логический нуль, который запирает эти элементы, имитируя максимально возможное число (единицы в разрядах с (р+1)-го по п-й, что соответствует нулям на инверсных выходах триггеров lр и исключает его таким образом из рассмотрения при поиске минимального числа. В результате логическая единица формируется на выходах одного или нескольких межразрядных элементов И 5л л последнего разряда, которые соответствуют тем триггерам ll > — I„>,в которых записано минимальное (или минимальные, в случае равенства нескольких чисел) число. По тактовому сигналу, подаваемому на вход 13 в управляющие триггеры 7л, через элементы

И 8 записывается логическая единица, а в управляющие триггеры 7 (которые соответствуют не минимальному числу или числам) — логический нуль. Затем по входу 12 поступает второй тактовый сигнал, который проходит через элементы И сдвига 611 — б„ь

612 — бл 2, ..., и т. д., вплоть до элементов И сдвига 61 л — б„л, т. е. в соответствующих которым триггерах l I II — 1лл записано минимальное число.

При этом в триггерах I I — I„переписывается число из триггеров I I(Ij — 1, в которые переписывается число из триггеров 1 „2> — 1. „21 и т. д. По тому же тактовому сигналу в триггеры 1 — 1, 1 записывается новое число из массива, поступающее по входам Ill â ll„. Число, записанное в триггерах I I jI — 1„, т. е. минимальное (или самое левое из нескольких равных минимальных чисел) потеряно. Таким образом, в информационных триггерах 1 записаны

m максимальных чисел из обрабатываемого массива, длина которого не ограничена.

При подключении к разрядным элементам И 4 не инверсных, а прямых выходов триггеров 1 устройство выделяет не максимальные, а минимальные числа. Функционирование устройства при этом аналогично.

Формула изобретения

Устройство для определения m экстремальных п-разрядных чисел, содержащее пК(т+1) триггеров, п элементов ИЛИ, (n — 1)(m+1) разрядных элементов И и (m+1)n межразрядных элементов И, причем выход (l,j) -го триггера, где 1 = 1, 2, ..., (т+1) соединен с /-м входом первого элемента ИЛИ, выход (i, j)-го триггера, где

i = 2, 3, ..., п, соединен с первым входом

ii, j)-го разрядного элемента И, выход которого соединен с 1-м входом -го элемента

ИЛИ, второй вход (k, ))-ro разрядного элемента И, где k = 2, 3, ..., п, объединен с первым входом (k, i)-го межразрядного элемента И, выход (l, j)-го межразрядного элемента И, где 1 = 1, 2, ..., (n — 2), соединен с первым входом (1+1, 1 ) -r o межразрядного элемента И, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности выделения нескольких экстремальных чисел из неограниченного массива, в него введены п®т+1) межразрядных элементов И п(т+1) элементов равнозначности, mn элементов И сдвига, 2m управляющих элементов И, m элементов НЕ и m управляющих триггеров, причем выход (1, !)-ro триггера соединен с первым входом (1, j)-ro элемента равнозначности, выход (i, j)-го разрядного элемента И соединен с первым входом (i, j)-го элемента равнозначности, выход р-го элемента ИЛИ, где р= l, 2, ..., и, соединен с вторыми входами (р, !), (р, 2), ..., (р, т+1)-х элементов равнозначности, выход (р, j)-го элемента равнозначнос1249504

Составитель В. Горохов

Редактор A. Ворович Техред И. Верес Корректор L. Рошко

Заказ 4325/49 Тираж 67! Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

3 ти соединен с вторым входом (р, /)-го межразрядного элемента И, первые входы (1, /)-х межразрядных элементов И подключены к шине логической единицы устройства, вход р-го разряда числа устройства соединен с установочным входом (p, 1)-ro триггера, прямой выход (р, q)-го триггера, где q = I, 2, m соединен с установочным входом (р, q+1)-го триггера, первый тактовый вход устройства соединен с входами синхронизации (р, 1)-х триггеров и первыми входами (р, 1)-х элементов И сдвига выход (p, r)-го элемента И сдвига, где г = !, 2, ..., (m — 1) соединен с первым входом (р, г+1)-го элемента И сдвига и входом синхронизации (р, г+1)-го триггера, выход (р, т)-го элемента И сдвига соединен с входом синхронизации (р, т+1)-го триггера, второй тактовый вход устройства соединен с первыми входами управляющих элементов И, выходы (I q)-го и (2, q)-го управляющих элементов И соединены соответственно с S- u R-входами q-ro управляющего триггера, инверсный выход которого соединен с вторыми входами (р, д)-х элементов И сдвига, выход (n, q)-го межраз10 рядного элемента И соединен с вторым входом (1, q)-го управляющего элемента И и с входом q-го элемента НЕ, выход которого соединен с вторым входом (2, q)-го управляющего элемента И.