Устройство для вычисления функций вида @ и @ @

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и нредназначено для вычисления понарных нроизведений функций вида Uslna и Ucosa по алгоритму Волдера. Устройство содержит т последовательно соединенных итерационных блоков, состоящих из трех сумматоров-вычитателей и ПЗУ, блок сдвига входной информации, элемент ИЛИ-НЕ, блок инверсии аргумента, блок формирования знака функций, блок сдвига, первый и второй блоки выдачи информации и соответствующие связи. При этом блок инверсии аргумента состоит из т-1 параллельных схем свертки по модулю 2 и соответствующих связей. Кроме того, блок формирования знака функций содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и соответствующие связи, в данном устройстве повышение быстродействия осуществляется за счет сокращения на (п - т) последовательно соединенных итерационных блоков. Предлагаемое устройство может быть использовано в устройствах цифровой фильтрации при реализации алгоритма Волдера. 3 ил. sg (Л Ю 4 СО ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (u 4 б 06 1 7/548

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3767306/24-24 (22) 20.07.84 (46) 07.08.86. Бюл. № 29 (72) А. П. Мартынов и Ю. П. Гнучев (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 546890, кл. G 06 F 7/544, 1973.

Авторское свидетельство СССР № 813421, кл. G 06 F 7/548, 1978. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ФУНКЦИИ ВИДА Using и Uco (57) Изобретение относится к вычислительной технике и предназначено для вычисления попарных произведений функций вида Usinn и Ucosa, по алгоритму Волдера. Устройство содержит т последовательно соединенных итера ционных блоков, состоящих из трех

Я0„„1249511 А 1 сумматоров-вычитателей и ПЗУ, блок сдвига входной информации, элемент ИЛИ-НЕ, блок инверсии аргумента, блок формирования знака функций, блок сдвига, первый и второй блоки выдачи информации и соответствующие связи. При этом блок инверсии аргумента состоит из т — 1 параллельных схем свертки по модулю 2 и соответствующих связей. Кроме того, блок формирования знака функций содержит первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и соответствующие связи. В данном устройстве повышение быстродействия осуществляется за счет сокращения на (n — и) последовательно соединенных итерационных блоков. Предлагаемое устройство может быть использовано в устройствах цифровой фильтрации Я при реализации алгоритма Волдера. 3 ил.

1249511

Предлагаемое изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой фильтрации сигналов при реализации алгсритмов дискретного преобразования Фурье или быстрого преобразования Фурье.

Целью изобретения является повышение быстродействия устройства.

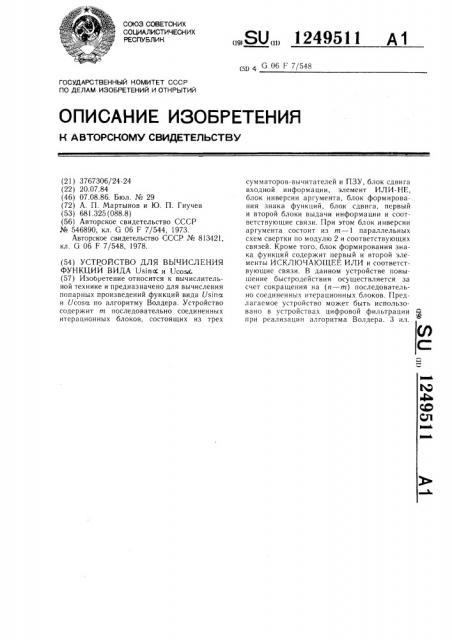

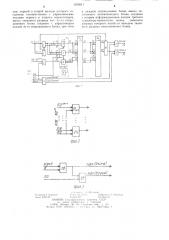

На фиг. 1 приведена струкгурная схема устройства для вычисления фу нкций вида

Us1na. и Uc0sa; на фиг. 2 — функциональная схема блока инверсии аргумента; »а фиг. 3-функциональная схема блока формирования знака функций.

Устройство содержит блок 1 сдвига входной информации, элемент ИЛИ-НЕ 2, блок 3 инверсии аргумента, блок 4 формирования знака функций, m операционных блоков 5 -5„,, каждый из которых содержит первый, второй и третий сумматоры-вычитатели 6 — 8, постоянное запоминающее устройство 9, блок 10 сдвига, первый и второй коммутаторы 11 и 12, п-разрядная информационная шина 13, шина 14 текущего значения аргумента, итерационные блоки имеют информационные входы 15 — 18, управляощкй вход итерационных блоков 19 и информационный вход 20, а также информационные выходы итерационных блоков 21 — 23, выход знакового разряда операционного блока 24, выходы вычисленных значений функций 25 и 26.

Блок 3 инверсии аргумента содержит т -1 схем свертки по модулю 2 27 --27. ь Блок 4 формирования знака функции содержит первый и второй элементы ИСКЛ1ОЧАЮ1ЦЕЕ

ИЛИ 28 и 29.

Работа устройства основана на решении системы HTcpaH,èoníûx уравнений вида

a. yi = a,— signa; агс®2

1 у,, — — у, --signer.;-хг2

I х, =- х,+signa,.(Ü-2 гдеi = — 0,1 и.

Начальные условия: Q!> =-= сс/„у > == О, xp= U.

По окончании итерационного процесса величины у„и х„приобретают соответственно значения Usina, и Ucosa>, Устройство работает следующим образом.

На вход блока 1 сдвига входной информации (фиг. 1) с и-разрядной информационной шины 13 поступает код входной величины U, а на вход элемента ИЛИ-НЕ -- старшис разряды этой величины. Б>лок 1 сдвига информации (например, и парал.г.ельных схем мультиплексоров) осущес; вляет коммутацию кода входной величины U без сдвига, либо со сдвигом влево на и — m разрядов в зависимости от команды, поступающей от элемента ИЛИ-НЕ. В последнем случае производится дополнение освободи вш ихсн в результате сдвига младших разрядов нулями. Команда сдвига, поступающая на управляющие входы блока 1 сдвига входной информации и блока 10 сдвига, вырабатывается элемегг.-ом ИЛИ-НЕ при отсутствии единиц в п — m старших разрядах входной величины U. С инверсного выхода блока 1 сдвига входной информ а ци и п-разрядный код поступает на первый вход первого сумматора-вычитателя 6 и с дополнительным сдвигом на один разряд вправо, достигаемым за счет соответствующего соединения линий связи, — на втсрой вход второго сумматора-вычитателя 7, а с прямого выхода— на первый вход второго сумматора-вычита1О теля 7 и с дополнительным сдвигом вправо на один разряд — на второй вход первого сумматора-вычитателя 6 первого блока 5ь

Г1оследовательно соединенные сумматоры-вычитатели 6 и 7 блоков 51 — 5m выполняют соответственно следующие уравнения:

1.> у, = у; — signa,-х 2 х;: = x,+signa,;у; 2 где = 1, 2, ..., т.

Управление сумматорами-вычитателями

6 -8 i-го блока осуществляется знаковым разрядом третьего сумматора-вычитателя 8 (! — 1)-го блока. Посл довательно соединенные сумматоры-вычитатели 8 блоков 5 — 5, производят вычисления в соотвтствии с уравнением

25 а;+1 = а; — signa,, arctg2

Значение константы afctg2, поступаюгцей на второй вход сумма:ора-вычитателя 8!-го итерационного блока, выбирается из постоянного запоминающего устройства 9 соответствующего блока 5,.

Число итерационных блоков (итераций)

m определяется исходя из заданной относительной погрешности г> по выражению, Гт+16 2rm — и — 22 2!„m)2

24 3 U-где U" . -- минимальное значение кода входной вел и ч -. н ы.

Управление сумматорами-вычитателями

6--8 первого операционного блока 5i производится непосредственна разрядом л/4 с шины 14 текущего значения аргумента, тем самым вычисление функций в операционных блоках 51 5 осуществляется в пределах значений углов от 0 до л/2, в соответствии с кодом текушего угла, поступающего по разрядам л/8- л/2 + от шины 14 текущего значения аргумента через блок 3 инверсии аргумента на первый вход третьего сумматора-вычитателя 8 первого блока 5ь Для обеспечения вычисления функций при любых

S0 произвольных значениях текущего угла слу>кат блок 3 инверсии аргумента и блок 4 формирования знака функций. Блок 3 инверсии аргумента (фиг. 2) состоит из т — 1 параллельных схем свертки по модулю 2

27! --27 п вторые входы которых объединены и подключены к эазряду л/2 шины 14 текущего значения аргумента, что обеспечивает получение инверсных значений теку;цего угла, задаваемого разрядами л/8

1249511

Формула изобретения

Х/2 ", и ри задании текущего угла в интервале от л/2 до л и от Зл/2 до 2л. Блок формирования знака функций (фиг. 3), состоящий из двух элементов ИСКЛЮЧАЮ1ЦЕЕ ИЛИ 28 и 29, производит преобразование информации, содержащейся в разрядах л/2 и л текущего значения аргумента и знаке входной величины sign U, в команды управления коммутаторами 1 и 12 в соответствии с логическими выражениями

sign(Us!no:) = л sign U + л.sign U

sign(Ucosn) = К/2.sign(Usin(7) +

+>т/2s gn(Us па).

Коммутаторы 11 и 12 (например, и параллельных схем свертки по модулю 2, аналогичных устройству блока 3 инверсии аргумента) в зависимости от поступающих на них команд производят выдачу вычисленных функций, приходящих на их входы от блока IO сдвига, на выходные шины 25 и 26 в прямом или обратном кодах. Блок 10 сдвига (например, параллельные схемы мультиплексоров) производит коммутацию вычисленных значений функций, поступающих ,с информационных выходов 21 и 22 m-ro итерационного блока 5„, без сдвига либо со сдвигом вправо íà n — т разрядов в зависимости от команды сдвига, поступающей от элемента ИЛИ-НЕ 2.

Таким образом, предлагаемое устройство для вычисления функций вида Using(u

Ucosv. при заданной относительной погрешности позволяет существенно повысить быстродействие по отношению к известному устройству за счет сокращения последовательно соединенных итерационных блоков на число и — m; исключения первого итерационного блока 1 = О, что достигается соответствующим заданием информации на сумматоры-вычитатели итерационного блока 51 (1=

= 1) и управления ими разрядом тс/4 текущего значения аргумента; уменьшения разрядности третьего управляющего сумматоравычитателя итерационных блоков, при этом устройство фактически работает только в интервале от 0 до л/4, а вычисление функций для любого заданного аргумента производится за счет управления блоками инверсии аргумента и выдачи информации.

Устройство для вычисления функций вида Using и Ucosn, содержащее т операционных блоков (где m определяется заданной относительной погрешностью), каждый из которых содержит три сумматоравычитателя, причем первый и второй информационные входы каждого операционного блока соединены соответственно с первым и вторым информационными входами первого сумматора-вычитателя, третий и четвертый информационные входы каждого опера5

55 ционного блока соединены cooTBe1«TB«HHo с первым и вторым информационными входами второго сумматора-вычитателя, пятый информационный вход каждого операционного блока соединен с первым информационным входом третьего сумматора-вычитятеля, информационные выходы первого, второго и третьего сумматоров-вычитателей являются соответ«тв«нно первым, вторым и третьим выходами каждого операционного блока, первый информационный выход (771 1) -гo операционного блока соединен с первым и четвертым информационными входами 7п-гo операционного блока, второй информационный выход (rn 1)-ro операционного блока соединен с вторым и третьим информационными входами т-го операционного блока, третий информационный выход (m — 1) -го операционного блока соединен с пятым информационным входом 771-го операционного блока, отлина(ои(еегя тем, что, с целью повышения быстродействия, в него введены блок сдвига входной информации, блок инверсии аргумента, блок формирования знака функции, элемент ИЛИ-НЕ, блок сдвига, а в каждый операционный блок введен постоянный запоминаюгций блок, первый и второй коммутаторы, прич«м вход коэффициента устроиствя со«диllен с информационным входом блока сдвига входной информации, инверсный выход которого соединен с первым информационным входом и со сдвигом на один разряд в сторону младших разрядов с четвертым информационным входом первого операционного блока, прямой выход блока сдвига входной информации сосди11«н со сдвигом па один разряд в сторону мла IIIIHx разрядов с вторл(м информационным входом и с третьим информационным BxojoM 11срвого операционного блока, входы с 771 по и (и -- разрядность аргумента) разрядов входа коэффициента устройства соединены с Bx(5 дами элемента ИЛI)-НЕ, выход которого «оединен с входами управления сдвигом блока сдвига входной информации и блока сдвига, входы с л/8 по:т/2" + разрядов аргум«нтя устройства соединены с пнформацио 11ым б loK2 Hнв«р«ин ярr>м«нт;1, ля1ощий вход которого соединс и с рязря;спым входом т/2 р;1зрядя аргумента устройства, вход л/4 разряда арго мента устройств<1 ???????????????? ?? ?????????????????????? ???????????? ?????????????? oiip???????????????????? ??????????, ???????????? ?? ???????????? ??????????m??????o??h??????????o???? ??l-??o ????????????????????o???? ????o???? ?????????????????? ???????????????????????????? ?????????????? ???????????? ?????????? l??????????????????>хо;(ями 6.ц1кя сдвига. первый и второй выхо.сы которого соединены соответственно «информационными входами первого и второго коммутаторов, BbIxoJû котор:1х со«днн«ны соответ«твен(ю с первым H в.-орым выходямп вычисл«нных значений функций, входы разрядов л/2, п и знаковый яргуме:1т устройства сос дин«1(ы соответственно с п«рвым, вторым и третьим входами блока формирования знака функ1249511,7f

gs

i7Б

COS a

7Б

7<4

<< у-/ 77<< 7

Ф. Г

ri7 ) 1 л

„;L @77 77ЫГ//7 ()

-3ь н "<< < I I i

Редактор 7< 11ороиин 1с,1<., 11 . 1«<к Коррс<.<о;< << (Хбр< нар

Лакан 4325,4Н Тир«û б I I!одни< но<

ВНИИПИ Государс;,<;!«» . ко«<итета СССР

113035, Мосина, Ж- 35, I-,:ë и<скан наб, .<. 4<5

Филиал П11П «11гтент., <У,:л:. .и р >,<, ул Проект«аи, 4 ции, первый и второй выходы которого соединены соответственно с управляющими входами первого и второго ком мутаторов, выход знакового разряда (т 1)-го операционного блока соединен с управляющим входом т-го операционного блока, при этом в каждом операционном блоке выход постоянного запоминающего блока соединен с вторым информационным входом третьего сумматора-вычитателя, выход знакового разряда которого является выходом знакового разряда операционного блока. г ---" .;- с7- ур / JegSu ) ..3

:!<