Устройство для контроля передачи информации

Иллюстрации

Показать всеРеферат

Изобретение относиться к вычислительной технике, в частности к системам передачи данных, и может быть использовано для ввода информации в ЭВМ. Цель изобретения - повьниение достоверности контроля передачи информации . С этой целью в устройство, содержащее блок приема информации, блок буферной памяти, блок контроля, ренерсивный счетчик, первый счетчик повторений ввода информации шифратор, триггер, элемент И и элемент ИЛИ, введены второй счетчик повторений ввода информации, второй элемент ИЛИ, элемент запрета и три элемента И. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (11) (51) 4 6 06 F 11/10, 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3837954/24-24 (22) 02.0.1.85 (46) 07.08.86. Бюл № 29 (72) А.Ю.Лапин, Л.В.Лычев и В.Г.Утенков (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 378832, кл. С 06 F 3/04, 1973.

Авторское свидетельство СССР

¹ 544958, кл. G 06 F 3/04, 1977. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике, в частности к системам передачи данных, и может быть использовано для ввода информации в

ЭВМ. Цель изобретения — повьниение достоверности контроля передачи ин" формации. С этой целью в устройство, содержащее блок приема информации, блок буферной памяти, блок контроля, ренерсивный счетчик, первый счетчик повторений ввода информации шифратор, триггер, элемент И и элемент ИЛИ, введены второй счетчик повторений ввода информации, второй элемент

ИЛИ, элемент запрета и три элемента

И. 1 з.п. ф-лы, 3 ил.

1249520

Изобретение относится к области вычислительной техники, в частности к системам передачи данных, и может быть испопьзовано, например, для ввода информации в ЭВМ.

Цель — изобретения повышение достоверности контроля передачи информации.

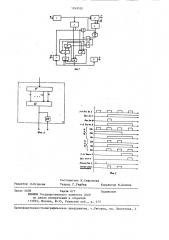

На фиг. 1 изображена структурная схема устройства; на фиг.2- схема блока контроля; на фиг. 3- временная диаграмма работы устройства при формировании двух перезапросов.

Устройство содержит блок 1 приема информации, блок 2 буферной памяти, блок 3 контроля, реверсивный счетчик

4, элемент 5 запрета, триггер 6, первый 7 и второй 8 счетчики повторений ввода информации, шифратор 9, первый

10, второй 11, третий 12, четвертый

13 элементы И, первый 14 и второй 15 элементы ИЛИ.

Информация поступает в устройство по линии 16, а считывается в 3ВМ по линии 17 при поступлении сигнала, разрешающего считывание по линии 18.

По линии 19 на передающее устройство выдается перезапрос, а на шину 20 сигнал об отсутствии канала (линии) связи.

Блок 3 контроля содержит регистр

21, сумматор 22 и элемент НЕ 23.

Устройство работает следующим

3 образом.

В исходнои состоянии счетчики 7 и 8 находятся в нулевом состоянии, при этом на первом выходе счетчика

8 имеется сигнал, который через элемент ИЛИ 15 поступает на второй вход элемента И 12. Триггер 6 находится в нулевом состоянии, при которои на его первом выходе имеется сигнал

"0", и элемент 5 запрета открыт. С линии 16 на блок 1 поступает информация. В блоке 3 повторяется правильность приема, например, по четности.

Если ошибки нет, то на втором выходе блока 3 появляется сигнал отсутствия ошибки, через открытый элемент 5 передающийся в блок 2 буферной памяти и разрешающий запись информации в блок 2, которая затеи по сигналу, поступающему по линии 18, может быть считана, например, в 3ВМ. Счетчик 4 обеспечивает подсчет пачек информации, записанных в блок 2 и считанных в ЭВМ, определяя тем самым заполнение блока 2 буферной памяти. Если

I5

55 на выходе счетчика 4 сигнал отсутствует, то перезапрос не формируется и в следующем такте в блок 1 поступает новая информация.

Если при приеме информации обнаружена ошибка, на первом выходе блока 3 появляется сигнал, который через элемент ИЛИ 14 поступает на вход шифратора 9 и считанный вход счетчика 7. На выходе .пифратора 9 формируется сигнал перезапроса, а счетчик

7 подсчитывает число перезапросов.

Запись информации в блок 2 в этом случае не производится. В ответ на перезапрос в следующем такте на вход блока 1 поступает "старая" информация, которая подвергается обработке в рассмотренном порядке до тех пор, пока не произойдет правильный прием информации. В этом случае она будет записана в блок 2, а счетчик 7 сигналом, поступающим на его первый вход, будет установлен в исходное состояние. Повторение перезапросов продолжается до тех пор, пока не превысит заданного числа n, на которое рассчитан счетчик 7. При этом на его выходе формируется сигнал неисправности.

В ходе приема правильной информации счетчик 4 проверяет заполнение блока 2 буферной памяти по заданному условию, например, по условию заполнения половины ячеек. В этом случае, т.е, при выполнении этого условия, на выходе счетчика 4 формируется сигнал заполнения, который поступает на вход элемента И 10.

При этом, если очередной цикл приема прошел без ошибки, то сигналом со второго выхода блока 3, прошедшим через элемент 5, информация записывается в блок 2, а этим же сигналом прошедшим через элемент И 10, триггер

6 перебрасывается в единичное состояние. Сигнал с первого выхода триггера

6 закрывает элемент 5 и поступает на первые входы элементов И 12 и 13. На выходе элемента И 12 появляется сигнал, который, пройдя через элемент

ИЛИ 14, формирует сигнал перезапроса и подсчитывается счетчиком 8 ° Устройство переходит в режим дополнительных перезапросов, формирующихся при повторном приходе информации, которая, однако, в блок 2 не записывается, -.àê как элемент 5 закрыт. После формирования и перезапросов появляется

12495?0

40 сигнал »а (и+1) †ом выходе второго счетчика, а сигнал на втором входе элемента И 12 пропадает. При приходе очередной правильной повторной комбинации перезапрос не формируется и она не записывается в блок 2. При этом на выходе элемен-,à И 11 появляется сигнал, по обратному фронту которого триггер 6 перебрасывается в нулевое состояние, элемент 5 открывается, подготавливая устройство к приему новой комбинации, а счетчик

8 сбрасывается в исходное состояние.

Ф о р м ул а и з о б р е т е н и я

1. Устройство для контроля передачи информации, содержащее блок приема информации, блок буферной памяти, реверсивный счетчик, триггер, первый элемент И, первый элемент

ИЛИ, первый счетчик повторений ввода информации, шифратор, блок контроля, причем вход блока приема информации подключен к информационному входу устройства, выход блока приема информации соединен с информационными входами блока буферной памяти и блока контроля, первый выход блока контроля соединен с первым входом первого элемента ИЛИ, выход которого подключен к входу шифратора, выход которого является выходом сигнала повторения ввода информации в устройство, выход блока буферной памяти является информационным выходом устройства, вход считывания блока буферной памяти объединен с входом управления счетом реверсивного счетчика и подключен к входу разрешения считывания устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в устройство введены второй элемент ИЛИ, второй счетчик повторений ввода информации, второй, третий и четвертый элементы И и элемент запрета, причем единичный и нулевой входы триггера соединены соот5

l5

25 ветственно с выходами первого и второго элементов И, первый вход первого элемента И соединен с выходом переполнения второго счетчика повторений ввода информации, информационные выходы которого подключены к соответствующим входам второго элеме»та

ИЛИ, выход которого соединен с первым входом третьего элемента И, второй вход которого объедине» с входом сброса первого счетчика повторений ввода информации, первым входом элемента: запрета, вторым входом второго элемента И, первым входом четвертого элемента И и подключен к второму выходу блока контроля, второй вход элемента запрета объединен с третьим входом третьего элемента И, вторым входом четвертого элемента И и подключен к прямому выходу триггера, инверсный выход которого подключен к входу сброса второго счетчика повторений ввода информации, третий вход четвертого элемента И объединен со счетным входом первого счетчика повторений ввода информации и подключен к выходу первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, выход элемента запрета соединен с входом разрешения записи блока буферной памяти и первым входом первого элемента И, второй вход которого-соединен с выходом реверсивного счетчика, выход переполнения первого счетчика повторения ввода информации является выходом признака неисправности устройства.

2. Устройство IID II ° 1, o T JI H ч а ю щ е е с я тем, что блок контроля содержит регистр, сумматор по модулю два и элемент НЕ, причем выходы разрядов регистра подключены к соответствующим входам сумматора по модулю два, выход которого соединен с входом элемента НЕ и является первым выходом блока, выход элемента

НЕ и вход регистра являются соответственно вторым выходом и входом блока.1249520

I и»

Иг

Вйа.

И-й, &gee. У

Ь. жи и

>e vn /A 2

Сыма дюра. люргЮвтрюса

Составитель И.Сафронова

Техред Г.Гербер Корректор M.Äåì÷èê

Редактор Н.Егорова

Заказ 4638 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãîðoä, ул. Проектная, 4