Модульная многоуровневая система коммутации процессоров

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет сократить временные затраты при поиске свободного процессора в многопроцессорной вычислительной системе. Система 1 коммутации процессоров состоит из совокупности коммутационных модулей 2, расположенных на нескольких уровнях, и терминальных модулей 3, предназначенных для организации взаимодействия через систему 1 между процессами, реализуемыми в процессоре 4 данного терминального модуля 3, и процессами в других процессорах. Поиск свободного процессора и одновременное установление логического канала к нему осуществляется децентрализованно коммутационными модулями 2 на .основании служебной информации , имеющейся в каждом из них и динамически отображающей наличие в текущий момент свободных процессоров. 1 З.П., ф-лы, 12 ил. (Л ;о ел ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

9524 А 1 (19) (11) (59 4 G 06 F 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3786222/24-24 (22) 24.08.84 (46) 07.08.86. Бюл. У 29 (7 1) Ленинградский институт авиационного приборостроения (72) С.В.Горбачев (53) 681.325 (088.8) (56) Прангишвилли И.В. и Стецюра Г.И.

Микропроцессорные системы. М.: "Наука", 1980, с. 194.

Авторское свидетельство СССР

М 9837 14, кл. G 06 F 15/16, 1982.

Авторское свидетельство СССР

В 962965, кл. G 06 F 15/16, 1982. (54) МОДУЛЬНАЯ МНОГОУРОВНЕВАЯ СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ (57) Изобретение относится к вычислительной технике и позволяет сократить временные затраты при поиске свободного процессора в многопроцессорной вычислительной системе. Система 1 коммутации процессоров состоит из совокупности коммутационных модулей 2, расположенных на нескольких уровнях, и терминальных модулей 3, предназначенных для организации взаимодействия через систему 1 между процессами, реализуемыми в процессоре 4 данного терминального модуля 3, и процессами в других процессорах.

Поиск свободного процессора и одновременное установление логического канала к нему осуществляется децентрализованно коммутационными модулями 2 на ..основании служебной информации, имеющейся в каждом из них и динамически отображающей наличие в текущий момент свободных процессоров.

1 з.п., ф-лы, 12 ил.

1 1

Изобретение относится к вычислительной технике и может найти применение при создании надежных и высокопроизводительных многопроцессорных вычислительных систем.

Целью изобретения является повышение производительности эа счет увеличения пропускной способности при уменьшении временных затрат на управление межпроцессорными взаимодействиями.

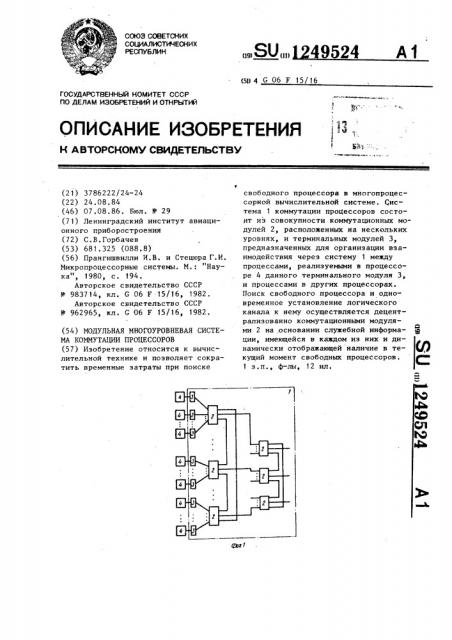

На фиг. 1 приведен пример структурной схемы модульной многоуровневой системы коммутации процессоров; на фиг. 2 — структурная схема коммутационного модуля," на фиг. 3 — струк турная схема терминального модуля на фиг. 4 — пример реализации функциональной схемы операционного блока модулей; на фиг. 5 — пример реали" эации структурной схемы приоритетного блока, на фиг. 6 — пример реализации блока ввода-вывода модулей; на фиг. 7 — временные диаграммы работы операционного блока, на фиг.8i2 — алгоритмы функционирования системы коммутации процессоров °

Система 1 коммутации процессоров содержит коммутационные модули 2, терминальные модули 3,, процессоры

4 (фиг. 1).

Коммутационный модуль содержит операционный блок 5, блок 6 памяти, блоки 7.1,...,7.п хранения идентификаторов логических каналов, блоки 8.1,...,8. хранения индикаторов процессоров, приоритетный блок 9, блоки 10.1,...,10.а ввода-вывода, шину 11 адреса, шину !2 управления, шину 13 данных, каналы 14 . 1,..., 14.и связи (фиг, 2).

Терминальный модуль 3 содержит операционный блок 15, блок 16 памяти, блок 17 хранения идентификаторов логических каналов, блок 18 хранения индикаторов процессоров, приоритетный блок 19, два блока 20.1, и 20.2 ввода-вывода, шину 21 адреса, шину 22 управления, шину 23 данных, входы-выходы 24.1 и 24.2 терминального модуля 3 (фиг. 3).

Операционный блок 5(15) содержит регистр 25 микропрограммного адреса, блок 26 хранения микропрограмм,коммутатор 27 микропрограммного адреса, коммутатор 28 адреса ветвления, регистр 29 микрокаманды, арифметикологический блок 30, регистр 31 ре249524 2 эультата, регистр 32 адреса, дешифратор 33 записи, коммутатор 34 данных, коммутатор 35 базового адреса, регистр 36 селекции, генератор 37 синхроимпульсов (фиг. 4).

Приоритетный блок 9(19) содержит регистр 38 свободных идентификаторов, приоритетную 39 схему, шифратор 40 индентификатора логического канала, группу 41 элементов НЕ, первую группу 42 элементов И, коммутатор 43 идентификаторов, группу 44 элементов ИЛИ, дешифратор 45 идентификатора, второй буферный усилитель 46, вторую группу 47 элементов И (фиг. 5).

Блок 10(20) ввода-вывода содержит выходной регистр 48, входной регистр 49, регистр 50 управления выдачей, регистр 51 управления приемом, дешифратор 52 адреса, третью группу 53 элементов И, коммутатор 54 входной информации, третий буферный

25 усилитель 55 (фиг. 6).

На фиг. 7 А — диаграмма на выходе генератора 37 синхроимпульсов, Б — диаграмма на выходе регистра 25 микропрограммного адреса;  — диаграмма на выходе блока 26 хранения микропрограмм; à — диаграмма на выходе регистра 29 микрокоманды; Д— диаграмма на выходе дешифратора 33 записи.

Модульная многоуровневая система

1 коммутации может обеспечивать вза.имодействие произвольного числа М процессоров 4, разделенных на группы по процессоров в каждой группе.

Отдельный процессор 4 предназначен для выполнения различных операций необходимых для реализации вычислительного процесса в многопроцессорчой вычислительной системе, и может представлять собой универсальную электронную вычислительную машину (микро-ЭВИ). Каждая группа из v процесссров через соответствующие терминальные модули 3 соединена с соответствующим коммутационным модулем

2 через каналов связи. Все коммутационные модули 2 соединены между собой таким образом, что образуют

" -уровневую структуру межсоединений.

Коммутационные модули 2 обеспечи55 вают поиск свободных процессоров 4 в системе, установление логических ка-. чалов связи между процессорами 4 и перецачу информации по логическим

9524

3 124 каналам связи между любой парой абонентов (процессоров 4) системы 1 коммутации. Каждый коммутационный модуль 2 имеет каналов, из которых (и-г) в коммутационном модуле 2 первого уровня используются для соединения с другими коммутационными модулями 2. В общем случае коммутационный модуль 1 -ro уровня (=1,N) соединен через, L и каналов связи 1б (h=г+1+К) с различными коммутационными модулями соответственно (i -1)— го, 1 -го .и (i + 1)-ro уровней . Пример модульной системы 1 коммутации процессоров с трехуровневой структурой межсоедииений коммутационных модулей

2 приведен на фиг. 1.

Терминальный модуль 3 предназначен для органиэации взаимодействия через систему 1 коммутации между про-. 20 цессами, реализуемыми в подключенном к данному терминальному модулю 3 процессоре 4, и процессами, порожден.ными в других процессорах 4. Терминальный уровень 3 имеет два входавыхода,,с помощью первого иэ них он соединен со входом-выходом процессора 4, а ко второму подключен канал одного из коммутационных модулей 2 первого уровня. 30

Коммутационный модуль 2 (фиг ° 2) включает операционный блок 5, который предназначен для логической обработки принимаемой модулем 2 информации, а также обеспечивает управление остальными блоками модуля

2. Вход-выход операционного блока 5 соединен через двунаправленную шину

13 данных со входами-выходами всех остальных блоков модуля 2. Адресный выход операционного блока 5 соединен с шиной 11 адреса, к которой подключены адресные входы блока 6 оперативной памяти, всех блоков 7 хранения идентификаторов, всех бло-. ков 8 хранения индикаторов процессоров, приоритетного блока 9 и всех блоков 10 ввода-вывода. Управляющий выход операционного блока 5 соединен с шиной 12 управления, к которой подключены управляющие входы всех блоков модуля 2.

В состав однонаправленной шины

12 управления входят следующие управляющие одноразрядные линии: — линии 56.1,...,56.п селекции одноименных блоков 10. 1, ..., 10. и ввода-вывода, соединенные с управляющими входами соответствующих блоков 10; — линия 57 селекции памяти, соединенная с управляющим входом блока

6 памяти „ — линия 58 селекции блоков хранения идентификаторов, соединенная с управляющими входами всех блоков

7 хранения идентификаторов логических каналов; — линия 59 селекции блоков хранения индикаторов процессоров, соединенная с управляющими входами всех блоков 8 хранения индикаторов процессоров, — линия 60 селекции приоритетного блока, соединенная с управляющим входом приоритетного блока 9; — линии 61 и 62 чтения и записи, — линии 63 управления узлами приоитетного блока.

Двунаправленную шину 13 данных можно представить в виде совокупности следующих однонаправленных шин, которые обеспечивают четкое представление о характере взаимодействия блоков модуля. . — информационная шина 64, соединяющая вход-выход операционного бло" ка 5 с входами-выходами блока 6 памяти, блоков 7 хранения идентифика.торов логических каналов, блоков 8 хранения индикаторов процессоров, приоритетного блока 9 и блоков 10 ввода-вывода и обеспечивающая передачу данных из операционного блока

5 во все другие блоки модуля; — шина 65 данньж памяти, соединяющая вход-вь ход блока 6 памяти со входом-выходом операционного блока 5 и .предназначенная для передачи данных, хранящихся в памяти в операционный блок 5 — шина 66 передачи индентификаторов, соединяющая входы-выходы блоков 7 хранения идентификаторов логических каналов со входом-выходом операционного блока 5 и обеспечивающая передачу кодов идентификаторов в операционный блок 5; — шина 67 передачи индикаторов, соединяющая входы-выходы блоков 8 хранения индикаторов процессоров со входом-выхоДом операционного блока

5 и обеспечивающая передачу кодов индикаторов в операционный блок 5, — шина 68 передачи кодов свободных идентификаторов, соединяющая вход-выход приоритетного блока 9

1249524 со входом-выходом операционного блока 5 и обеспечивающая передачу двоичных кодов выделенных.идентификаторов в операционный блок 5;

S — шина 69 передачи входной информации, соединяющая входы-выходы блоков 10 ввода-вывода со входом-выходом операционного блока 5 и обеспечивающая передачу в операционный 1Î блок 5 входной информации, полученной блоком 10 извне.

Блок 6 памяти обеспечивает хранение программ и данных, в том числе и буферируемых данных, принятых извне.

Блоки 7 хранения идентификаторов обеспечивают запоминание идентификаторов, которые используются при передаче по установленным ранее логи- 20 ческим каналам связи через данный модуль 2 информации между парами взаимосвязанных таким образом терминальных модулей. Число блоков 7 соответствует числу физических кана- 25 лов данного коммутационного модуля

7. Емкость каждого из блоков 7 определяется числом логических каналов связи, которые можно установить через данный модуль 2. 30

Блоки 8 хранения индикаторов процессоров используются для хранения служебной информации, обеспечивающей поиск свободных процессоров 4 различных типов, подключенных к системе 1 коммутации, по соответствующему физическому каналу связи, Емкость блока, 8 определяется числом типов процессоров 4. Разрядность каждрй ячейки каждого блока 8 равна единице. Число блоков .8 равно п., Приоритетный блок 9 предназначен для выделения свободного в данном коммутационном модуле 2 идентификатора при установлении нового логического канала связи, создаваемого в процессе поиска свободного процессора.

Блоки 10 ввода-вывода обеспечивают взаимодействие данного модуля 2 с другими модулями 2 и 3. Каждый иэ блоков 10 имеет внешний вход-выход, который образует один физический канал связи коммутационного модуля 2.

При отсутствии сигналов селекции блока 1О, так же, как и блоков 6-9, входы-выходы этих блоков, соединенные с шиной 13 данных, находятся в третьем состоянии (имеют высокий им педанс).

Терминальный модуль 3 (фиг. 3) включает операционный блок 15, который аналогичен блоку 5 и предназначен для логической обработки принимаемой модулем 3 информации, а также обеспечивает управление остальными блоками модуля 3. Вход-выход операционного блока 15 соединен через шину 23 данных со входами-выходами всех остальных блоков модуля 3. Адресный выход операционного блока 15 соединен с шиной 2 1 адреса, к которой подключены адресные входы блока

16 памяти, блока 17 хранения идентификаторов, блока 18 хранения индикаторов процессоров, приоритетного блока 19 и двух блоков 20 ввода-вывода. Управляющий выход операционного блока 15 соединен с шиной 22 управления, к которой подключены управляющие входы всех блоков модуля 3.

В состав шины 22 управления входят управляющие линии, аналогичные перечисленным для шины 12 управления .

Двунаправленная шина 23 данных также может быть представлена в виде совокупности однонаправленных шик, аналогичнйх перечисленным для шины 13 данных.

Блох 16 памяти, который аналогичен блоку 6, обеспечивает хранение программ, а также данных, в том числе и буферируемых данных, принятых извне.

Блок 17 хранения идентификаторов обеспечивает запоминание имен процессоров, активизированных в подключенном к данному модулю 3 процессоре и взаимодействующих с процессами в других процессорах 4, и идентификаторов занятых логических каналов связи, которые используются при передаче по установленным ранее логическим каналам связи через данный модуль 3 информации к взаимосвязанным с данным модулем 3 другим терминальным модулем 3. Емкость блока 17 определяется числом логических каналов связи, которые можно установить через данный модуль 3.

Блок 18 хранения индикаторов процессоров аналогичен блоку 8.» и используется для хранения служебной ин.— формации, обеспечивающей поиск свободных процессоров 4 различных типов, 1249524

10 подключенных к системе 1 коммутации.

Емкость блока 18, так же, как и блоков 8, .определяется числом типов процессоров 4. Разрядность каждой ячейки блока 18 равна единице.

Приоритетный блок 19 аналогичен блоку 9 и предназначен для формирования свободного в данном терминальном модуле 3 идентификатора при установлении нового логического канала связи, создаваемого в процессе поиска свободного процессора °

Два блока 20 ввода-вывода обеспечивают взаимодействие данного модуля

3 с процессором 4 и одним иэ коммутационных модулей 2 первого уровня.

Каждый из двух блоков 20 имеет внешний вход-выход, который образует один иэ двух входов-выходов терми- 20 нального модуля 3. При отсутствии сигналов селекции блока 20, так же как и блоков 16 — 19, входы-выходы этих блоков, соединенные с шиной 23 данных, находятся в третьем состо- 25 янии (имеют высок ;й импеданс).

Каждый из операционных блоков 5 и 15 (фиг. 4) содержит регистр 25 микропрограммного адреса, который предназначен для запоминания на один микрокомандный цикл текущего микропрограммного адреса. Его выход соединен с адресным входом блока 26 храненйя микропрограмм, обеспечивающего при этом выдачу соответствующей мик- З рокоманды на свои выходы. Первый выход блока 26 (поле формирования следующего адреса микрокоманды) соединен с первыми входами коммутатора 27 микропрограммного адреса и коммутатора 28 адреса ветвления. Второй выход блока 26 (поле задания либо альтернативного микропрограммного адре.са, либо кода базового адреса) сое- . динен с первым входом коммутатора 45

35 базового адреса и со вторымвходом коммутатора 28 адреса ветвления.

Третий выход блока 26 соединен с информационным входом регистра 29 микрокоманды. 50

Коммутатор 27 микропрограммного адреса обеспечивает передачу кода адреса на свой выход, соединенный с информационным входом регистра 25, 55 с одного из двух входов, в зависимости от управляющего сигнала на своем управляющем входе.

Коммутатор 28 адреса ветвления обеспечивает передачу кода адреса на свой .выход, соединенный со вторым входом коммутатора 27, с одного из двух входов, в зависимости от сигнала переноса на своем управляющем входе.

Регистр 29 микрокоманды обеспечивает запоминание на цикл некоторых полей текущей микрокоманды.

Первый выход регистра 29 (поле управления типом микропрограммного перехода) соединен с управляющим входом коммутатора 27. Второй выход регистра 29 (поле кода операции) соединен с управляющим входом арифметико-логического блока 30 ° Третий выход регистра 29 (поле адреса результата операции) соединен с информационным входом дешифратора 33 записи. Четвертый выход регистра 29 (поле управления режимом шины 13/23 данных) соединен с управляющим входом первого буферного усилителя 34.

Пятый выход регистра 29 (поле выбора базового адреса) соединен с управляющим входом коммутатора 35 базового адреса. Шестой выход регистра 29 (поле загрузки) -соединен с управляющим входом регистра 36 селекции. Седьмой выход регистра 29 (поле управления периферийными блоками модуля 2(3) является составной частью управляющего выхода блока

5(15), который соединен с шиной 12 (22) управления. С седьмым выходом. регистра 29 микрокоманды соединены линии 6 1 и 62 чтения и з;.яиси и линии 63 управления узлами приоритетного блока 9(19).

Арифметико-логический блок 30 предназначен для арифметико-логической обработки информации, поступающей на два его входа, в cooT pTcT вии с кодом операции на его управляющем входе. Результат операции появляется на информационном выходе блока 30, соединенном с информационными входами регистров 31и 32; признак результата операции формируется на выходе сигнала переноса блока 30, соединенном с управляющим входом коммутатора 28.

Регистр 31 результата обеспечивает запоминание результата текущей операции блока 30 при наличии сигнала записи на его управляющем входе.

1249524

Выход регистра 31 соединен с первым входом блока 30 и информационным входом первого буферного усилителя 34.

Регистр 32 адреса обеспечивает запоминание результата текущей операции блока 30 при наличии сигнала записи на его управляющем входе. Выход регистра 32 является адресным выходом операционного блока 5(15), который соединен с шиной 11(21) адреса °

Дешифратор 33 записи обеспечивает формирование на одном из своих выходов сигнала записи в зависимости от двоичного кода на информационном входе при наличии синхросигнала на управляющем входе. Первый выход дешифратора 33 соединен с управляющим 2р входом регистра 31, а второй выход— с управляющим входом регистра 32.

Первый буферный усилитель 34 обеспечивает передачу кода операнда на

СВОЙ ВыхОД» ЯвлЯющийсЯ ВхОДОм ВыхО 25 дом операционного блока 5(15) и соединенный со вторым входом коммутатора 35 базового адреса, со своего информационного входа В зависимости от разрешающего сигнала на своем управляющем входе. При отсутствии разрешающего сигнала выход усилителя 34 находится в третьем с.остоянии.

Коммутатор 35 базового адреса обеспечивает передачу унитарного кодаЗ5 адреса на свой выход, соединенный с информационным входом регистра 36 селекции, с одного иэ двух входов, в зависимости от сигнала на своем управляющем входе. 40

Регистр 36 селекции обеспечивает запоминание унитарного кода адреса при наличии сигнала загрузки на его управляющем входе. Выход регистра

36 является составной частью управляющего выхода блока 5(15). Единичный сигнал в одном из разрядов регистра 36 обеспечивает выбор соогветствующего блока модуля 2(3) для текущей с ним работы (выполнение цик-5О ла записи или чтения). С выходом регистра 36 селекции соединены линии

56 селекции блоков 10(20) Ввода-Вывода, линия 57 селекции блоков 6(16) памяти, линия 58 селекции блоков 55

7(17) хранения индификаторов логи-. ческих каналов, линия 59 селекции блоков 8(18) хранения индикаторов процессоров, линия 60 селекции приоритетного блока 9(19).

Генератор 37 синхроимпульсов обес пе ивает выработку непрерывной последовательности синхроимпульсов на своем выходе, который соединен с управляющими входами регистра 25, регистра 29, дешифратора 33. Период следования синхроснгналов определяет микрокомандный цикл блока 5(15).

Приоритетный блок 9(19) содержит (фиг. 5) регистр 38 свободных идентификаторов, предназначенный для хранения суперпозиции унитарных кодов свободных идентификаторов, которые используются для маркировки вновь устанавливаемых через данный модуль 2(3) логических каналов.

Выход регистра 38 соединен со входом приоритетной схемы 39, с первым входом первой группы 42 элементов И и с первым Входом группы 44 элементов ИЛИ.

Приоритетная схема 39 обеспечивает формирование на выходе, соединенном со входом шифратора 40 идентификатора логического канала и через группу 41 элементов HE со вторым входом первой группы 42 элементов. И, унитарного кода старшего единичного разряда из суперпозиции унитарных кодов, присутствующей на ее входе. В таблице показано правило функционирования восьмиразрядной приоритетной схемы 39.

Шифратор 40 идентификатора логического канала обеспечивает преобразование унитарного кода со своего входа в двоичный код на выходе, соединенном с информационным входом второго буферного усилителя 46.

Первая группа 42 элементов И предназначена для формирования после очередного выделения унитарного кода свободного идентификатора логического канала новой, скорректированной суперпозиции унитарных кодов, в которой выделенный унитарный код погашен. Выход группы 42 элементов И соединен с первым информационным входом коммутатора 43 идентификаторов.

Коммутатор 43 идентификаторов обеспечивает передачу информации на свой выход, соединенный с информационным Входом регистра 38 свободных идентификаторов, с одного из

1249524

l2 двух входов, в зависимости от управляющего сигнала на своем управляющем входе.

Дешифратор 45 идентификатора обеспечивает преобразование двоичного кода вновь освободившегося идентификатора со своего входа в унитарный код идентификатора на выходе, соединенном через группу 44 элемен- 1О тов ИЛИ со вторым информационным входом коммутатора 43 идентификаторов.

Второй буферный усилитель 46 обеспеивает выдачу информации с 15 выхода шифратора 40 идентификатора логического канала на шину 13(23) данных при наличии разрешающего сигнала на управляющем входе. При отсутствии разрешающего сигнала выход 2р .буферного усилителя 46 находится в третьем состоянии..

Вторая группа 47 элементов И предназначена для выделения управляющих сигналов с шины 12(22) управления, 25. адресованных к дан ому приоритетному блоку 9(19). Первые входы всех элементов И группы 47 объединены и соединены с линией 60 селекции, являющейся составной частью управляющего входа блока 9(19). Вторые входы элементов И группы 47 соединены соответственно с другими управляющими сигналами, поступающими с управляю— щегб входа блока 9(19) по управляющим линиям 63. Первый выход группы

47 соединен с управляющим входом коммутатора 43 идентификаторов. Второй выход соединен с синхровходом регистра 38 свободных идентификато- 4О ров. Третий выход соединен с установочным входом регистра 38 и обеспечивает начальную установку в единицу всех унитарных кодов. Четвертый выход соединен с управляющим входом 45 второго буферного усилителя 46.

Каждый из блоков 10(20) ввода-вывода содержит (фиг ° 6) выходной регистр 48, обеспечивающий запомина50 ние выдаваемого информационного слова, которое присутствует на шине

13(23) данных, при наличии сигналов записи и селекции на входе загрузки и селектирующем входе. Выход ре55 гистра 33 соединен с выходной информационной шиной одного из внешних входов-выходов 14(24) — физических каналов связи модуля 2(3).

Вход-выход блока 10(20), подключенный к шине 13(23) данных соединен с информационными входами регистра 48, регистра 50 управления выдачей и регистра 51 управления приемом. Адресный вход блока 10(20),,подключенный к шине 11(21) адреса,соединен с информационным входом дешифратора 52 адреса и адресным входом коммутатора 54 входной информации.

Управляющий вход блока 10(20), подключенный к шине 12(22) управления, включает в себя линию 56 селекции данного блока !0(20), соединенную с первыми входами всех элементов и третьей группы 53, а также с управляющим входом дешифратора 52 адреса, линии чтения 6 1 и записи 62, которые подключены ко вторым вхбдам соответствующих элементов И группы 53.

Элементы И группы 53 обеспечивают передачу сигналов со своих вторых входов на выходы при наличии разре- шающего сигнала на линии селекции.

Первый выход (линия записи) элементов И группы 53 соединен с синхровходами регистров 48, 49, 50 и 51; второй выход (линия чтения) соединен с управляющим входом третьего буферного усилителя 55.

Регистры 50 управления выдачей и 5 1 управления приемом предназначены для синхронизации обмена инфор4 мацией по физическому каналу в режиме передачи и приема соответственно. Их выходы являются составной частью внешнего входа-вых 1да 14(24) данного блока 10(20) ввода-вывода.

Регистр 49 приема информации обеспечивает запоминание входного слова и передачу его на свой выход, соединенный с первым входом коммутатора

54 входной информации. !

Дешифратор 52 адреса обеспечивает декодирование двоичного кода адреса регистра данного блока 10(20).Четыре

era выхода соединены с селектирующими входами соответственно регистров

48, 50, 49 и 51.

Коммутатор 54 входной информации обеспечивает передачу информации на свой выход с одного из трех входов в зависимости от двоичного кода на своем адресном входе. Второй и третий информационный входы предназначены для передачи входных управляю13

1249524 щих сигналов иэ физического канала связи и соединены с линиями, образующими часть линий внешнего входавьгхода 14(24) блока 10(20) вводавывода. Выход коммутатора 54 соеди-. нен с информационным входом третьего буферного усилителя 55.

Третий буферный усилитель 55 обеспечивает передачу информации на свой выход для последующего ее анализа в блоке 5(15) со своего информационного входа в зависимости от присутствия разрешающеrо сигнала чтения на своем управляющем входе. В противном случае выход буферного усили. теля 55 находится в третьем состоянии.

Внешний вход-выход 14(24) блока

10(20) ввода-вывода образует один физический канал связи модуля 2(3).

Физический канал связи составляют следующие линии и шины: — выходная информационная шина 70;

- выходная линия 71 запроса на

25 сеанс связи; — выходная линия 72 установки выдаваемого слова; входная информационная шина 73; — выходная линия 74 разрешения сеанса связи; — выходная линия 75 квитирования принятого слова; — входная линия 76 запроса на сеанс связи, 35 — входная линия 77 установки входного слова, — входная линия 78 разрешения сеанса связи, — входная линия 79 квитирования 40 выданного слова.

Блоки 6-8, 16-18 могут быть реализованы на микросхемах оперативного запоминающего устройства. Коммутаторы 27, 28, 35, 43 и 54 — на микро- 45 схемах мультиплексоров ° Дешифраторы

33, 45 и 52, а также шифратор 40— на соответствующих микросхемах. Приоритетную схему 39 можно реализовать с помощью элементов И-НЕ. В ка- 50 честве другого варианта реализации приоритетной схемы 39 и шифратора

40 можно использовать микросхему приоритетного шифратора. Регистры

25, 31, 32, 36 и 38 могут быть реализованы на соответствующих микросхемах, блок 26 хранения микропрограмм — на микросхемах ПЭУ, блок

30 — на микросхемах АЛУ, Для реализации генератора 37 может быть использована микросхема одновибратора.

Регистры 48-51 могут быть реализованы на соответствующих микросхемах.

В качестве другого примера реализации блока ввода-вывода 10(20) можно использовать БИС программируемого параллельно интерфейса. Буферные усилители 34, 46 и 55 могут быть реализованы на микросхемах шинных формирователей, а элементы И, ИЛИ, HE — на соответствующих микросхемах.

Система работает следующим образом.

Каждый процессор 4, подключенный к терминальному модулю 3 системы 1 коммутации, может находиться в свободном (пассивном) или в активном (занятом) состоянии. Свободные процессоры 4 переходят в активное состояние по коммутационным командам от других активных процессоров 4 при установлении между ними логичес. ких каналов связи..Поиск свободного процессора 4 осуществляется в тех случаях, когда. любому активному процессору 4, выполняющему некоторое задание, становится необходим, например, дополнительный ресурс памяти или дополнительный процессор 4 (вычислительный ресурс) определенного типа для непосредственного распарал" леливания вычислительного процесса.

Поиск свободного процессора 4 и одновременное установление логического канала к нему осуществляется децентрализованно коммутационными модулями 2 на основании служебной информации (индикаторов), имеющейся в каждом иэ них и динамически отображающей наличие в текущий момент свободных процессоров из числа процессоров 4, подключенных к системе 1.

Первоначально состояние индикаторов всех типов в блоках 8 и 18 хранения индикаторов процессоров каждого коммутационного модуля 2 и каж г дого терминального модуля 3 соответственно устанавливается при ини-. циализации системы, а затем постоянно корректируется в процессе работы системы путем выдачи каждым терминальным модулем 3 после изменения состояния своего процессора соответствующей коммутационной команды (алгоритмы на фиг. 8-11). Когда любой

1249524

l5

16!

15

20 процессор 4 типа о становится свободным, он выдает об этом сообщение в свой TepMHHclJIBHbtH Mo 3, KOTOpbIA формирует коммутационную команду

"Установка индикатора q --го типа .Она распространяется по всем коммутационным модулям 2 и воспринимается всеми другими терминальными модулями 3. Принимая по -му физическому каналу связи эту команду, каждый коммутационный модуль 2 проверяет состояние индикатора в,i -м разряде ячейки блока 8 хранения индикаторов маршрутов. Если индикатор равен единице, то команда блокируется. В противном случае устанавливается в единичное состояние соответствующий индикатор в блоке 8, а команда выдается в остальные физические каналы связи кроме а -го канала в соответствии со слсдующим правилом.

Если команда поступила в модуль 2 с более низкого (t -1)-го уровня по -му физическому каналу связи из 25 числа физических каналов связи, то команда передается во все физи-. ческие каналы связи, ведущие на более высокий ипи тот же уровни структуры при условии, что индикаторы ти- З0 па g по другим физическим каналам из числа, кроме j -го физического канала, равны нулю (условие А). Команда должна выдаваться в каждый физический канал из числа, не рав35 ный j, если индикаторы типа q no всем другим физическим каналам из числа ь, кроме данного, равны нулю (условие Б) .

Если команда поступила с более высокого или того же уровней по некоторому физическому каналу из числа (Ь+К) каналов модуля 2, то она выдается в любой другой физический канал, если выполняется условие Б. Когда любой процессор 4 типа q становится занятым, он выдает в свой терминальный модуль 3 соответствующее сообщение. По этому сообщению в модуле формируется и выдается B смеж 50 ный коммутационный модуль 2 коммутационная команда "Сброс индикатора

g-го типа", по которой каждый модуль

2, принимая ее по -му физическому каналу, устанавливает в нуль -й ин- 55 дикатор в строке ) блока 8. Условия выдачи этой команды в другие физические каналы аналогичны описанным.

При необходимости поиска1дополI 1 нительного ресурса свободного процессора 4) типа о любой активный процессор 4 выдает в свой терминаль- . ный модуль 3 соответствующий запрос и сообщает при этом имя порта процесса — инициатора запроса. Из регистра 38 свободных идентификаторов приоритетного блока 19 в данном модуле 3 выделяется код свободного идентификатора, который после этого считается занятым, что фиксируется в соответствующем разряде регистра

38 данного модуля 3. Затем в модуле

3 производится взаимная привязка имени порта и вновь занятого идентификатора, что и означает установление логического канала связи через данный модуль 3. Для этого осуществляется запись кода выделенного идентификатора в блок 17 хранения идентификаторов в первую половину ячейки по адресу, определяемому именем порта, а также запись имени порта во вторую половину ячейки блока

17 по адресу, равному коду выбранного идентификатора. После этого модуль 3 формирует и выдает коммутационную команду "Установка логического канала к свободному процессору типа q ", Эта команда сопровождается следующими параметрами: идентификатором, соответствующим данному логическому каналу и индикатором .

При получении этой команды по -му физическому каналу через,i -й блок 10 ввода †выво каждый коммутационный модуль 2 проверяет наличие индикаторов в строке о блока 8 индикаторов процессоров. Если они есть, то из них вьщеляется наиболее предпочтительный индикатор, соотв"тствующий физическому каналу Ь из числа r, кроме физического канала д

Иэ регистра 38 свободных идентифи- каторов (фиг. 5) выделяется унитарный код наиболее приоритетного свободного идентификатора. В соответствии с правилом функционирования приоритетной схемы 39 (см. таблицу) ,это будет старший по номеру идентификатор. Первая группа элементов И

42 формирует новую суперпоэицию унитарных кодов, в которой вьщеленный унитарный код вновь занимаемого идентификатора погашен. При подаче

17 сигнала записи из операционного блока 5 на синхровход регистра 38 в нем запоминается новая суперпозиция кодов. Двоичный код выделенного идентификатора с выхода шифратора 40 через второй буферный усилитель 46 считывается в операционный блок 5.

Для установления логического канала через данный модуль 2 принятый 10 с командой и вновь выделенный идентификаторы запоминаются в соответствующих блоках 7 хранения идентификаторов. При этом в блок 7 ° J в первую половину ячейки по адресу, оп- 15 ределяемому двоичным кодом принятого идентификатора, записывается двоичный код вновь занятого идентификатора и код выходного физического канала.S а в блоке 7.S во вторую поло- 20 вину ячейки по адресу, определяемому двоичным кодом вновь выделенного идентификатора, записывается код принятого идентификатора и код входного физического канала j . Затем в команду на место принятого идентификатора подставляется выделенный в данном модуле 2 идентификатор, и команда выдается в определенный р"-нее выходной физический канал 5че- 30 реэ блок 10. 5 ввода-вывода.

Обрабатываемая таким образом в коммутационных модулях 2 эта коммутационная команда обеспечивает поиск ближайшего свободного процессора требуемого типа и одновременное установление с ним двустороннего логического канала связи. При поступлении в найденный свободный процессор

4 коммутационной команды "Установка щ виртуального канала он переходит в активное состояние> в нем порождается необходимый процесс, имя порта которого он сообщает своему терминальному модулю 3. Это имя порта за- 4 » писывается в блок 17 хранения идентификаторов, в первую половину ячейки по адресу, равному коду принятого идентификатора. Кроме того, во вторую половину ячейки блока l7 по ад- 50 ресу, определяемому именем порта, записывается код принятого идентификатора, После этого модуль 3 выдает в систему 1 коммутации коммутацион- . ную команду Сброс индикатора g-го типа". Описанная процедура установления логического канала связи при поиске свободных процессоров может выполняться одновременно в различных модулях системы 1 коммутации процессоров, что обеспечивает возможность параллельной обработки запросов на свободные ресурсы различных типов, которые независимо поступают в терминальные модули 3.

После логического связывания процессоры 4, являющиеся абонентами одного логического канала, могут обмениваться информацией по существующему между ними двустороннему логическому каналу (алгоритм на фиг ° 10).

Для этого передаваемое сообщение из процессора 4 должно поступить через соответствующий блок 20 ввода-вывода в блок 16 памяти терминальногo о п 3. 3 o ooo eHHe B терминальном модуле разбивается на отдельные пакеты, которые последовательно передаются через коммутационные модули 2 по созданному логическому каналу связи терминальному модулю 3, получателю сообщения.

Для этого используются коммутационные команды "Передача ro прямому (обратному) логическому каналу".

Каждая из этих команд содержит в заголовке кроме кода команд