Аналого-цифровое вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к аналого-цифровой вычислительной технике, но может быть применено также в измерительных системах. Цель изобретения - расширение функциональных .возможностей устройства за счет выполнения операции деления алгебраической суммы сигналов на сумму сигналов . Устройство содержит две группы ключей, регистр, две группы мас; штабных резисторов, дифференциальный усилитель, интегратор, элемент сравнения, триггер, элемент И, счетчик импульсов, вход запуска, первые и вторые группы аналоговых информационных входов, цифровой информационньй вход, шину тактовых импульсов. При запуске триггер устанавливается в 1, и на счетный вход счетчика импульсов через элемент И поступают импульсы тактовой частоты. Одновременно начинается интегрирование напряжения с первой группы ключей. В момент равенства напряжений с выхода интегратора и дифференциального усилителя сигнал с выхода элемента сравнения сбрасьшает триггер в . Код на выходе счетчика при этом пропорционален относительной разности напряжений. Введение в устройство ключей, регистра, масштабных резисторов , дифференциального усилителя и интегратора, а также новые связи меяоду элементами устройства обеспечило достижение поставленной це- ,ли. 1 ил. (С (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК. (!9) (!!) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3856813/24-24 (22) 09.01.85 (46) 07.08.86. Вюл. é 29 (72) Н.P. Андронатий и M.Н. Бурдиян (53) 681.34 (088.8) (56) Авторское свидетельство СССР

Ф 604004, кл. G 06 G 7/16, 1976.

Авторское свидетельство СССР

У 746603, кл. G 06 J 3/00, 1980. (54) АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬ-,НОЕ УСТРОЙСТВО (57) Изобретение относится к аналого-цифровой вычислительной технике, но может быть применено также в измерительных системах. Цель изобретения — расширение функциональных возможностей устройства за счет выполнения операции деления алгебраической суммы сигналбв на сумму сигналов. Устройство содержит две группы ключей, регистр, две группы масштабных резисторов, дифференциальный усилитель, интегратор, элемент (5!) 4 G 06 J 3/00, G 06 G 7/12 сравнения, триггер, элемент И, счетчик импульсов, вход запуска, первые и вторые группы аналоговых информационных входов, цифровой информационнь)й вход, шину тактовых импульсов.

При запуске триггер устанавливается в "1", и на счетный вход счетчика импульсов через элемент И поступают импульсы тактовой частоты. Одновременно начинается интегрирование напряжения с первой группы ключей. В момент равенства напряжений с выхода интегратора и дифференциального усилителя сигнал с выхода элемента сравнения сбрасывает триггер в "0 .

Код на выходе счетчика при этом пропорционален относительной разности напряжений. Введение в устройство ключей, регистра, масштабных резисторов, дифференциального усилителя и интегратора, а также новые связи между элементами устройства обеспечило достижение поставленной це,ли. 1 ил.

1249550

Изобретение относится к области аналого-цифровой вычислительной техники и может быть применено в измерительных системах.

Целью изобретения является расширение .функциональных возможностей устройства за счет выполнения операции деления алгебраической суммы сигналов на сумму сигналов.

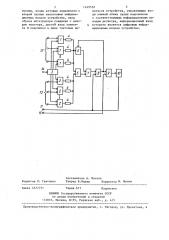

На чертеже приведена структурная схема аналого-цифрового вычислительного устройства.

Устройство содержит две группы ключей 1 и 2, регистр 3, две группы масштабных резисторов 4, дифференциальный усилитель .5, интегратор 6, элемент 7 сравнения, триггер 8,элемент И 9, счетчик 10 импульсов, вход

11 запуска, первые и вторые группы аналоговых информационных входов

12 и 13, цифровой информационный вход 14, шину 15 тактовых импульсов.

Устройство работает следующим образом.

В исходном состоянии триггер 8 находится в состоянии логического

"0", поэтому интегратор 6 сброшен и сигналы тактовой. частоты с шины

15 на счетный вход счетчика 10 не поступают. При подаче на вход 11 запуска импульса триггер 8 устанавливается в. "-1", на счетный вход счетчика 10 через элемент И 9 поступают импульсы тактовой частоты. Одновременно начинается интегрирование напряжения U „ интегратором 6.

Напряжение U, равно

UX1 U, + Пл2 + ° ° + U h где U — напряжения на первой группе аналоговых входов 12 устройства.

При этом напряжения или их комбинация, которые подаются на вход интегратора 6, определяются кодом с соответствующих выходов регистра 3, которые управляют ключами 1.

Напряжение на выходе интегратора 6 изменяется по закону U(t)

= U, t/, где — постоянная времени. В момент времени t„ напряжение

V(t) станет Равным напРЯжению ПЕл—

U и сигналом с выхода элемента 7

Е2 сравнения триггер 8 устанавливается в "0".

Напряжение U 2 равно

+ + ... + u

2. 2 2л 22 2

Выбор напряжений для суммирования определяется кодом с регистра 3, подаваемым на управляющие входы ключей 2. Записанный в счетчик 6 код равен ел где f — тактовая частота, т.е. он

10 пропорционален относительной разности напряжений Uz, и П

Предлагаемое устройство в зависимости от кода с регистра 3 позволяет производить операции над раз15 личными переменными или над их суммами. Так, например, можно получить код в счетчике 6, пропорциональный — (u +v„) . лл

П21 П22 ) и множество

Л2

U,;

20 (u +u„) 11 + лл дру гих комбинаций.

Формула изобретения

Аналого-цифровое вычислительное устройство, содержащее последовательно включенные элемент сравнения,триггер, элемент И и счетчик импульсов, выход которого является цифровым информационным выходом устройства, вход сброса счетчика объединен с другим установочным входом триггера

35 и является входом запуска устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выполнения операции деления алгебраической

40 суммы сигналов на сумму сигналов, оно содержит регистр, две группы ключей, две группы масштабных резисторов, интегратор и дифференциальный усилитель, выход которого подклю45 чен к первому входу элемента сравнения, подсоединенного вторым входом к выходу интегратора, информационный вход которого соединен с инвертирующим входом дифференциального

50 усилителя и через масштабные резисторы первой группы подключен к выходам ключей первой группы, входы которых подключены к первой группе аналоговых информационных входов устройства, неинвертирующий вход дифференциального усилителя через масштабные резисторы второй группы подключен к выходам ключей второй

Составитель А. Маслов

Техред В.Кадар Корректор И Муска

Редактор Л. Гратилло

Заказ 4327/51

Тираж 671

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 группы, входы которых подключены к второй группе аналоговых информационных входов устройства, вход сброса интегратора соединен с выходом триггера, другой вход элемента И подключен к шине тактовых им1 249550 4 пульсов устройства, управляющие входы ключей обеих групп подключены к соответствующим информационным выходам регистра, информационный вход которого является цифровья информационным входом устройства.