Устройство для синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах для синхронизации , обеспечивающих требуемую последовательность и дпительность операций. Целью изобретения является повышение быстродействия. Отличительной особенностью устройства является возможность нормирования длительности режима ожидания и гибкого изменения длительности циклов синхронизации , в которых отсутствует режим ожидания. Поставленная цель достигается тем, что в устройство введены третий коммутатор, счетчик, элемент ИЛИ-НЕ, элемент ИЛИ, элемент НЕ, два элемента И. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (SD 4 G 06 F 1/04

ВСЮОТЩУ, 13,",., ",, ц

ЯВ,11ИО ДЖА

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К Д BT0PCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3848670/24-24 (22) 31.01.85 (46) 15.08.86. Бюл. N - 30 (72) 10.H.Áåñîâ и И.А.Сафин (53) 681.3(088.8) (56) Авторское свидетельство СССР

11- 471581, кл, G 06 F 1/04, 1973.

Авторское свидетельство СССР

9 1015336, кл. G 06 F 1/04, 1981. (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах для синхро„„SU„„1253 55 А1 низации, обеспечив ающих требуемую последовательность и длительность операций. Целью изобретения является повьппение быстродействия. Отличительной особенностью устройства является возможность нормирования длительности режима ожидания и гибкого изменения длительности циклов синхронизации, в которых отсутствует режим ожидания. Поставленная цель достигается тем, что в устройство введены третий коммутатор, счетчик, элемент ИЛИ-НЕ, элемент ИЛИ, элемент

НЕ, два элемента И. 1 ил.

1251055

Изобретение относится к вычислительной технике и может быть использовано в устройствах для синхронизации, обеспечивающих требуемую последовательность и длительность операций.

Цель изобретения - повышение быстродействия.

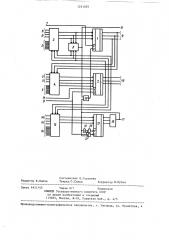

На чертеже изображена схема устройства, Устройство содержит регистры 1 и

2, коммутаторы 3 и.4, первую группу

5 входов сигналов логических условий, блок 6 сравнения, вход 7 первой .Фазовой синхронизации, вход 8 второй

Фазовой синхронизации, первую группу

9 выходов Фазовой синхронизации, вторую группу 10 выходов фазовой синхронизации, вход 11 разрешения следующего состояния устройства, контрольный выход 22 режима ожидания устройства, коммутатор 13, вторую группу

14 входов сигналов логического условия устройства, счетчик 15, элемент

ИЛИ lб, дополнительный контрольный выход 17 устройства, элемент ИЛИ-НЕ

18 элемент НЕ 19, элементы И 20 и 21, Устройство работает следующим образом.

В исходном состоянии выходы регистров l и 2 и счетчика 15 находятся в нулевом состоянии. На выходах коммутаторов 3,4 и 13 устанавливаются коды, определяющие следующее состояние усгройства. Счетчик 15 по входу разрешения записи с выхода элемента ИЛИ 16 устанавливается в режим параллельной записи. По приходу первого Фазового импульса с входа 7 в регистр 1 записывается код, задающий новое состояние синхронизируемого устройства через первую группу 9 выходов и одновременно поступающий на управляющие входы коммутатора 4, определяя код на информационных входах второго регистра 2. По второму фазо— вому импульсу, поступающему через вход 8, в счетчик заносится код с выхода коммутатора 13, а в регистр

2 — код, определяющий следующее состояние синхронизируемого устройства через группу 10 выходов. Кроме того, код с выхода регистра 2 поступает на управляющие входы коммутатора 3, определяя следующее. состояние на информационных входах регистра l, и на управляющие входы коммутатора 13, ус5

55

Если при выполнении следующего цикла синхронизации коды на первой и второй группах входов блока б сравнения не равны, т.е. режим ожидания отсутствует, то в счетчик 15 записывается код, определяющий вретанавливая следующее состояние на информационных входах счетчика 15, При равенстве кодов на управляющих входах и информационных выходах коммутатора 3, т.е. на первых и вторых группах входов блока б сравнения, на выходе блока б сравнения вырабатывается сигнал, который через элемент

ИЛИ-НЕ 18 блокирует запись в регистр и поступает через контрольный вы" ход 12 в синхронизируемое устройство, Фиксируя начало режима ожидания °

Счетчик 15 после записи в него кода с выхода коммутатора 13 сигналом временной длительности с выхода элемента ИЛИ 16 устанавливается по счетному входу в режим реверсивного счета. Одновременно сигнал временной длительности с выхода элемента ИЛИ 16 поступает во внешнее синхронизируемое устройство через дополнительный контрольный выход 17 и на второй вход элемента ИЛИ-НЕ 18, дополнительно блокируя запись в регистр 1. Длительность этого сигнала соответствует количеству тактов импульсов Фазовой синхронизации, определяемому кодом, записанным в счетчик 15 по инФормационным входам. По последнему тактовому импульсу íà выходах счетчика 15 устанавливается нулевой код, определяюш и окончание сигнала временной дпительности на выходе элемента ИДИ 16 и переключающий счетчик 15 по управляюшему входу в режим параллельной записи. Если,за время дейст" вия сигнала временной длительности внешнее синхронизируемое устройство не выставило на входы 5 логическое условие снятия режима ожидания, то по окончании (заднему Фронту) сигнала временной длительности во внешнем синхронизируемом устройстве Формируется сигнал, дополнительно устанавливающий через входы 5 логическое условие снятия режима ожидания, т.е. осуществляется нормирование режима ожидания по какому-то определенному контрольному времени. Это позволяет исключить случайные остановы устройства на сколь угодно долгое время.

3 1251 менную длительность данного цикла, и сигнал временной длительности с выхода элемента ИЛИ 16 через второй вход элемента ИЛИ-НЕ 18 блокирует запись нового состояния в регистр 1 до полного выполнения данного цикла синхронизации. Тем самым программируется длительность выполнения любой операции, а период импульсов фазовой синхронизации выбирается из )Î условия выполнения минимальной по длительности операции. Например, для выполнения трех операций с длительностями 3, !5 и 30 мкс период импульсов синхронизации равен 3 мкс ° !5

В случае отсутствия счетчика 15 период импульсов синхронизации должен быть не менее 30 мкс.

Формула изобретения?0

Устройство для синхронизации, содержащее два коммутатора, два регистра, блок сравнения, причем группа выходов первого коммутатора соедине- 25 на с группой информационных входов первого регистра и с первой группой входов блока сравнения, группа выходов первого регистра соединена с группой управляющих входов второго коммутатора и является первой группой выходов фазовой синхронизации устройства, группа выходов второго коммутатора соединена с группой информационных входов второго регистра, группа выходов которого соединена с второй группой входов блока сравнения, с группой управляющих входов первого коммутатора и является второй группой выходов фазовой синхронизации устройства, первая группа входов логических условий устройства соединена с группой инфор055 4 мационных входов первого и второго коммутаторов, первый и второй входы фазовой синхронизации устройства соединены соответственно с синхровходами первого и второго регистров, вход разрешения следующего состояния устройства соединен с управляющим входом второго регистра, выход блока сравнения является контрольным выходом устройства, о т л и ч а ю щ е ес я тем, что, с целью,повышения быстродействия, в устройство введены третий коммутатор, счетчик, элемент

ИЛИ-НЕ, элемент ИЛИ, элемент НЕ, два элемента И, причем вторая группа входов логических условий устройстВа соединена с группой информационных входов третьего коммутатора, rpyrma управляющих входов которого соединена с груплой выходов второго регистра, группа выходов третьего коммутатора соединена с группой информационных входов счетчика, выходы разрядов которого соединены с соответствующими входами элемента ИЛИ, выход которого соединен с первым входом элемента ИЛИ-НЕ, с входом элемента

НЕ, с первым входом первого элемента

И и является дополнительным контрольным выходом устройства, второй вход элемента ИЛИ-НЕ соединен с выходом равенства блока сравнения, выход элемента ИЛИ-НЕ соединен с входом разрешения записи первого регистра, второй вход фазовой синхронизации устройства соединен с вторым входом первого элемента И и с первым входом второго элемента И, второй вход которого соединен с выходом элемента HE выход первого элемента И соединен со счетным входом счетчика, вход разрешения записи которого соединен с выходом второго элемента И.

1251О55

Составитель Е.Торопова

Техред О,Сопко Корректор И.МУска

Редактор Е.Копча

Заказ 4411/45 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий . 113035, Москва, Ж-35, Раушская наб., д . 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4