Устройство для отображения информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для вьшода графической информации из ЭВМ. Целью изобретения является повьшение быстродействия . Устройство содержит два генератора импульсов, блок синхронизации, счетчик, блок буферной памяти, три коммутатора, регистр, блок сопряжения , формирователь видеосиг; алов, триггер, элемент ИЛИ и формирователь числа нуль. ГТовьппение быстродействия обеспечивается введением элементов, обеспечивающих ускоренное обнуление блока буферной памяти, 2 -ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (sg g G 06 F 3/153

1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3833067/24-24 (22) 30.12.84 (46) 15.08.86. Бюл. Ф 30 (72) В.Г.Неклюдов, В.С.Волков и Ю.Л.Чувашов (53) 681.327.11(088.8) (56) Авторское свидетельство СССР

Р 734759, кл. G Об F 3/153, 1980.

Устройство, запоминающее изображение. Информационный листок ВИМИ, !

1 82-0972, сер. 13-08 °

„„Я0„„2510а2 A1 (54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано для вывода графической информации из ЭВМ. Целью изобретения является повьппение быстродействия. Устройство содержит два генератора импульсов, блок синхронизации, счетчик, блок буферной памяти, три коммутатора, регистр, блок сопряжения, формирователь видеосиг. алов, триггер, элемент ИЛИ и формирователь числа "нуль". Повьппение быстродействия обеспечивается введением элементов, обеспечивающих ускоренное обнуление блока буферной памяти.

2 ил.

12

Изобретение относится к вычислительной технике и может быть использовано для вывода графической информации из ЗВИ на пульты управления, например, устройства числового программного управления станками.

Цель изобретения — повьппение быстродействия устройства.

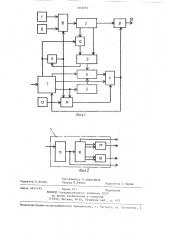

На фиг,l изображена структурная схема устройства; на фиг.2 — структурная схема блока сопряжения, Устройство содержит первый генератор 1 импульсов, блок 2 синхронизации, счетчик 3, блок 4 буферной памяти, первый коммутатор 5, регистр

6, блок 7 сопряжения, формирователь

8 видеосигнала, второй генератор 9 импульсов, второй коммутатор 10, первый триггер 11, элемент ИЛИ 12, задатчик 13 кода числа "нуль1, третий коммутатор 14, канальный приемопередатчик 15, дешифратор 16 команд, второй триггер 17, третий триггер 18, выход 19 устройства.

Генераторы 1 и 9 представляют собой rенераторы импульсов, например мультивибраторы, причем частота второго генератора 9 вьппе частоты первого генератора ). Частота первого генератора выбирается такой, чтобы частота смены кадров изображения соответствовала стандартной частоте

50 Гц. Частота второго генератора выбирается максимально возможной для обеспечения минимального времени обнуления блока 4 буферной памяти и ограничивается быстродействием элементов памяти.

Блок 2 синхронизации содержит в своей основе:счетчик (делитель частоты) и логические элементы для формирования синхронизирующих импульсов необходимой длительности и частоты.

С первого выхода на счетный вход счетчика 3 поступает частота, определяемая количеством точек на экране, с второго выхода на формирователь видеосигнала поступает частота, с которой выдается на экран информация, а с третьего выхода через элемент

ИЛИ 12 на вход установки счетчика 3

11 11 в 0 поступает частота, равная частоте кадровой развертки — 50 Гц, Счетчик 3 выполнен по схеме двоичного нереверсивного счетчика с последовательным переносом, имеющим счет.ный вход и вход установки и "0".

Блок 4 буферной памяти представляет собой набор элементов памяти, ста51062 2 тической или динамической. Регистр 6 представляет собой статический ре гистр с параллельной записью информации и с выходом информации в параллельном коде ° Коммутаторы 5, 10 и 14

10 l5

<0

55 представляют собой набор переключающих логических элементов и отличаются только количеством переключаемых разрядов. Число разрядов первого коммутатора 5 равно числу адресных разрядов блока 4 буферной памяти. Число разрядов третьего коммутатора 14 равно числу разрядов данных блока 4 буферной памяти. Второй коммутатор 10 переключает только одну цепь. Формирователь 8 видеосигналов представляет собой преобразователь параллельного кода в последовательный и в основе своей содержит сдвиговый регистр, который управляется. сигналами с блока 2 синхронизации.

Триггер 11 представляет собой триггер с разделительными входами установки в "0" и "1". Задатчик 13 кода числа "нуль представляет собой элемент, на выходе которого постоянно установлен потенциал "0".

Блок 7 сопряжения состоит из канальных приемопередатчиков 15 для согласования с магистралью ЗВМ (не показана), дешифратора 16 команд, триггера,17 для формирования управляющего сигнала первого коммутатора и триггера 18 для формирования сигнала "Чтение-запись" для блока 4 буферной памяти (в устройстве увеличен объем дешифратора для формирования сигнала "Сброс", который запоминает" ся в триггере 11).

Устройство работает следующим образом.

В первом режиме осуществляется вывод информации из ЭВМ в блок 4 буферной памяти. Триггер 11 находится в исходном состоянии, поэтому к информационному входу блока. 4 буферной памяти подключен через третий коммутатор 14 выход блока 7 сопряжения.

Адрес ячейки, в которую должна заноситься информация, записывается в регистр 6. На управляющем входе блока

4 буферной памяти устанавливается ре11 11 жим Запись, адресный вход подключается к регистру б через первый коммутатор 5, который переключается по сигналу первого выхода блока 7 сопряжения, после чего на втором выходе блока 7 сопряжения появляются

ОЬ2 ти.

3 12с1 данные, которые через третий коммутатор 14 записываются в блок 4 буферной памяти по заданному адресу.

Во втором режиме устройство работает автономно, так как триггер 11 находится в исходном состоянии, на вход блока 2 синхронизации через второй коммутатор 10 поступает частота с первого генератора 1. Адресный вход блока 4 буферной памяти подклю- t0 чен через первый коммутатор 5 к выходу счетчика 3, содержимое которого последовательно изменяется от нуля до числа, определяющего максимальный адрес ячейки памяти. С третьего выхо †да блока 2 синхронизации с частотой кадровой развертки поступают импульсы установки счетчика 3 в 0 . На управляющем входе блока 4 буферной памяти устанавливается режим Чте- 2î ние", и данные из блока 4 буферной памяти поступают на вход формирователя 8 видеосигналов и по тактовым импульсам с выхода блока 2 синхронизации поступают на выход 19 устрой- 25 ства. Таким образом вся информация, записанная в блок 4 буферной памяти, поступает на выход 19 устройства, к которому подключен блок индикации (не показан . Частота генератора 1 выбирается такой, чтобы выдача всего массива информации из блока 4 буферной памяти происходила со стандартной частотой 50 Гц.

В третьем режиме по команде ЭВМ с четвертого выхода блока 7 сопряжения устанавливается триггер 11 и через элемент ИЛИ 12 счетчик 3 устанавливается в "0". Сигналом с выхода триггера переключается третий комму- 40 татор 14, который подключает к информационному входу блока 4 буферной памяти выход задатчика 13 кода числа

"нуль". К входу блока 2 синхронизации подключается через второй комму в p5 татор 10 второй генератор 9, имеющий более высокую частоту относительно генератора 1. Счетчик 3 последова— тельно перебирает все адреса ячеек памяти и по переполнению устанавливает триггер 11 в исходное состояние.

Таким образом, во все ячейки блока 4 буферной памяти записывается "0".

Частота генератора 9 выбирается исходя из быстродействия элементов памяФормула изобретения

Устройство для отображения информации, содержащее первый генератор импульсов, блок синхронизации, первый выход которого соединен со счетным входом счетчика, а второй выход соединен с тактовым входом формирователя видеосигналов, выход которого является выходом устройства, первый коммутатор, адресный вход которого соединен с выходом счетчика, информационный вход — с выходом регистра, а управляющий вход — с первым выходом блока сопряжения, первый вход которого является входом устройства, блок буферной памяти, адресный вход которого соединен с выходом первого коммутатора, а выход — с информационным входом формирователя видеосигнала и с вторым входом блока сопряжения, второй выход которого соединен с входом регистра, а третий выход — с управляющим входом блока буферной памяти, отличающее с я тем, что, с целью повышения быстродействия, оно содержит второй генератор импульсов, второй коммутатор, триггер, элемент ИЛИ, задатчик кода числа "нуль" и третий коммутатор, адресный вход которого соединен с вторым выходом блока сопряжения, информационный вход — с выходом задатчика кода числа "нуль", выход — с информационным входом блока буферной памяти, а управляющий вход — с выходом триггера, первый вход которого соединен с четвертым выходом блока сопряжения, а второй вход — с выходом переполнения счетчика, первый и второй информационные входы второго коммутатора соединены с выходами первого и второго генераторов импульсов соответственно, управляющий вход — с выходом триггера, а выход — с входом блока синхронизации, третий выход которого соединен с первым входом элемента

ИЛИ, второй вход которого соединен с четвертым выходам блока сопряжения, а выход — с входом установки в "0 счетчика.

l 25 1062

Составитель Л:Абросимов

Техред О.Сопко Корректор С. 1ерни

Редактор E.Копча

Заказ 4411/45

Тираж 671 Подписное

ВНИИГ1И Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб..„ ц, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, .л. Проектная 4