Устройство для контроля цифровых узлов

Иллюстрации

Показать всеРеферат

Изобретение отиосится к вычислительной технике и может быть использовано при тестовой диагностике цифровых узлов, содержащих микросхемы с ТТЛ уровнем и ЭСЛ уровнем. Устройство содержит генератор тестов, дешифратор , триггер, элемент И, буферный , регистр, регистр тестов, регистр коммутации, блок преобразования уровней , блок обратного преобразования уровней, схему сравнения. Из .генератора тестов поступает информация в блок управления, где на дешифраторе происходит дешифрация этой инфор мации, и с выходов дешифратора снимается информация, которая служит для последовательной синхронизации регистров. С буферного регистра эталонная информация идет на схему сравнения . Тестовая информация идет на регистр тестов, на регистр коммутации поступает информация о расположении входов с уровнем ТТЛ и входов с уровнем ЭСЛ. Выходы с объекта кон-ьроля, соответствующие ТТЛ уровням, идут через блок преобразования уровней и блок обратного преобразования уровней вместе с выходами, соответствующими ЭСЛ уровнями, которые проходят через блок обратного преобразования , на схему сравнения, где сравниваются и в случае ошибки происходит останов генератора тестов. Тестовая информация с регистра тестов поступает на коммутатор непосредственно , а также, пройдя преобразование в блоке двойного преобразования, поступают на коммутатор, который управляется регистром коммутации. 2 ил. ю (Л

СОЮЗ СОВЕТСКИХ

С01.1ИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А1 (19) 01) (51)4 G 06 F ll

OllHCAHHE ИЗОБРЕТЕНИЯ

H А ВТОРСИОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3833939/24-24

° °

22) 02.01.85

46) 15.08.86. Бюл, У 30 (72) Н.Н. Кузьмин и В.И. Фомич (53) 681,3 (088.8) (56) Авторское свидетельство СССР

У 1013960, кл. G 06 F 11/16,1981.

Авторское свидетельство СССР

У 947863, кл. G 06 F 11/16, 1980. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ УЗЛОВ (57) Изобретение относится к вычислительной технике и может быть использовано при тестовой диагностике цифровых узлов, содержащих микросхемы с ТТЛ . уровнем и ЭСЛ уровнем. Устройство содержит генератор тестов, дешифратор, триггер, элемент И, буферный регистр, регистр тестов, регистр коммутации, блок преобразования уровней, блок обратного преобразования уровней, схему сравнения. Иэ .генератора тестов поступает информация в блок управления, где на дешифраторе происходит дешифрация этой информации, и с выходов дешифратора снимается информация, которая служит для последовательной синхронизации регистров. С буферного регистра эталонная информация идет на схему сравнения. Тестовая информация идет на регистр тестов, на регистр коммутации поступает информация о расположении входов с уровнем ТТЛ и входов с уровнем ЭСЛ. Выходы с объекта конъ., роля, соответствующие ТТЛ уровням, идут через блок преобразования уров— ней и блок обратного преобразования уровней вместе с выходами, соответствующими ЭСЛ уровнями, которые проходят через блок обратного преобразования, на схему сравнения, где сравниваются и в случае ошибки происходит останов генератора тестов.

Тестовая информация с регистра тестов поступает на коммутатор непосредственно, а также, пройдя преобразование в блоке двойного преобразования, поступают на коммутатор, который управляется регистром коммутации.

2 ил.

1251085

45

50.. информационных входов регистра тесИзобретение относится к вычислительной технике и может быть использовано для контроля логических блоков и цифровых узлов ЭВМ.

Известно устройство для контроля цифровых узлов, содержащее, блок памяти, блок сравнения, блок управления, блок формирования тестовой информации, регистр теста, блок муль1тнплексоров„коммутатор.

Цель изобретения — расширение функциональных возможностей за счет обеспечения контроля цифровых узлов, построенных на элементах различных логик

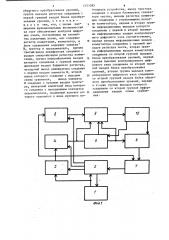

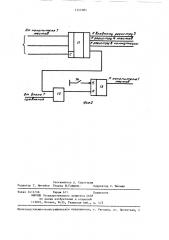

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - схема блока управления.

Устройство (фиг.1) содержит генератор 1 тестов, блок 2 управления, буферный регистр 3, регистр 4 тестов, блок 5 преобразования уровней, блок 6 обратного преобразования уровней, блок сравнения 7, регистр 8 коммутации, коммутатор 9, контролируемый цифровой узел 10.

Блок управления содержит дешифратор 11, элемент И 12, триггер 13, переключатель 14, Устройство работает следующим образом.

Данные из, генератора 1 тестов поступают на вход дешифратора ll u буферного регистра 3. Блок 2 управления с помощью дешифратора 11 распределяет поступающую информацию между регистрами устройства 3, 4 и 8.

В регистр 8 коммутации записывает" ся информация о разделении входных контактов проверяемого узла на контакты с уровнями ТТЛ-логики и конта:— ты с уровнями ЭСЛ-логики, в регистр

4 тестов - элементарный стимул, во входной регистр 3 . — эталонная информация.

Стимулирующие сигналы в уровнях ТТЛ-логики с выхода регистра 4 тестов поступают на первую группу информационных входов коммутатора 9 и на вход блока 5 преобразования уровней, который служит для преобразования уровней ТТЛ вЂ” ЭСЛ. Сигналы с выходов блока 5 преобразования уровней

Поступают на вторую группу информационных входов коммутатора 9 и на вход блока 6 обратного преобразования уровней, который служит для обратного преобразования уровней ЭСЛ!

О

ТТЛ. Сигналы с выходов блока 5 преобразования уровней поступают на другую группу информационных входов коммутатора 9 и на вход блока 6 образ ного преобразования уровней, который служит для обратного преобразования уровней ЭСЛ-ТТЛ.

Коммутатор 9 создает цепи для прохождения сигналов н ТТЛ-уровнях или в ЭСЛ-уровнях раздельно для каждого контакта проверяемого узла в зависимости от состояния регистра 8 коммутации.

В блоке 7 сравнения производится сравнение содержимого буферного регистра 3 с информацией на контактах контролируемого узла, которая попадает на группу входа блока 7 сравнения через блоки 5 и 6 преобразования уровней, если данный контакт с ТТЛ-уровнями, и только через блок 6 обратного преобразования уровней, если данный контакт с ЭСЛ-уровнями.Результат сравнения опрашивает-а в блоке 2 управления на элементе И 12, и в случае несравнения сбрасывается триггер. !3, тем самым прекращая поступление информации из накопителя тестов, Формула изобретения

Устройство для контроля цифровых уэлон, содержащее генератор тестов, буферный регистр, регистр тестов, блок сравнения, блок преобразования уровней, блок- обратного преобраэонания уровней, блок управления, содержащий дешифратор, причем информационные выходы генератора тестон. соединены с информационными входами буферного регистра и информационными входами дешифратора, выход признака синхронизации генератора тестов соединен с синхровходом дешифратора, первый выход которого соединен с синхровходом буферного регистра, группа выходов признаков теста которого соединена с группой тов, синхровход которого соединен со вторым выходом дешифратора, группа выходов признаков эталона буферного регистра соединена с первой группой информационных нходон блока сравнения, первая группа выходов блока преобразования уровней соеди; ена с первой группой входон блока

1251

10 обратного преобразования уровней, группа выходов регистра соединена с первой группой входов блока преобразования уровней, о т л н ч а ющ е е с я тем, что, с целью рас.ширения функциональных возможностей за счет обеспечения контроля цифровых узлов, построенных на элементах различных логик, оно содержит регистр коммутации, коммутатор, а к блок управления содержит элемент

И, триггер и переключатель причем третий выход дешифратора соединен с входом синхронизации регистра коммутации, группа информационных входов которого соединена с группой выходов признаков входов буферного регистра, четвертый выход дешифратора соединен с первым входом элемента И, второй выход которого соединен с выходом 2О схемы сравнения, . выход элемента

И соединен с нулевым входом триггера инверсный единичный вход котороl го соединен с неподвижным контактом переключателя, подвижный контакт ко- 25 торого подключен к шине нулевого по1

085 4 тенциала устройства, выход триггера соединен с входом блокировки генератора тестов, выходы регистра коммута" ции соединены с управляющими входами коммутатора, первая и вторая группы информационных выходов которого соединены с первой и второй группами информационных входов контролируемого цифрового узла соответственно, первая группа информационных входов коммутатора соединена с группой выходов регистра теста, вторая группа информационных входов коммутатора соединена со второй группой выходов блока преобразования уровней, первая группа выходов контролируемого цифрового узла соединена со второй груп-. пой входов блока преобразования уровней, вторая группа выходов конт» ролируемого цифрового узла соединена со второй группой входов блока обратного преобразования уровней, первая . и вторая группы выходов которого соединены со второй группой информационных входов схемы сравнения.1251085

& н к ст РюЯ 1

Составитель А, Сиротская

Редактор Т. Митейко Техред И.Гайдои,. Корректор С. 1Чекмар

Заказ 44)2/46 Тираж 671 Подписное

ВНИЧПИ Государственного комитета СССР по делам изобретений и открь.тий

1 13035, Москва, R-35, Раушская наб., д. 4/5

Производственно-полиграфическое. предприятие, г. Ужгород, ул, Проектная, 4