Буферный регистр

Иллюстрации

Показать всеРеферат

Изобретение относится к вычисдительной технике и может быть использовано при построении многопроцессорных вычислительных систем. Буферный регистр содержит блок триггеров , блок выходных ключевых элементов f тремя состояниями и управляющий блок, состоящий из элементов И, ИЛИ и ЗАПРЕТ. Изобретение позволяет повысить быстродействие регистра в режиме сквозной передачи информации с входа на выход благодаря введению дополнительного элемента И в управляющий блок, изменению связей между элементами управляющего блока и введению дополнительного управляющего входа. 1 ил.

СООЭ СОВЕТСКИХ

Ю4

PECflYSl}HH (51)4 6 11 С 19/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,"д;

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3836725/24-24 (22) 07.01.85 (46) 15.08.86. Бюл. У 30 (72) В.В.Кангин, Л.М.Кангииа, HiII.ßìïóðHí и A.Â.Ãðà÷åâ (53} 681.327.66(088.&) (56) Алексенко А.Г. и др. Проектирование радиоэлектронной аппаратуры на микропроцессорах. М.: Радио и связь, 1984, с. 21-30.

Соучек Б. Микропроцессоры и микроЭВМ. М.: Сов. радио, 1979, с.243-244. (54) БУФЕРНЫЙ РЕГИСТР (57) Изобретение относится к вычислительной технике и может быть исSU„„12511S0 А1 пользовано при построении многопроцессорных вычислительных систем. Буферный регистр содержит блок триггеров, блок выхолньгх ключевых элементов тремя состояниями и управляющий блок, состоящий из элементов И, ИЛИ и ЗАПРЕТ. Изобретение позволяет повысить быстродействие регистра в режиме сквозной передачи информации с входа на выход благодаря введению дополнительного элемента И в управляющий блок, изменению связей между элементами управляющего блока и введению дополнительного управляющего входа. 1 ил.

1251180

Изобретение относится к вычисли, тельной технике и может быть исполь-зовано при построении многопроцессорных вычислительных систем,.

Цель изобретения — понытпение 5 быстродействий буферного регистра при использовании его н многопроцессорных системах.

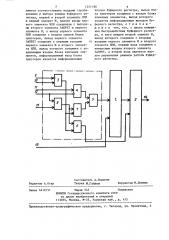

На чертеже приведена схема буферного регистра. 1О

Регистр содержит блок 1 триггерон, блок 2 ключевых элементов, первый 3 и второй 4 элементы ЗАПРЕТ, первый 5 и нторой 6 элементы ИЛИ и первый 7 v второй 8 элементы И. На чертеже обоз- 15 начены также первый 9 и второй 10 входы выборки регистра, вход 11 стробированкя, вход 12 выбора режима, информационнътй вход 13, информационный выход 14 и вход 15 управления ре- >б жимом работы регистра„ Вход 13 и выход 14 являются соответственно входной и выходной шинами данных.

Регистр работает следующим обра75 зом.

Если на вход 15 подана логическая единица, регистр настраивается на работу в однопроцессорнои системе, Fcлк на вход 12 при этом подается логиЯ/, ческий ноль, при подаче сигнала логической единицы на вход 11 стробкрования производится запись ттнформации н блок ° 1 триггеров с входа 13. Сиrнал записи снимается с выхода первого элемента ИЛИ 5. Предварительное формирование сигнала записи осуществляется вторым элементом ЗЛПРЕТ 4.

Вывод информации производится при подаче сигналов на входы 9 v 10 выборки, На выходе первого элемента ЗЛЛРЕТ 3 формируется логическая единица.

Логическая единица формируется также к на выходе второго элемента ИЛИ 6, выход которого соединен с управляющим входом блока 2 ключевых элементов . Информация, ранее занесенная в блок I триггеров. выводится тта ньтходную шину 14 данных. Если на вход ныбора 12 режима подана логическая единица, при поступлении сигналон на входы 9 и IO выборки на выходах элементов 3, 7, 6 и 5 в этом случае появляются логические единитвт. Осущестнттяется запись информации в блок

1 триггеров с одновременной передачей ее на выходную шину 14 данных.

Таким образом, в случае, когда на входе 15 управления режимом работы присутствует логическая единица, предлагаемый регистр функционирует аналогично прототитту.

Если на вход 15 управления режимом работы подан логический ноль, регистр настраивается на работу в многопроцессорной системе. В этом случае входы 9 и 10 испоттьзуются для выборки регистра процессором-приемником информации, а входы 11 и 12 для выборки регистра процессором-источником информации. Гистемная шина данных процессора-источника информации подключается к нхоцттой шине !3 данных, а системная птина данных процессора-приемника информации — к выходной шине 14 данных, В рассматриваемом режиме работы на выходах логических элементон 8 к 7 постоянно присутствует логический ноль, Работа регистра протекает следующим образом.

1Процессор-источник информации инициирует обмен. Для этого он вырабатывает сигналы выборки активного уровня, поступающие тта нходт>т 11 и 12. На выходе элемента ЗАПРЕТ 4 формируется логическая ециница, которая подается на первый вход элемента ИЛИ 5. На выходе последнего появляется логическая единица, которая вызывает запись информации с нходной шины 13 данных н блок 1 триггеров„ Так осуществляется прием информации из процессораисточника информации н регистр. Для ! считывания информации из регистра процессор-приемник информации вырабабывает сигналы активного уровня, поступающие на входы 9 и 10 устройства..

11а выходе элемента ЗЛПРЕТ 3 формируется логическая единица, поступающая на вход элемента ИГИ 6. На выходе последнего прянляется логическая едиттица-, которая вызывает открывание блока 2 кпточевьтх элементов. Информация из блока I триггеров поступает на выходную шину 14 данных, т.е. на системную шину данных процессораприемника инйормации.

Ф о р и у л а и з о б р е т е н и я

Буферный регистр, содержащий блок триггеров, блок ключевых элементов, ттервый элемент ЗАПРЕТ, прямой и инверсный входы которого являются первым и вторым входами выборки буферного регистра, второй элемент ЗАПРЕТ, прямой и иннерснььй входы которого явСоставитель А.Дерюгин

Техред И.Гайдош Корректор И.Демчик

Редактор А.Огар

Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР

TIo делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 4419/51

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

3 12511 ляются соответственно входами стробирования и выбора режима буферного регистра, первый и второй элементы ИЛИ и первый элемент И, причем входы первого элемента ИЛИ соединены с выхода- g ми второго элемента ЗАПРЕТ и первого элемента И, а выход первого элемента

ИЛИ соединен с входом записи блока триггеров, выход первого элемента

ЗАПРЕТ соединен с первыми входами 1О первого элемента И и второго элемента KIN, выход которого соединен с управляющим входом блока ключевых элементов, информационный вход блока триггеров является информационным

80 4 входом буферного регистра, выход блока триггеров соединен с входом блока ключевых элементов, выход которого является информационным выходом буферного регистра, о т л и ч а ю— шийся тем, что, с целью повышения быстродействия буферного регистра, в него введен второй элемент И,. выход которого соединен с вторыми входами первого элемента И и второго . элемента ИЛИ, первый вход соединен с инверсным входом второго элемента

ЗАПРЕТ, а второй вход является входом .управления режимом работы буферного регистра.