Устройство для контроля дешифратора

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах при контроле адресных трактов и в многоканальных устройствах коммутации. Целью устройства является повьппение достоверности контроля. Сигналы с выхода ; контролируемого дешифратора устанавливают в единичное состояние соответствующие триггеры группы блока сравнения и через первый элемент ИЛИ. опрашивает дублирующий дешифратор, информационные входы которого объединены с информационным входом контролируемого дешифратора. Выходы дублируклцего дешифратора устанавливают в нулевое состояние соответстгвующие триггеры группы блока сравнения . После этого через элемент задержки анализируется состояние группы триггеров. При ненулевом состоянии триггеров формируется сигнал неисправности . 1 ил. i

СОЮЗ СОЕЕТСНИХ

СОЦИАЛИСТИЧНжИХ

РЕСПУБЛИН (!9) (И) 4 G 06 F llil6

Е Г -ISA > i д

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3581540/24-24 (22) 20.04.83 (46) 23 . 08. 86 . Бюл. У 31 (72) Л.О.Беспалов (53) 681.3 (088.8) (56) Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ. — М: Мир, 1972, с. 228, фиг. 12.3.

Там же, с. 229, фиг,12.6. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТ0РА (57) Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах при контроле адресных трактов и в многоканальных устройствах коммутации. Целью устройства является повышение достоверности контроля. Сигналы с выхода:. контролируемого дешифратора устанавливают в единичное состояние соответствующие триггеры группы блока сравнения и через первый элемент ИЛИ . опрашивает дублирующий дешифратор, информационные входы которого обьединены с информационным входом контролируемого дешифратора. Выходы дублирующего дешифратора устанавливают в нулевое состояние соответст вующие триггеры группы блока сравнения. После этого через элемент задержки анализируется состояние группы триггеров. При ненулевом состоянии триггеров формируется сигнал неисправности. l ил.

1252783

20

Если деш ;фраторы 2 и 3 работают правильно, то к моменту поступления сигнала на второй вход первого элемента И группы 11 с выхода элемента

8 задержки все триггеры группы 10 будут находиться в нулевом состоянии

Изобретение относится к пифроной вычислительной технике и может быть использовано в запоминающих устройствах и многоканальных устройствах коммутации. 5

Цель изобретения. — повышение достоверности контроля.

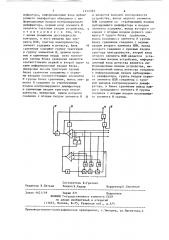

На чертеже приведена функциональная схема устройства для контроля дешифратора и подключенный к нему 1б контролирумый дешифратор.

Приняты следующие обозначения: регистр 1, контролируемый 2 и дублирующий 3 дешифраторы, элемент И 4, триггер 5 неисправности, элементы

ИЛИ 6 и 7, элемент 8 задержки, блок

9 сравнения, группа 10 триггеров блока 9 сравнения, группа 11 элементов И блока 9 сравнения, тактовый вход 12 устройства, информационный вход 13 устройства, выход 14 неисправности устройства, установочный вход 15 устройства.

Устройство работает следующим образом.

Дешифрируемый код с информационного входа 13 устройства поступает на регистр 1, с выхода которого поступает на информационные входы контролируемого 2 и дублирующего 3 дешифраторов. Сигнал опроса поступает с тактового входа 12 устройства на первый вход элемента И 4. В исходном состоянии триггер 5 неисправности находится в нулевом состоянии, поэтому сигнал опроса проходит через элемент И 4 на стробирующий вход контролируемого дешифратора 2 и единичный вход триггера 5 неисправности, запрещая прохождение оче40 редного импульса опроса.

Сигнал с выхода контролируемого дешифратор» 2 устанавливает в единичное состояние соответствующий триггер группы 10 и через первый элемент

ИЛИ 6 поступает на стробирующий вход дублирующего дешифратора 3 и элемента 8 задержки.

Сигнал с выхода дублирующего дешифратора 3 устанавливает в нулевое состояние соответствующий триггер группы 10. и сигнал с выхода элемента 8 задержки пройдет через последовательно соединенные элементы И группы 11 на вход второго элемента ИЛИ 7 и установит в нулевое состояние триггер неисправности. Таким образом, разрешается прохождение очередного сигнала опроса через элемент И 4.

В том случае, когда один из дешифраторов 2 и 3 неисправен, сигналы у них могут формироваться на разных выходах. При этом один из триггеров группы 10, установленный в единичное состояние сигналом с выхода дешифратора 2, не будет сброшен в нулевое состояние сигналом с выхода дешифратора 3. Сигнал с выхода элемента 8 задержки не пройдет на установку в нулевое состояние триггера 5 неисправности. На выходе 14 неисправности устройства при этом формируется нулевой ситнал > говорящий о неисправности дешифратора, и дальнейший опрос дешифратора 2 будет запрещен до того момента, пока триггер 5 неисправности не будет установлен в нулевое состояние сигналом начальных установок по установочному входу 15 устройства.

Если неисправность контролируемого дешифратора 2 приводит к отсутствию сигналов на его выходах, то и в этом случае триггер 5 неисправности останется в единичном состоянии, поскольку будет отсутствовать сигнал на выходе первого элемента

ИЛИ 6.

Выбранная структура блока 9 сравнения позволяет обнаружить короткие импульсные помехи, возникающие на выходах контролируемого дешифратора 2 в интервалах между сигналами опроса.

Состояние триггеров группы 10 блока 9 сравнения позволяет определить неисправный выход контролируемого дешифратора 2.

Формула изобретения

Устройство для контроля дешифратора, содержащее дублирующий дешифратор, блок сравнения и элемент И, причем группа выходов дублирующего дешифратора соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого соединена с группой выходов контролируемого де1252783

Составитель В.Гречнев

Редактор В.Петраш Техред В.Кадар Корректор Е . Снрохман

Заказ 4621/49 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г . Ужгород, ул. Проектная, 4 шифратора, информационный вход дублирующего дешифратора объединен с информационным входом контролируемого дешифратора, первый вход элемента И является тактовым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены два элемента ИЛИ, триггер неисправности, элемент задержки и регистр, блок 10 сравнения содержит группу триггеров и группу элементов И, причем нулевые и единичные входы всех триггеров группы блока сравнения являются соответственно первой и второй груп- 15 лами информационных входов блока, инверсные вьмоды триггеров группы блока сравнения соединены с первыми входами соответствующих элементов

И группы блока сравнения, выход эле- 211 мента И соединен со стробирующим входом контролируемого дешифратора и единичным входом триггера неисправности, инверсный выход которого соединен с вторым входом элемента И 25 и является выходом неисправности устройства, выход первого элемента

ИЛИ соединен со стробирующим входом дублирующего дешифратора и входом элемента задержки, вьмод которого со— единен r вторым входом первого элемента И груп ы блока сравнения, выход последне о элемента И группы блока сравнения соединен с первым входом второго элемента ИПИ, выход которого соединен с нулевым входом триггера неисправности, второй вход второго элемента ИЛИ является установочным входом устройства, информационный вход регистра является информационным входом устройства, информационный выход регистра соединен с информационным входом дублирующего дешифратора, группа входов первого элемента KIH соединена с группой выходов контролируемого дешифратора, в блоке сравнения выход каждого предыдущего элемента И группы соединен с вторым входом последующего элемента И группы.