Усилитель-ограничитель

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике и автоматике . Целью изобретения является повышение быстродействия усилителя-ограничителя . Усилитель-ограничитель содержит первый операционный усилитель , инвертирующий вход которого через первьй масштабньй резистор соединен с его выходом, являющимся выходом усилителя-ограничителя, и через второй масштабный резистор - с его информационным входом, неинвертирую ции ВХОД первого операционного усилителя через третий масштабный I e- зистор связан с вторым ннформацгюпным входом усилителя-ограничителя л через четвертый масштабный резистор - с шиной нулевого потенциала, второй операционный усилитель, выход которого через ключ, выполненный в виде последовательно и встречно включенных первого ключевого диода и стабнлитрога, и пятый маси табный резистор подключен к инвертирую цему входу первого операционного усилителя ti через второй ключевой диод - к его инвертирующему входу, между которым и ти- Г10Й нулевого пoтeнuИ(лa включены последовательно ограш чпванмций резистор и ncTO4jniK напряжения ограничения . Введение в усилитель-ограничитель третьего, четвертого и пятого масштабных резисторов и Hoot,rx связей -Между элементами позволяет умены;п ть постоянную времени усилителя ограничителя при работев режиме ограничения и тем самым достичь поставленной цели. 1 ил. Q , kf. v,fo i

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Я)4 G06 G 7 25

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Р >

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ щий вход первого операционного усилителя через третий масштабный резистор связан с вторым информационным входом усилителя-ограничителя и через четвертый масштабный резистор с ш>и ой нулевого потенциала, второй операционный усилитель, выхап, которого через ключ, выпо3?ненный в виде последовательно и встречно включенных первого ключевого диода и стабилитрона, и пятый масштабный резистор подключен к инвертирующему входу первого операционного усилителя и через второй ключевой диод — к его инвертирующему входу, между которым ir шиНой нулевого потенци»ла вклю >сны последовательно ограштчиван>щчй резистор и источник напряжения ограничения. Введение в усилитель-ограничитель третьего, четвертого и пятого масштабных резисторов и новых связей .между элементами позволяет уме>>ь>;п.ть постоянную времени усилитея» -ограничителя при работе в режиме ограничения и тем самым достичь поставленной цели. 1 ил.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3855362/24-24 (22) 11. 02.85 (46) 23. 08. 86. Бюп. № 31 (») Ульяновский политехнический институт (72) А.B.Eôèìoí, А.И.Зарукин и В.Н.Хаханин (53) 681.3(088.8) (56) Авторское свидетельство СССР № 826365, кл. С 06 G 7/25, 1979.

Авторское свидетельство СССР № 913405, кл. G 06 С 7/25, 1980. (54) УСИЛИТЕЛЬ-ОГРАНИЧИТЕЛЬ (57) Изобретение относится к аналоговой вычислительной технике и автоматике. Целью изобретения является повышение быстродействия усилителя-ограничителя. Усилитель-ограничитель содержит первый операционный усилитель, инвертирующий вход которого через первый масштабный резистор соединен с его выходом, являющимся выходом усилителя-ограничителя, и через второй масштабный резистор — с его информационным входом, неинвертируюГ. зК 12Ы799 А 1

1252799

Усилитель-ограничитель работает следующим Образом.

При выполнении условия (UI — U ) <

- U R„/R, на выходе Операционного усшгнтепя появляется напряжение, меньшее относи-.ельного опорного (U /U, U,, — напряжения на входах

7 и 5; R — сопротивление масштабных резисторов 4 и 6; Rz - сопротивление

55

Изобретение относится к аналоговой вычислительной технике и втоматике.

Цель изобретения — повышение быстродействия усилителя-ограничителя.

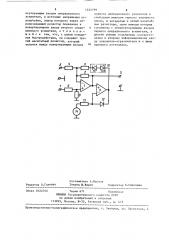

На чертеже показана электрическая схема усилителя-ограничителя.

Усилитель-ограничитель содержит первый операционный усилитель 1, пнвертирующий вход которого через пер- 10 вый масштабный резистор 2 соединен с

его выходом, являющимся выходом 3 усилителя-ограничителя, и через второй масштабный резистор 4 — с его информационным входом 5, неинвертирующий вход операционного усилителя

1 через третий масштабный резистор

6 связан с вторым информационным входом 7 усилителя-ограничителя и через четвертый масштабный резистор

8 с шиной нулевого потенциала, второй операционный усилитель 9, выход которого через ключ 10 выполненный в виде последовательно и встречно включенных первого ключевого диода

10.1 и стабнлитрона 10.2 и пятый масштабный резистор 11 псдключен к иниертпрующему входу операционного усилителя 1 и через второй ключевой диод 12 - к его инвертирующему вхо- 30 ду, между которым и шиной нулевого потенциала включены последовательно

Ограничивающий резистор 13 и источник 14 напряжения ограничения, а неипвертирующий вход подключен к выхо35 ду операционного усилителя 1 и выходу 3 усилителя-ограничителя.

Полярность включения полупроводниконых элементов соответствует ограничению положительного выходного напряжения сверху. При ограничении ,Отрицательного напряжения снизу по(1 .чярпость включения всех элементов изменяется на прот. воположную.

В случае Отрицател1 НОГО напряже 45 ния сверху стабплпгрон исключается из схемы, а при ограничении положительного напряжения снизу полярность ч1 люченпя диодов изменяется. масштабных резисторов 2 и 8).. Это приводит к появлению на выходе операционного усилителя 9 отрицательного напряжения. Ключ 10 закрывается и операционный усилитель 9 не влияет на работу дифференциального усилителя на операционном усилителе 1.

Ключевой диод 12 открывается замыкая петлю отрицательной обратной связи операционного усилителя 9 и предотвращая его насыщение.

Усилитель-ограничитель работает при этом в режиме усиления входного . дифференциального сигнала U - U с коэффициентом, определяемым масштабными резисторами 2, 4, 6 и 8 °

При возрастании входного дифференциального сигнала, как только будет выполняться (13< — U. ) U В.,>

10.2 ключа 10 и замыканию петли

1007-ной отрицательной обратной связи, включающей усилители 1 и 9, ключ

10 и резистор 11.

Напряжение пробоя стабилитрона

10.2 выбирается несколько большим максимально возможного напряжения огра ичения, что необходимо для надежного запиранпя ключевого диода 12.

На выходе усилителя-ограничителя в режиме ограничения поддерживается напряжение источника 14.

Ф о р м у л а и з о б р е т е н и я

Усилитель-Ограни петель, содержащий первый Операционный усилитель, между выходом и инпертирующим входом которого включен первый масштабный резистор, второй машстабный резистор, включенный между пнвертирующим входом первого операционного усилителя и первым информационным входом усилителя †ограничите, второй операционный усилитель, подсоединенный непннертирующим входом к выходу первого операционного усилителя, который является выходом усилителя-ограничителя, последовательно и встречно включенные первый ключевой диод и стабилитрон, подсоединенный свободным выводом к выходу второго операционного усилителя, второй ключевой диод, который включен между выходом и ин1252799

Составитель А.Маслов

Техред И.Верес Корректор Е. Сирохман редактор О. Головач

Заказ 4622/50

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 вертирующим входом операционного усилителя, и источник напряжения ограничейия, выход которого через ограничивающий резистор подключен к инвертирующему входу второго операционного усилителя, о т л и ч а ю— шийся тем, что, с целью повышения быстродействия, он содержит третий масштабный резистор, который включен между инвертирующим входом первого операционного усилителя и свободным выводом первого ключевого диода, и четвертый и пятый масштабные резисторы, одни выводы которых соединены с неинвертирующими входом первого операционного усилителя, а другие выводы подключены соответственно к второму информационному входу усилителя-ограничителя и к шине нулевого потенциала.