Устройство автоматической стабилизации мощности

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может использоваться в радиопередакяцих устройствахо Цель изо-, бретеяия - уменьшение bfbiimocTH, рассеиваемой транзисторами выходного усилителя модности (ВУМ) в переходном режиме. Входной сигнал поступает через регулируемый каскад 1, БУМ-2 и антенш 1Й согласующий блок 12 на антенну 13. Выходная мовшость ВУН 2 контролируется датчиком 3 выходной мощности. Сформированное им постоянное управляющее напряжение поступает на пороговый элемент (ПЭ) 4. Датчик остаточного напряжения (ДОН) 7 формирует напряжение, пропорциональное разности напряжения коллекторного питания ВУМ 2, которое поступает с управляемого источника питания 10 и выходного высокочастотного напряжения ВУМ 2, Это напряжение поступает на ПЭ 8 и на компаратор II. Если выходная мощность ВУМ 2 больше оптимальной , на выходе ГО 4 будет сигнал 1. Если сигнал с ДОН 7 меньше оптимального,на выходе ПЭ 8 появится сигнал I. В зависимости от этих сигналов, поступающих на элемент ИЛИ- НЕ 5, и сигнала с компаратора П дискретный интегратор 6 обеспечивает изменение напряжения возбуждения ВУМ 2, а дискретный интегратор 9 - увеличение напряжения управляемого источника питания, 1 ил. С

coos советсиих

СОЦИАЛИСТИЧЕСНИХ

PECflYBЛИН

1511 4 Н ОЗ С 3/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДФ СТВЕННЫЙ КОМИТЕТ СССР по лОмм изоаРетений и отнРцтю

К A STOPCHOIVtV СВИДЕТЕЛЬСТВУ (61) 1136306 (2l) 3867475/24-09 (22) 15.03.85 (46) 23.08.86. Вюл. II 31 (72) Ю. В. Корчагин, Л. А. Иорозова, В. А. Сметанников и И. С. Юнкес (53) 62).396.666(088.8) (56) Авторское свидетельство СССР

В 1136306, кл. Н ОЗ С 3/20, 1982. (54) УСТРОЙСТВО АВТОИАТИЧЕСКОЙ СТАБИЛИЗАЦИИ ИОЩНОСТИ (57) Изобретение относится к радиотехнике и может использоваться в радиопередающих устройствах. Цель изо-. бретения - уменьшение мощности, рассеиваемой транзисторами выходного усилителя мощности (ВУИ) в переходном режиме. Входной сигнал поступает через регулируемый каскад I, ВУИ 2 и внтенжй согласующий блок 12 на антенну !3. Выходная мощность ВУИ 2 контролируется датчиком 3 выходной

ÄÄSUÄÄ 1252915 A 2 мощности. Сформированное нм постоянное управляющее напряжение поступает на пороговый элемент (ПЭ) 4. Датчик остаточного напряжения (ДОН) 7 формирует напряжение, пропорциональное разности напряжения коллекторного питания ВУИ 2, которое поступает с управляемого источника питания 1О и выходного высокочастотного напряжения ВУИ 2. Это напряжение поступает на ПЭ 8 и на компаратор 11. Если выходная мощность ВУИ 2 больше оптимальной, на выходе ПЭ 4 будет сигнал "1". Если сигнал с ДОН 7 меньше оптимального,на выходе ПЭ 8 появится сигнал "1". В зависимости от этих ® сигналов, поступающих на элемент ИЛИНЕ 5, и сигнала с компаратора 11 дискретный интегратор 6 обеспечивает изменение напряжения возбуждения

ВУИ 2, а дискретный интегратор 9 — 3 увеличение нанряжения управляемого источника питания. 1 ил.

0 12529

Изобретение относится к радиотехнике, может быть использовано в радиапередающих устройствах и является усовершенствованием изобретения па основному авт. св. В 1136306. 5

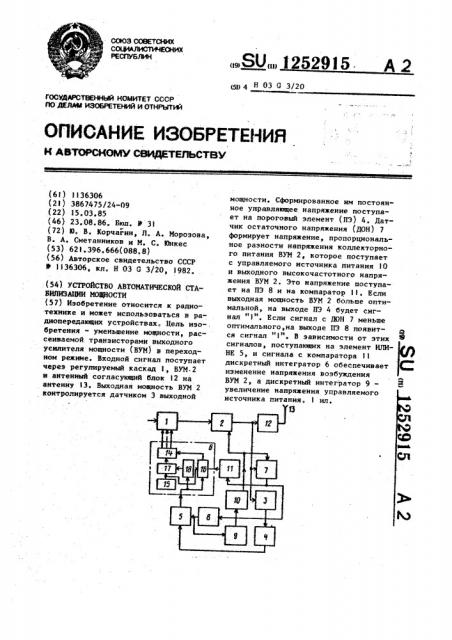

Целью изобретения является уменьжение мощности, рассеиваемой транзисторами выходного усилителя мощности в переходном режиме, На чертеже представлена структур- !О ная электрическая схема устройства автоматической стабилизации мощности.

Устройства автоматическои стабилизации мощности содержит регулируемый каскад 1, выходной усилитель 2 мощности, датчик 3 выходной мощности, пороговый элемент 4, элемент ИЛИНЕ 5, дискретный интегра-ор 6, датчик 7 остаточного напряжения, допол1 нительный пороговый элемент 8, дополнительный дискретный интегратор 9, управляемый источник 10 питания, кампаратор 11 антенный согласующий блок 12 н антенну 13, при этом дискретный интегратор содержит ревеасив25 ный счетчик 14, генератор 15 импульсов, первый и второй элементы И 16 и 17 и инвертор 18.

Устройство автоматической стабилизации мощности работает следующим образом.

Пусть нагрузкой выходного усили-! теля 2 мощности является антенна 13, подключенная к выходу выходного уси- 35 лителя 2 через антенный согласующий блок 12„ Тогда высокочастотная энергия с выхода выходного усилителя 2 мощности по фидеру поступает в антенну 13 через антенный согласующий 4О блок 12. Выходная мощность P выходного усили еля 2 мощности контролируется датчиком 3 выходной мощности, преобразуется в постоянное управляющее напряжение, которое поступает на вход 45 порогового элемента 4. Высокочастотное напряжение U с коллектора транзистора выходного усилителя 2 мощности поступает на вход датчика 7 остаточнога напряжения, на другой вход 50 которого поступает напряжение Е каллекторнага питания выходного усипителя 2 мощности. Напряжение с выхода датчика остаточного напряжения 7 пропорционально разности Е-U т.е. оста- 5» точному напряжению на коллекторе транзистора выходного усилителя 2 мощности, и поступает на входы дополнительнога порогового элемента 8 и компаратора 11.

В зависимости ат изменения импеданса нагрузки Е„ режим выходного усилителя 2 мощности при неизменном напряжении питания усилителя мощности может меняться ат перенапряженного, когда (Е-U) <1„„, а Е„ В„„„,, до йедонапряженного, когда (Е-Б) 1„, а Е„ В„,„, l,„„и R „,„., соответственна остаточное напряжение на коллекторе и сопротивление нагрузки выходного усилителя 2 мощности в оптимальном режиме.

Если 2„ !1„, то (Е U)<1.„,, а выходная мощйость P может быть как больше, так и меньше P

При Р>Р,„, на выходе порогового элемента 4 появляется сигнал логической "1", однако, поскольку (Е-Б) 1 „. на выходе дополнительного порогового элемента 8 появляется также сигнал логической "!", поэтому на выходе элемента ИЛИ"НЕ 5 появляется сигнал логического "0", по которому дискрет" ный интегратор 6 обеспечивает уменькение напряжения возбуждения и пропорциональное уменьшение тока и высокочастотного напряжения выходного усилителя 2 мощности. Одновременно сигнал логической "I" поступает с выхода дополнительного порогового элемента 8 на вход дополнительного дискретного интегратора 9, который обеспечивает увеличение напряжения управляемого источника 10 питания.

При P P „, на выходе порогового элемента 4 появляется сигнал логического "0", однако, поскольку (Е-U)

Формула изобретения

Составитель Л. Закс

Редактор Н. Коссей Техред Ч.Ходанич Корректор В. Синицкая

Заказ 4630/56 Тираж 816 Нодпис ное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб„, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 кого 0, по которому он обеспечии и вает уменьшение напряжения возбуждения. Такое уменьшение будет происходить до тех пор, пока с выхода дополнительного порогового элемента 8 не появится сигнал логического "0", т.е. когда разность (Е-U) будет больше 1,„ . Такой алгоритм работы необходим для того, чтобы предотвратить перегрузки усилителя 2 мощносв ти в процессе увеличения напряжения коллекторного питания Е при К„> R

Если Е «R „,, то (Е-U)+1 а

P P

Так как (E-11) 1 „„, то на выходе дополнительного порогового элемента 8 появляется сигнал логического

"0", по которому дополнительный дискретный интегратор 9 обеспечивает уменьшение напряжения коллекторного питания и, следовательно, остаточного напряжения на коллекторах транзисторов выходного усилителя. Так как Р Р,„, то на выходе порогового элемента 4 также появляется сигнал логического "0". Посколь-. ку на обоих входах элемента ИЛИ-НЕ 5 появляются сигналы логического "0", то на его выходе н на входе первого элемента И 16 дискретного интеграто- M, ра б появляется сигнал логической "1".

Однако увеличения выходного высокочастотного напряжения регулируемого каскада 1 не происходит, поскольку на выходе компаратора 11 присутствует сигнал логического "0", что свидетельствует об относительно большом остаточном напряжении на коллекторах транзисторов выходного усилителя 2 мощности, и не происходит увеличения мощности, рассеиваемой транзисторами выходного усилителя мощности в переходном режиме, Как только величина остаточного йапряжения достигнет некоторой величины 1.„,, где 1,„, 1 „.„, на выходе компаратора 1! появится сигнал логической "1", по этому сигналу дискретный интегратор 6 обеспечивает увеличение напряжения возбуждения и пропорциональное увеличение коллекторного тока выходного усилителя 2 мощности

Устройство автоматической стабилизации мощности по авт. св. 9 1136306 о т л и ч а ю щ е е с я тем, что, с целью уменьшения мощности, рассеиваемой транзисторами выходного усилителя мощности в переходном режиме, дискретный интегратор выполнен в виде реверсивного счетчика, выходы которого являются входом дискретного интегратора, а входы "Сложения" и

"Вычитания" подключены через первый и второй элементы И соответственно к выходу генератора импульсов, к второму входу второго элемента И подкхкочен инвертор, вход которого подключен к второму входу первого элемента И и является входом дискретного интегратора, при этом между выходом датчика остаточного напряжения и третьим входом первого элемента И включен компаратор, порог срабатывания которого превышает порог сраба" тывания дополнительного порогового элемента.