Преобразователь логических уровней

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано для согласования уровней логических сигналов схем МЦП-логики с различными элементами на биполярных транзисторах. Целью изобретения является повьшение нагрузочной способности . Для достижения цели в преобразователь , содержащий входной ЩЩ- транзистор 1 с каналом h-типа, выходной h-р-п-транзистор 2, резистор 3, р-h-p-транзисторы 5 и 6, вход 10, шину питания 11, выход 12, введейЫ дополнительные р -vi-p-транзисторы 7 и 8, дополнительныйh-р-п-транзистор 9 и дополнительный резистор 4. Транзисторы 7, 9 и резистор 4 образуют неинвертирующий усилитель, служаирш для увеличения нагрузочной способности преобразователя. Транзистор 6 предназначен для устранения фактора нестабильности, а транзистор 8 - для согласования с базовой цепью выходного транзистора 2, что способствует его надежному закрытию в другом состоянии преобразователя. 1 ил. 12 СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (!1) (511 4 Н 03 K 19/00

А1 ч( с1 (Яс1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

И A BTOPCHQMV СВИДЕТЕЛЬСТВУ (21) 3860940/24 21 (22) 01.03.85 (46) 23.08.86. Бюл. К 31 (71) Московский институт радиотехники, электроники и автоматики (72) Д.В. Игумнов, Г.П. Костюнина, И.С. Громов и Г.В. Королев (53) 621.374(088.8) (56) Мкртчян С.О. Преобразователи уровней логических элементов. М.:

Радио и связь, 1982, с. 40, рис.31.

Авторское свидетельство СССР

Р 1094150, кл. Н 03 К 19/00, 1983. (54) ПРЕОБРАЗОВАТЕЛЬ ЛОГИЧЕСКИХ УРОВНЕЙ (57) Изобретение относится к импульсной технике и может быть использовано для согласования уровней логических сигналов схем ИДП-логики с различными элементами на биполярных транзисторах. Целью изобретения является повышение нагрузочной способности. Для достижения цели в преобразователь, содержащий входной МДПтранзистор 1 с каналом .м -типа, выходной -p-n транзистор 2, резистор

3, р -n-v-транзисторы 5 и 6, вход 10, шину питания 11, выход 12, введены дополнительные р - -р-транзисторы 7 и

8, дополнительный a -p-h-транзистор 9 и дополнительный резистор 4. Транзисторы 7, 9 и резистор 4 образуют неинвертирующий усилитель, служащий для увеличения нагрузочной способности преобразователя. Транзистор 6 предназначен для устранения фактора нестабильности, а транзистор 8— для согласования с базовой цепью выходного транзистора 2, что способствует его надежному закрытию в другом состоянии преобразователя, 1 an.

1 125

Изобретение относится к импульсной технике и может быть использовано для согласования уровней логических сигналов схем МДП-логики с различными элементами на биполярных транзисторах, например транэисторнотранзисторной логики (ТТЛ).

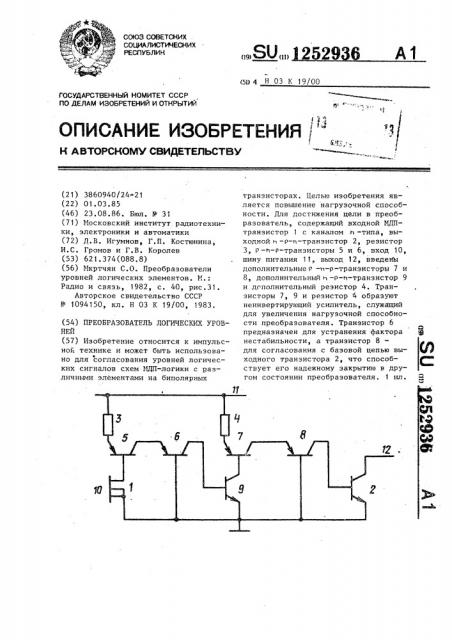

Цель изобретения — повышение нагрузочкой способности, На чертеже представлена принципиальная схема предлагаемого преобразователя.

Преобразователь логических уровней содержит входной ИДП-транзистор с каналом а-типа, выходной и -р-лтранзистор 2, резистор 3 и дополнительный резистор 4, первый 5 и второй

6 p -q-p-транзисторы, первый 7 и второй 8 дополнительные р -h-v-транзисторы и дополнительный r -р- -транзистор 9, исток и подложка МДП-транзистора 1 соединены с эмиттерами транзисторов 2 и 9, базами транзисторов 6 и 8 и с общей шиной устройства, затвор IQII-транзистора 1 подключен к входу устройства 10, а сток — к базе транзистора 5, эмиттер которого через резистор 3 соединен шиной 11 питания.

Коллектор транзистора 5 соединен с эмиттером транзистора 6, коллектор которого соединен с базой транзистора 9, а коллектор транзистора 9 — с базой транзистора 7, змиттер которого через резистор 4 соединен с ши-. . . ной 11 питания, коллектор транзистора

7 соединен с эмиттером транзистора 8, коллектор которого соединен с базой выходного транзистора 2, коллектор которого подключен к выходу 12 устройства. !

При запертом ИДП-транзисторе 1 ток стока не протекает, поэтому и ч ок в цепи базы выходного транзистора 2 равен нулю.

При открытом входном ИДП-транзисторе в цепи его стока будет протекать ток, который является и током эмиттера транзистора 5. Преобразуясь транзисторами 5 и 6, работающими в инжекционном режиме, этот ток будет протекать в цель базы транзистора 9 и поддерживать его в открытом состоянии.

Ток коллектора транзистора 9 является током эмиттера транзистора 7.

Преобразуясь транзисторами 7 и 8, работающими в инжекционном режиме, этот ток будет протекать в цепь базы выходного транзистора 2, поддерживая его открытое состояние.

2936

Поскольку входной МДП-транзистор

1 в открытом состоянии обладает значительным остаточным напряжением(!

ocr (десятые доли вольта), напряжение между коллектором транзистора 5 и общей шиной имеет величину большую, чем инжекционное напряжение транзистора 5, на!О„,, которое является фактором нестабильности. Транзистор

1Q 6 устраняет влияние!!.„ и между его коллектором и общей шиной уже будет иметь место только инжекционное напряжение. TQK базы транзистора 9 будет несколько меньше тока стока вход-!

5 ного МДП-транзистора 1. Транзистор 9 вместе с резистором 4 и транзистором

7 образует неинвертирующий усилитель; служащий для увеличения нагрузочной способности преобразователя. Транзистор 8 служит для согласования с базовой цепью выходного транзистора 2, подцерживая необходимый выходной ток в одном состоянии преобразователя уровней и способствуя надежному закрытию выходного транзистора 2 в друом состоянии преобразователя.

Формула изобретения

ЗО

Преобразователь логических уровней, содержащий входной МДП-транзистор, затвор которого подключен к входу преобразователя, основной резистор, первый вывод которого подключен к шине питания, два основных

p-e-p-транзистора, база первого иэ которых соединена со стоком МДП-транзистора, и выходной и -р- -транзистор, эмиттер которого соединен с базой второго р -o-р-транзистора, истоком МДП-транзистора и общей шиной, а коллектор подключен к выходу преобразователя. о т л и ч а ю щ и йс я тем, что, с целью повышения нагрузочной способности, в него введены два дополнительных P -- -р-транзистора, дополнительный а --р- -транзистор и дополнительный резистор, эмиттер первого дополнительного р о л-р-транзистора через дополнительный резистор подключен к шине питания, база соединена с коллектором дополнительного "р-h-òðàíýèñòîðà, эмиттер которого соединен с общей шинои

Ы и базой второго дополнительного р—

ii-Р-транзистора, коллектор которого соединен с .базой выходного о --р-итранзистора, змиттер - с коллектором

Составитель А, Янов

Техред Л.Сердюкова

Корректор И. Самборская

Редактор А. Козориэ

Заказ 4631/57 Тирам 816

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раутская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 1252936 4 первого дополнительного р-ri-p-тран- тор которого соединен с эмиттером зистора, второй вывод основного ре- второго основного Р-n-p-транзистора, зистора соединен с эмиттером первого коллектор которого соединен с базой основного р -л-р-транзистора, коллек- poïoëíèòåëüíîãî t --p-h-транзистора