Цифровой синтезатор частоты

Иллюстрации

Показать всеРеферат

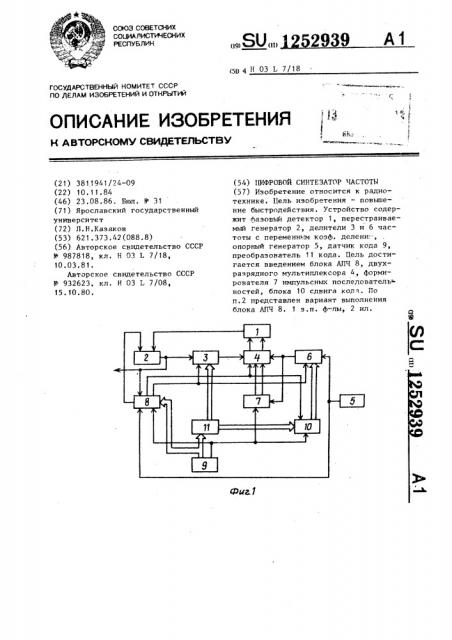

Изобретение относится к радиотехнике . Цель изобретения - повышение быстродействия. Устройство содержит фазовьй детектор 1, перестраиваемый генератор 2, делители 3 и 6 частоты с переменньм коэф. деление, . опорный генератор 5, датчик кода 9, преобразователь 11 кода. Цель достигается введением блока АЦЧ 8, двухразрядного мультиплексора 4, формирователя 7 импульсных последователь - ностей, блока 10 сдвига кодч. Цо п.2 представлен вариант выполнения блока АГГЧ 8. 1 з.п. ф-.пы, 2 ил. Фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИК

2939 А1 (19) (11) (sg 4 Н 03 L 7/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А BTOPCHQMY СВИДЕТЕЛЬСТВУ (21) 3811941/24-09 (22) 10 ° 11.84 (46) 23.08.86. Вюл. 1(31 (71) Ярославский государственный университет (72) Л.Н.Казаков (53) 621.373.42(088.8) (56) Авторское свидетельство СССР

1(987818, кл. Н 03 ? 7/18, 10.03.81.

Авторское свидетельство СССР

Р 932623, кл. Н 03 L 7/08, 15. 10. 80. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение быстродействия. Устройство содержит фазовый детектор 1, перестраиваемый генератор 2, делители 3 и 6 частоты с переменным коэф. делени., опорный генератор 5, датчик кода 9, преобразователь 11 кода. Цель достигается введением блока АПЧ 8, двухразрядного мультиплексора 4, формирователя 7 импульсных последователь ностей, блока 10 сдвига кодч. По п.2 представлен вариант выполнения блока АПЧ 8. 1 s.ï. ф-.пы, 2 ил.

1252939

Изобретение относится к радиотех- нике и может быть использовано B системах радиосвязи и в контрольноизмерительной аппаратуре.

Пель изобретения — повышение быстродействия.

На фиг.! представлена структурная электрическая схема цифрового синтезатора частоты," на фиг.2 — вариант выполнения блока автоподстрой- Ю ки 3ястоты е

Пифровой синтезатор частоты содержит фазовый детектор (ФД) 1, перестраиваемый генератор 2, первый делитель 3 частоты с переменным ко- 15 эффициентом деления (ДПКД), двухразрядный мультиплексор 4, опорный генератор 5, второй ДПКД 6, формирователь 7 импульсных последовательнос -.ей (ФИП), блок 8 автоподстройки 20 частоты (БЛП), датчик 9 кода, блок

10 сдвига кода и преобразователь 11 кода.

Блок автоподстройки частоты при этом содержит двоичный счетчик 12, 25 первый 13 и второй 14 сумматоры кодов, и-разрядный мультиплексор 15, регистр 16 кода частоты, цифроаналоговый преобразователь (ЦАП) 17, дешифратор 18, первый 19 и второй 20 gg триггеры, делитель 21 частоты, первый формирователь 22 импульсов, элемент 23 задержки, второй формирователь 24 импульсов °

1 ийровой синтезатор частоты рабо35 тает следующим образом.

При смене частоты из датчика 9 кода на вход преобразователя 11 кодов и информационный вход БАПЧ 8 поступает двоичный код К;-й частоты, одновременно с другого выхода датчика кода 9 командный импульс обнуляет ФИП 7 и через вход включения

БАПЧ 8 устанавливает в единичное со45 стояние первый 19 и второй 20 триггеры. Преобразованный в преобразователе f1 кода код новой частоты М с первого выхода поступает на установочный вход первого ДПКД 3, а с

l второго выхода код N; переписывается задним фронтом командного импульса с второго выхода датчика 9 кода, поступающего на вход параллельной записи блока 10 сдвига через информационньпr вход в универсальный сдвиговый регистр (не показан), входящий в состав блока 10 сдвига, разрядность сдвигового регистра больше на единицу разрядности максимально возможного кода на информационном входе блока 10 сдвига. При этом вход старmего разряда сдвигового регистра зануляется, а на информационный вход второго ДПКД 6 с выхода блока 10 сдвига, наоборот, подается код старших разрядов, а самый младший не используется, Таким образом, после параллельной записи на информационный вход второго ДПКД 6 будет поступать код, равный и.

2 где en — целая часть числа.

Соответственно на выходе второго

ДПКД 6 появляются импульсы с частотой в два раза выше частоты сравнения в кольце фазовой автоподстройки, они поступают на вход синхронизации

ФИП 7, в котором .формируется меандр с частотой, равной частоте сравнения, по заднему и переднему фронту меандра формируются короткие импульсы, таким образом, из последовательности с удвоенной частоты ФИП 7 формирует две последовательности с частотой, практически равной частоте сравнения кольца ФЛПЧ, и сдвинутых одна относительно другой на %, С выхода второго триггера 20 к этому времени на управляющий вход двухразрядного мультиплексора 4 приходит высокий уровень и сформированные сдвинутые последовательности с выхода ФИП 7 через двухразрядный мультиплексор 4 поступают на входы ФД 1, на выходы которого автоматически устанавливается постоянное напряжение, соответствующее средней части характеристики детектора, кольцо фазовой автоподстройки при этом размыкается.

Далее высокий уровень с выхода второго триггера 20 разрешает работу делителя 21 частоты и на его выходе формируется меандр, высокий уровень которого разрешает двоичному счетчику 12 вести счет периодов сигнала с выхода перестраиваемого генератора 2, а низкий запрещает.

Первым импульсом, сформированным первым формирователем 22 по отрицательному фронту меандра, код К. с

1 выхода датчика 9 кода через п-разрядный мультиплексор 15 переписывается в регистр 16, затем с помощью

1252

ПАП 17 преобразуется в аналоговое напряжение и осуществляет начальную установку перестраиваемого генератора 2. Затем этот же импульс, задержанный элементом 23 задержки, 5 сбрасывает первый триггер 19 в нулевое состояние, который подключает через п-разрядный мультиплексор 15 к входу регистра 16 выход второго сумматора 14, этот же импульс обну- !О ляет двоичный счетчик 12 °

К моменту поступления на вход разрешения двоичного счетчика 12 очередного высокого уровня с делителя 2! частоты на его входе синхро- f5 низации будет присутствовать частота, соответствующая начальной установке перестраиваемого генератора 2, Код числа сосчитанных импульсов за время разрешения, которое выбирается gg из соображений требуемой точности подстройки и задается соответственно частотой опорного генератора 5 и коэффициентом деления делителя 21 частоты (в общем случае на выходе дели- 25 теля 21 частоты может быть не меандр), сравнивается в первом сумматоре 13 с кодом К,.

Если требуется точность подстройки более высокая чем шаг частоты цифрового синтезатора частоты, то во входной код на входе первого сумматора 13 младшими разрядами добавляется необходимое количество нулей, чтобы выравнять веса младших разря- 3S дов. Далее на первый сумматор 13 код с выхода двоичного счетчика 12 поступает в инверсном виде, поэтому первый сумматор 13 автоматически проводит операцию вычитания иэ вход- 40 ного кода двоичного счетчика 12. Получаемая разность складывается во втором сумматоре 14 с выходным кос дом регистра 16, а результат снова переписывается очередным импульсом с 43 вьжода элемента 23 задержки регистра

16. Весь этот процесс повторяется.

На выходе первого сумматора 13 стоит дешифратор 18, который дешифрует нулевое значение кода с выхода пер- 5О вого сумматора 13 с точностью до младшего разряда. При наличии такого кода на входе дешифратора 18 на его выходе появляется импульс, который сбрасывает второй триггер 20 в нулевое состояние, соответственно на выходе окончания подстройки БАПЧ 8 появляется низкий уровень, что гово939 4 рит о том, что процесс подстройки частоты перестраиваемого генератора с заданной точностью окончен.

По отрицательному перепаду на выходе второго триггера 20 второй формирователь 24 формирует импульс, который осуществляет предустановку делителей ДПКД 3 и 6 в состояния, соответствующие кодам на кодовых входах, а именно первый ДПКД 3 в состояние, равное значению своего коэфI фициента деления Y., второй ДПКД 6

1 в состояние, равное епс(й./g). Нуле-! вой -уровень выхода второго триггера

20 переводит двухразрядный мультиплексор в противоположное состояние, а на входы ФД 1 будут поступать импульсные последовательности непосредственно с выходов первого 3 и второго 6 ДПКД (кольцо фазовой автоподстройки замкнется), а если учесть, что к этому времени частота перестраиваемого генератора 2 близка к требуемой ("захвачена") и соответственно периоды сигналов на выходах первого и второго ДПКД 3 и 6 достаточно близки, то с учетом предустановок разность фаз на входах ФД 1 сразу же после смены управления двухразрядным мультиплексором 4 вновь будет близка к ff,. что приведет к тому, что переходный процесс на выходе ФД 1 све-, дется к минимуму.

Импульс с выхода второго триггера

20 своим отрицательным фронтом также осуществит последовательный сдвиг информации в блоке 10 сдвига, после чего на вход второго ДПКД 6 поступит

I код, равный N,, при этом второй ДПКД

6 автоматически на втором цикле деления перейдет в нормальный режим деления.

Осуществление предустановки второго ДПКД 6 и обнуление ФИП 7 при включении БАПЧ 8 необходимо, чтобы избежать скачков напряжения на вьжоде ФД 1 в начальный момент частотной автоподстройки. В качестве ФД 1 может служит устройство выборки-запоминания, перестраиваемый генератор 2 может быть выполнен по схеме LC-автогенератора с двумя входами управления, в качестве ДПКД 3 и 6 могут быть использованы делители с переменным коэффициентом деления типа

133ИЕ7, 53ОИЕ 17, в качестве двухразрядного мультиплексора 4 — сдвоенные мультиплексоры "четыре н один" и

125? 9 "19 Ь и N„, при этом выходная частота определится как

yr>

: Е.. в „i; N

50

5 счетверенный мультиплексор два в один".

При этом выходы первого 3 и второго 6 ДПКД образуют первую пару информационных входов двухразрядного мультиплексора, а два выхода ФИП 7 образуют вторую пару информационных входов двухразрядного мультиплексора

4. ФИП 7 может состоять из триггера и двух одинаковых формирователей, выполненных на простой логике, подключенных соответственно к прямому и инверсному выходам триггера, вход синхронизации триггера является входом синхронизации ФИП 7, вход обнуления триггера является входом обнуления ФИП 7, а выходы формирователей являются первым и вторым выходами

ФИП 7.

Блок 10 сдвига может быть выполнен на основе универсального сдвигового регистра, информационный вход которого является информационным входом блока 10 сдвига, и два формирователя, выполненные на простой логике, вход первого из них является входом параллельной записи блока

10 сдвига, а выход подключен к входу параллельной записи С2 универсального сднигового регистра, вход второго формирователя соединен с управляющим входом управления Ч универсального сдвигового регистра и является входом блока 10 сдвига, а выход подключен к входу синхронизации С1 универсального сдвигового регистра, по которому осуществляется сдвиг информац п . Преобразователь 11 кода может быть выполнен, например, в виде двух постоянных запоминающих устройств (Hp- показаны), адресные входы которых соединены между собой и являются входом преобразователя 11 кода, а выходы первого и второго постоянных запоминающих устройств являются соответственно первым и вторым выходами преобразователя 11 кода, вычисление кодов и их запись в постоянное запоминающее устройство проводится заранее по следующему алгоритму.

Коэффициенты М, и N, связывающи выходную частоту синтезатора с опорной частотой следующим образом:

: 1 4, 8 к!» No o заменяются новой парой коэффициентов

N. u N. меньших соответственно И"

Ф 1

Вычисленные значения коэффициентов Y. и У,. заносятся в ячейку со1 1 ответственно первого и второго постоянных запоминающих устройств с адресом определяемым двоичным кодом К, задаваемым датчиком 9 кода, однозначно связанным со значением выходной частоты цифрового синтезатора частот и равным М,.

Таким образом, при поступлении на вход преобразователя 11 кода некоторого кода К; с выхода первого и вто-. рого постоянных запоминающих устрой-! 1 ств считываются коды N, .и N., записанные в ячейки с адресами К; (другим примером конкретного выполнения преобразователя 11 кода может служить использование вместо постоянных запоминающих устройств вычислительного устройства, которое непосредственно в процессе работы осуществит вычисление коэффициентов Y.

1 и К, по заданному К.) .

Предлагаемый цифровой синтезатор частоты обладает повышенной скоростью перестройки по частоте, что позволяет использовать его в различных радиосистемах, предъявляющих повышенные требования к быстродействию систем.

Формула изобретения

Цифровой синтезатор частоты, содержащий последовательно соединенные фазовый детектор, перестраиваемый генератор и первый делитель частоты е переменным коэффициентом деления, последовательно соединенные опорный генератор и второй делитель частоты с переменным коэффициентом деления, последовательно соединенные датчик кода частоты и преобразователь кода, первый выход которого подключен к кодовому входу первого делителя частоты с переменным коэффициентом деления, отличающийся тем, что, с целью повышения быстродейст55. вия, введены блок автоподстройки частоты и двухразрядный мультиплексор, формирователь импульсных последовательностей и блок сдвига кода, кодовый вход и выход которого соединены

1252939 соответственно с BTopblM выходом преобразователя кода и с кодовым входом второго делителя частоты с переменным коэффициентом деления, уста— новочный вход которого объединен с установочным входом первого делителя частоты с переменным коэффициентом деления и подключен к установочному выходу блока.автоподстройки частоты, опорный вход которого соединен с вы- 10 ходом опорного генератора, управляющий вход, блока сдвига кода объединен с управляющим входом двухразрядного мультиплексора и подключен к выходу сигнала окончания подстройки 5 блока автоподстройки частоты, сигнальный вход и выход сигнала подстройки которого соединены соответственно с выходом и с управляющим входом перестраиваемого генератора, 20 информационный вход блока автоподстройки частоты подключен к первому выходу датчика кода, вход включения блока автоподстройки частоты объединен с входом параллельной записи блока сдвига кода и с входом обнуления формирователя импульсньх последовательностей и подключен к второму выходу датчика кода, выход второго делителя частоты с переменным ко- ЗО эффициентом деления соединен с вхоом синхронизации формирователя импульсных последовательностей, а также с первым информационным входом двухразрядного мультиплексора, к второму информационному входу двухразрядного мультиплексора подключен выход первого делителя частоты с переменньм коэффициентом деления, пЕрвый и второй выходы формирователя 4П импульсных последовательностей соединены соответственно с третьим и четвертым информационными входами двухразрядного мультиплексора, первый и второи выходы которого подклю- 45 чены соответственно к первому и Bto рому входам фазового детектора.

2, Синтезатор по п.1, о т л и— ч а ю шийся тем, что блок автос

1 подстройки частоты содержит последовательно соединенные делитель частоты, двоичный счетчик, первый сумматор кодов, второй сумматор кодов, и-разрядный мультиплексор, регистр кода частоты и цифроаналоговый преобразователь, последовательно соединенные первый формирователь импульсов, элемент задержки и первый триггер, выход которого соединен с управляющим входом и-разрядного муль" типлексора, последовательно соединенные второй триггер и второй формирователь импульсов, а также дешифратор, информационный вход и выход которого соединены соответственно с выходом первого сумматора кодов и с первым входом второго тригге ра, второй вход которого объединен с вторым входом первого триггера и является входом включения блока автоподстройки частоты, стробирующий вход дешифратора объединен с управляющим входом регистра кода частоты и подключен к выходу первого формирователя импульсов, выход регистра кода частоты соединен с вторым входом второго сумматора кодов, управляющий вход и выход делителя частоты соединены соответственно с выходом второго триггера и с входом первого формирователя импульсов, выход элемента задержки соединен с входом обнуления двоичного счетчика, второй вход первого сумматора объединен с вторым информационным входом п-разрядного мультиплексора и является информационным входом блока автоподстройки частоты, при этом входы синхронизации делителя частоты и двоичного счетчика являются соответственно опорным и сигнальным входами блока автоподстройки частоты, а выходы цифроаналогового преобразователя, второго триггера и второго формирователя импульсов являются соответственно выходом сигнала подстройки, выходом сигнала окончания подстройки и установочным выходом блока автоподстройки частоты.

1252939

Составитель Ю.Ковалев

Техред Л.Сердюкова. Корректор В.Синицкая

Редактор А.Козориз

Заказ 4631/57 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4