Преобразователь цифрового кода в частоту следования импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к вьгаислительной технике, а именно к кодированию и преобразованию информации. и может быть использовано в цифровых регуляторах, в цифровых прЪграммных системах управления и т.д. Целью изобретения является повышение быстродействия и расширение функциональных возможностей преобразователя . за счет синхронизации ввода кода частоты и обеспечения возможности модулирования выходной частоты по любому закону. По сигналу па шине 19 управления триггер 6 открывает ключ 9, в результате чего выходной импульс с выходной шины 16 осуществляет запись информации с шины 18 кода адреса задаваемой частоты в регистр 14 хранения, устанавливая при этом с SS (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (я) 4 Н 03 M 1/86

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

FAx

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3838143/24-24 (22) 08.01,85 (46) 23.08.86. Бюл. № 31 (72) В.Г.Байтеряков, Б.П.Касич и P.Â.Галиев (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 482893, кл. Н 03 К 13/20, 1973.

Авторское свидетельство СССР № 1084982, кл. Н 03 К 13/02, 1982. (54) ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА

В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ (57) Изобретение относится к вычислительной технике, а именно к кодированию и преобразованию информации, „. Я0„, 252943 А 1 и может быть использовано в цифровых регуляторах, в цифровых прЬграммных системах управления и т.д. Целью изобретения является повьппение быстродействия и расширение функциональных возможностей преобразователя. за счет синхронизации ввода кода частоты и обеспечения воэможности модулирования выходной частоты IIo любому закону. По сигналу на шине 19 управления триггер 6 открывает ключ

9, в результате чего выходной импульс с выходной шины 16 осуществляет запись информации с шины 18 кода адреса задаваемой частоты в регистр

14 хранения, устанавливая при этом

1252943

20

35 в исходное состояние делитель 1 частоты, регистр 2 сдвига, управляемый делитель 3 частоты, счетчик 4 импульсов и счетчик 13 адреса. Тот же выходной импульс через элемент 7 задержки увеличивает содержимое счетчика 13 адреса на единицу. На выходе управляемого делителя частоты 3 из опорной частоты, поступающей по шине 15, с помощью делителя i частоты и регистра 2 сдвига формируется импульсная последовательность, поступающая на вычитающий вход счетИзобретение относится к вычислительной технике, а именно к кодированию и преобразованию информации, и может быть использовано в цифровых регуляторах, в цифровых программных системах управления и т.д.

Цель изобретения — повьппение быс родействия и расширение функ— циональных возможностей преобразователя за счет синхронизации ввода кода задаваемой частоты и обеспечения возможностей модулирования выходной частоты.

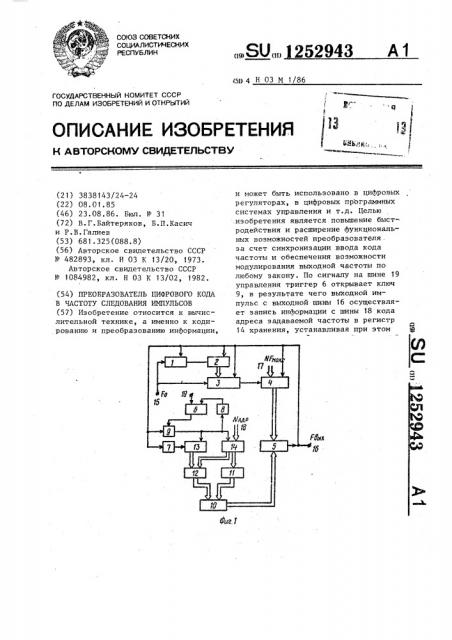

На фиг ° 1 приведена структурная электрическая схема преобразователя цифрового кода в частоту следования импульсов, на фиг.2 и 3 — временные циаграммы работы преобразователя.

Преобразователь содержит делитель 1 частоты, регистр 2 сдвига, управляемый делитель 3 частоты, счетчик 4 импульсов, блок 5 сравнения кодов, триггер 6, элементы 7-и 8 задержки, ключ 9 сумматор 10, запоминающие устройства 11 и 12, счетчик

13 адреса, регистр 14 хранения, шину 15 опорной частоты, выходную .шину 16, шину 17 кода постоянного числа, шину 18 кода адреса задаваемой частоты, шину 19 управления.

Преобразователь цифрового кода в частоту следования импульсов работает следующим образом.

Ввод в преобразователь нового ко"да адреса задаваемой частоты производится через шину 18 и сопровождается появлением на шине 19 управлечика 4 импульсов, где записано постоянное число, поступающее по шине

i7. Содержимое счетчика 4 сравнивается в блоке 5 сравнения кодов с содержимым сумматора 10. В сумматоре

10 формируется сумма кода задаваемой частоты, поступающего из запоминающего устройства 11 по адресу в регистре 14, и кода приращения частоты, поступающего из запоминающего устройства 12 по адресу в регистре 14 и счетчике 13 адреса. 3 ил. нйя импульсного сигнала ввода, который устанавливает триггер 6 в единичное состояние, формируя тем самым на первом входе ключа 9 разре- шающий потенциал, который открывает ключ 9, что обеспечивает в момент поступления очередного импульса на выходную шину 16, запись в регистр

14 хранения по шинам 18 кода адреса задаваемой частоты, установку в "0" счетчика 13 адреса и через элемент

8 задержки установку в "О" триггера

6. Низкий потенциал на выходе триггера 6 создает на первом входе ключа 9 запрещающий потенциал и ключ 9 закрывается до следующего ввода кода-адреса задаваемой частоты. В тот момент поступления очередного импульса на выходную шину 16 делите-ли 1 и 3 частоты устанавливаются в

"0", в счетчик 4 импульсов по шинам

17 записывается начальное число, в регистр 2 сдвига записывается код единицы, а на счетный вход счетчика

25, 13 адреса через элемент задержки поступает импульс, увеличивающий на единицу код в счетчике 13 адреса.

Длительность указанных операций, выполняемых одновременно и с задержкой, не превьппает периода опорной частоты, после чего начинается очередной цикл формирования периода вы.ходной частоты.

На выходе управляемого делителя

3 из опорной частоты с помощью делителя 1 частоты и регистра 2 сдвига вырабатывается частотная последова1252943

5 о

ZO

55 тельность импульсов в соответствии с фиг.2. Импульсы с выхода управляемого делителя 3, поступая на вычитающий вход счетчика 4 импульсов, уменьшают первоначально записанный в него код.

Процесс уменьшения кода в счетчике 4 импульсов продолжается до тех пор, пока он не станет равным коду частоты, установленному на вторых входах блока 5 сравнения кодов.

Код частоты, устанавливаемый на вторых входах блока 5 сравнения кодов, представляет собой сумму кода задаваемой частоты Г „. и кода приращения частоты ьР., образующуюся на выходе сумматора 10. Код задаваемой частоты F поступает на первый вход сумматора 10 с выхода первого запоминающего устройства 11 и выбирается иэ ячейки запоминающего устройства, код адреса которой записан в регистре 14 хранения и поступает на входы первого запоминающего устройства 11 с первых выходов регистра 14 хранения.

С вторых выхоцов регистра 14 хранения на первые входы второго запоминающего устройства 12 поступает код старших разрядов адресов ячеек запоминающего устройства, содержащих коды приращений частоты аF, . Младшие разряды адресов ячеек запоминающего устройства формируются в счет чике 13 адреса и с его выхода поступают на вторые входы второго запо-. минающего устройства 12. Разрядность счетчика 13 адреса определяется количеством периодов выходной частоты

Т., укладываюшихся в один период Т— повторения модулирующей составляющей выходной частоты (фиг.3), В счетчике l3 адреса происходит непрерывное изменение кода на едини-, цу перед каждым циклом формирования периода выходной частоты, что позволяет в начале каждого цикла формирования периода выходной частоты выбирать из второго запоминающего устройства. 12 очередное значение кода приращения частоты лГ,, которое с выхода второго запоминающего устройства 12 поступает на второй вход сумматора 10, на выходе которого формируется код текущего значения задаваемой частоты, который подается на вторые входы блока 5 сравнения кодов.

В момент совпадения кода, поступающего на первые входы блока 5 срав- - нения кодов с кодом, установленным на вторых входах блока 5 сравнения кодов, на его выход поступает импульс, который завершает формирование очередного периода выходной частоты и блоки устройс.тва соответственно устанавливаются в исходное положение.

Изменение формируемого периода выходной частоты происходит немедленно, что обеспечивает хорошие динамические свойства преобразователя.

Непрерывный счет в счетчике 13 адреса с возобновлением счета с начального кода при его переполнении обеспечивает поступление на второй вход сумматора 10 циклически повторяющихся значений кодов приращений частоты, что позволяет получать на выходе преобразователя любой периодически повторяющийся закон изменения частоты.

Формула из обрете ния

Преобразователь цифрового кода в частоту следования импульсов, содержащий делитель частоты, сч тный вход которого объединен со счетным входом управляемого делителя частоты и является шиной опорной частоты, а выход соединен с управляющим входом регистра сдвига, выходы которого подключены к соответствующим управляющим входам управляемого делителя час» тоты, счетчик импульсов, установочные входы которого являются шинами кода постоянного числа, вход разрешения записи объединен с входами установки нуля делителя частоты и управляемого делителя частоты, входом установки единицы регистра сдвига и является выходной шиной, а выходы соответственно соединены с первыми входами блока сравнения кодов, выход которого является выходной шиной, и первый элемент задержки, о т л и— ч а ю шийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей преобразователя эа счет обеспечения дополнительной функции модуляции выходной частоты, в него введены триггер, второй элемент задержки, ключ, сумматор, первое и второе зало минающие устройства, счетчик адреса

F пакс

Ъ с с

Яих

Составитель В.Войтов

Редактор A.Козориз Техред Л.Сердюкова Корректор В.Синицкая

Заказ 4631/57 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5 12 и регистр хранения, первые выходы которого соединены с соответствующими входами первого запоминающего устройства, вторые выходы — с соответствующими первыми входами второго запоминающего устройства, установочные входы являются шинами кода адреса задаваемой частоты, а вход разрешения записи объединен с входом установки нуля счетчика адреса и входом второго элемента задержки и подключен к выходу ключа, первый вход которого подключен к выходу триггера, первый вход которого является шиной управления, а второй вход подключен к выходу второго элемента задержки, при этом второй вход

52943 Ь ключа объединен с входом первого элемента задержки и является выходной шиной, причем выход управляемого делителя частоты соединен с вычитающим входом счетчика импульсов, а выход первого элемента задержки: подключен к счетному входу счетчика адреса, выходы которого подключены к соответствующим вторым входам вто1О рого запоминающего устройства, выходы которого подключены к соответствующим первым входам сумматора, вторые входы которого соединены с соответствующими выходами первого

15 запоминающего устройства, а выходыс соответствующими вторыми входами блока сравнения кодов.