Устройство для приема сигналов с комбинированной фазочастотной манипуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - повышение помехоустойчивости. Устройство содержит частотный детектор 1, блок 2 подстройки фазы (БПФ), генераторы 5 и 6 опорных сигналов, фазовый детектор (ФД) 8. Цель достигается введением двух коммутаторов (К) 4 и 7 и линии задержки. К 4 содержит два элемента И, элемент НЕ. К 7 содержит два элемента И, элемент НЕ и элемент ИЛИ. По п.2 БПФ 3 содержит два фазовых детектора, фазовращатель на 90° и перемножитель. Назначение К 7 состоит в том, чтобы на 1-м опорном входе ФД 8 и 1-м входе БПФ 3 был опорный сигнал, настота которого совпадает с частотой сигнала , поступающего на 1-й сигнальный вход ФД 8 и 1-й вход БПФ 3, К 4 предназначен для того, чтобы генераторы 5 и 6 управлялись своим управлякицим сигналом. В БПФ 3 осуществляются снятие фазовой, манипуляции и вьфаботка сигнала рассогласования. Использование кольца фазовой АПЧ в канале обработки фазы повышает помехоустойчивость устройства особенно при приеме сигналов с доплеровским (СДВИГОМ частоты, 1 8,п. ф-лы, 5 ил. с 5В (Л I Фиг .1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (su 4 Н 04 L 27/22

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA

ОПИСАНИЕ ИЗОБРЕТЕНИЯ И

616.: " а

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ и 7 и линии задержки. K 4 содержит два элемента И, элемент НЕ. К 7 содержит два элемента И, элемент НЕ и . элемент ИЛИ. По п.2 БПФ 3 содержит два фазовых детектора фазовращао

Э тель на 90 и перемножитель. Назначение К 7 состоит в том, чтобы на

1-и опорном входе ФД 8 и 1-м входе БПФ 3 был опорный сигнал, частота которого совпадает с частотой сигнала, поступающего на 1-й сигнальный вход ФД 8 и 1-й вход БПФ 3, К 4 предназначен для того, чтобы .генераторы 5 и 6 управлялись своим управляющим сигналом. В БПФ 3 осуществляются снятие фазовой,манипуляции и выработка сигнала рассогласования.

Использование кольца фазовой АПЧ в канале обработки фазы повышает помехоустойчивость устройства особенно при приеме сигналов с доплеровским сдвигом частоты. 1 з.п. ф-лы, 5 ил. (21) 3871339/24-09 (22) 25.03.85 (46) 23.08.86. Бюл. Р 31 (72) Я.Т.Абдалов, С.Д.Хайсюра н Н.В.Хорькова (53) 621.386.6 (088.8) (56) Авторское свидетельство СССР

11 - 809643, кл. Н 04 L 27/22, 1979.

Авторское свидетельство СССР

Ф 780218, кл. Н 04 L 27/22, 1978. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ

С КОМБИНИРОВАННОЙ ФАЗОЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ (57) Изобретение относится к электросвязи. Цель изобретения — повышение помехоустойчивости. Устройство содержит частотный детектор 1, блок

2 подстройки фазы (БПФ), генераторы 5 и 6 опорных сигналов, фазовый детектор (ФД) 8. Цель достигается введением двух коммутаторов (К) 4

„„SU„„12529 7 A 1

1252967

Изобретение относится к электросвязи и может быть использовано для приема сигналов с комбинированной фазочастотной манипуляцией.

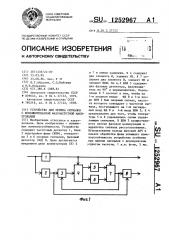

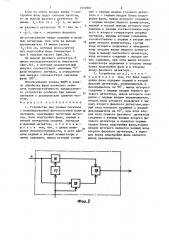

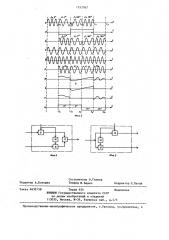

Цель изобретения — повышение помехоустойчивости. . На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 — структурная электрическая схема блока подстройки фазы; на фиг. 3 — временные диаграммы; на фиг. 4 †. структурная электрическая схема второго коммутатора; на фиг. 5 — структурная электрическая схема первого коммутатора.

Устройство для приема сигналов с комбинированной фазочастотной манипуляцией содержит частотный детектор 1, линию 2 задержки, блок 3 подстройки фазы, первый коммутатор 4, первый 5 и второй 6 генераторы опорных сигналов, второй коммутатор 7 и фазовый детектор 8.

Второй коммутатор ? содержит первый элемент И 9, элемент НЕ 10, элемент ИЛИ 11 второй элемент И 12.Первый коммутатор 4 содержит первый элемент И 13, элемент НЕ 14, второй элемент И 15. Блок 3 подстройки фазы содержит первый фазовый детектор 16, о фазовращатель 17 на 90, второй фазовый детектор 18, перемножитель 19.

Устройство работает следующим образом.

Пусть на вход устройства поступает сигнал с фазочастотной манипуляцией (фиг.За). При этом в моменты

t — t частотным детектором 1 прини1 5 мается решение о частоте входного сигнала. На выходе частотного детектора 1 будет последовательность импульсов (фиг.Зб), в которой отрицательный импульс соответствует значению частоты f, а положительный— значению частоты f . Эта последовательность импульсов поступает на управляющие sxo > коммутаторов 4 и 7.

На выходе линии 2 задержки имеем сигнал (фиг.Зв), задержанный относительно входного сигнала на время обработки частоты. Генераторы 5 и 6 опорных сигналов вырабатывают опорные сигналы частот (фиг.Зг,д). Назначение второго коммутатора 7 состоит в том> чтобы на первом опорном входе фазового детектора 8 и первом входе блока 3 подстройки фазы был опорный сигнал (фиг.3e), частота которого

50 ляющий. сигнал проходит на управляющий выход первого коммутатора 4 (фиг.Зз). Тем самым осуществляется подстройка первого генератора 5 опорных сигналов.

При поступлении на вход коммутатора 4 отрицательного импульса управляющий сигнал проходит на вход второго генератора 6 опорных сигналов (фиг. Зи) . Тем самым .каждый генератор 5 и 6 опорных сигналов подстраивается только тогда, когда на входах блока 3 подстройки фазы имеется сигнал частоты, совпадающей с частотой данного генератора 5 или б опорных сигналов. В блоке 3 подстройки фазы осуществляется снятие фазовой манипуляции и выработка сигнала рассогласования. совпадает с частотой сигнала, поступающего на первый сигнальный вход фазового детектора 8 и первый вход блока 3 подстройки фазы.

Коммутатор 7 работает следующим образом.

При поступлении на третий управляющий вход коммутатора 7 и, следовательно, на управляющий вход элемента И 9 положительного импульса (соответствующий частоте f ) сигE нальный вход элемента И 9 открывается и на выход коммутатора 7 проходит через элемент ИЛИ ll опорный сигнал частоты f,. В этот момент на выходе элемента И )2 сигнал отсутствует.

На его выходе сигнал появляется не только тогда, когда на управляющем входе комкутатора 7 будет отрицатель 0 ный импульс (соответствующий частоте и ).

На выходе блока 3 подстройки фазы будет сигнал, соответствующий рассогласованию между фазами входного н опорного сигналов, при этом в период времени 4 2 и 4 з бу дет сигнал рассогласовайия между опорным и сигналами частоты Й, в периоды t,--t,, . -tt — сигнал рассогласования между опорным и входным сигналами частоты. Для того,чтобы генераторы 5 и 6 опорных сигналов управлялись своим управляющим сигналом, используется коммутатор 4.

35 При поступлении на управляющий вход коммутатора 4 положительного импульса с выхода частотного детектора I элемент И 13 открывается, элемент И 15 закрывается, а управЗ 12529

Если на обоих входах блока 3 подстройки фазы будут сигналы частоты, то на выходе фазового детектора 16 имеем Sin (0 + ) на Выхо

5 де фазового детектора 18 V Cos (са +

И

+ — -) где сс — величина фазового

2 рассогласования между опорным и входным сигналами. При этом на выходе перемножителя 19 имеем сигнал

V Sin 2s который испо,ьзуется

t для подстройки фазы генератора 5 или 6 опорных частот (фиг.Зж).

На выходе фазового детектора 8 имеем последовательность импульсов (фиг.Зк), в которой положительный и импульс соответствует значению 0 фазы входного сигнала, а отрицательный импульс соответствует значению фазы 180

Использование кольца ФАПЧ в канале обработки фазы позволяет повысить помехоустойчивость предлагаемого устройства особенно при приеме сигналов с доплеровским сдвигом частотыы.

Формула из обре тения

1. Устройство для приема сигналов с комбинированной фазочастотной мани-ЗО пуляцией, содержащее частотный детектор, блок подстройки фазы, первый и второй генераторы опорных сигналов и фазовый детектор, о т л и ч а ю— щ е е с я тем, что, с целью повы- 35 шения помехоустойчивости, в него введены первый и второй коммутаторы и линия задержки, выход которой соеди67 4 нен с первым входом ÿsoâoão детектора и с первым входом блока подстройки фазы, выход которого соединен с первым входом первого коммутатора, первый и второй выходы которого подключены к входам соответственно первого и второго генераторов опорных сигналов, выходы которых соединены соответственно с первым и вторым входами второго коммутатора, третий вход которого подключен к объединенному второму входу первого коммутатора и выходу частотного детектора, вход которого соединен с входом линии задержки, при этом выход второго коммутатора подключен к второму входу блока подстройки фазы и к второму входу фазового детектора.

2. Устройство по п.l о т л и— ч а ю щ е е с я тем, что блок подстройки фазы содержит первый и второй фазовые детекторы, перемножитель и о фазовращатель на 90, выход которого соединен с первым входом первого фазового детектора, выход которого соединен с первым входом перемножителя, второй вход которого подключен к выходу второго фазового детектора,первый вход которого соединен с входом о фазовращателя на 90, при этом второй вход первого фазового детектора соединен с вторым входом второго фазового детектора и является первым входом блока подстройки фазы, вторым входом которого является первый вход второго фазового детектора, а выходом блока подстройки фазы является выход перемножителя.

Фиг.2

1252967

y, )ao i. 8 1

I !

yt na / ° 0

1 с (g

tJl

Фиа 3.Фик5

Составитель О.Геллер

Техред И.Верес

Редактор А.Козориз

Корректор Л.Патай

Заказ 4632/58

Тираж 624

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4