Устройство для контроля параметров

Иллюстрации

Показать всеРеферат

Изобретение относится к области контрольно-измерительной техники и может быть использовано при построении систем автоматизированного контроля многопараметрических объектов и позволяет повысить быстродействие устройства. Устройство для контроля параметров содержит преобразователи t, входы которых подключены к выходам объекта 3 контроля, управляющие входы - к первым выходам блока 4 программирования, а выходы соединены с входами коммутатора 5, выход которого подключен к первым входам первого и второго блоков 6 и 7 вычитания, выходы которых соединены с первыми входами первого и второго .компараторов 8 и 9, вторые входы которых соединены с выходом третьего источника 10 опорного напряжения , вход которого подключен к с (Л С фиг.)

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

PECllYBStHX (51) 4 С 05 В 23/02

«Д ъ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ \

ГОСУДАРСТВЕННЫЙ XOMHTET СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬ1ТИЙ (21) 3844288/24-24 (22) 16. 01.85 (46) 30,08.86. Бюл. Р 32 (71) Киевский ордена Ленина политехнический институт им. 50-летия

Великой Октябрьской социалистической революции (72) Е.Т. Володарский, В.Ф. Нестеренко и В.И, Беда (53) 62 1.396(088.8) (56) Авторское свидетельство СССР

У 418833 кл. G 05 В 23/02, 1970.

Авторское свидетельство СССР

9 996600774433, кл. G 05 В 23/02, 1980. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ (57) Изобретение относится к области контрольно-измерительной техники

„„SU„„1254441 A 1 и может быть использовано при построении систем автоматизированного контроля многопараметрических объектов и позволяет повысить быстродействие устройства. Устройство для контроля параметров содержит преобразователи 1, входы которых подключены к выходам объекта 3 контроля, управляющие входы — к первым выходам блока 4 программирования, а выходы соединены с входами коммутатора 5, выход которого подключен к первым входам первого и второго блоков 6 и 7 вычитания, выходы которых соединены с первыми входами первого и второго .компараторов 8 и 9, вторые входы которых соединены с выходом третьего источника 10 опорного напряжения, вход которого подключен к

1254441 второму выходу блока 4 программирования, третий и четвертый выходы ко-, торого соединены с входами второго и первого источников 11 и 12 опорного напряжения, выходы которых соединены с вторыми выходами первого и второго блоков 6 и 7 вычитания, вычислитель 13, выход которого соединен с входом счетчика 14, а управляющий вход подключен к пятому выходу блока 4 программирования, а также дополнительно введенные оперативное запоминающее устройство 15, компаратор 16 кодов и блок 17 обработки и регистрации информации, первый выход которого соединен с входом блока 4 программирования, второй выход которого соединен с управляющим входом счетчика !4, первые входы подключены к первым выходам блока 4 программирования, второй и третий входы подключены к выходам соответственно первого и второго ком1

Изобретение относится к контрольно-измерительной технике и может быть использовано при построении систем автоматизированного контроля многопараметрических объектов. 5

Цель изобретения — повьппение быстродействия устройства.

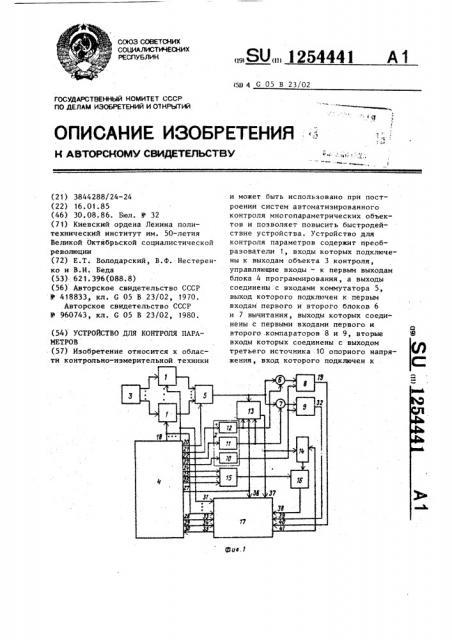

На фиг. 1 приведена структурная схема предлагаемого устройства для контроля параметров, на фиг. 2 — 1О структурная схема блока программирования; на фиг. 3 - структурная схема компаратора; на фиг. 4 — структурная схема вычислителя; на фиг. 5 — структурная схема блока обработки и ре- !5 гистрации информации; на фиг. 6— временные диаграммы работы устройства для контроля параметров.

Устройство для контроля параметров (фиг. 1) содержит преобразова- 20 тель 1, блок 2 опорных сигналов, объект 3 контроля, блок 4 программирования, коммутатор 5, первый 6 и второй 7 блоки вычитания, первый

8 и второй 9 компараторы, третий 1О, второй 11 и первый 12 источники опорного напряжения, вычислитель 13, параторов 8 и 9, четвертый, пятый и шестой входы соединены соответственно с пятым, шестым и седьмым выходами блока 4 программирования, седьмой вход соединен с выходом вычислителя 13, а восьмой вход соединен с выходом компаратора 16 кодов, подключенного первым входом к выходу счетчика 14, а вторым входом— к выходу оперативного запоминающего устройства 15, первый, второй и третий входы которого соединены соответственно с восьмым, девятым и десятым выходами блока 4 программирования, одиннадцатый выход которого соединен с управляющим входом коммутатора 5, выход которого подключен к первому входу вычислителя

13, второй и третий входы которого подключены соответственно к выходам второго и первого источников

11 и 12 опорного напряжения. 2 з.п. ф-лы. 6 ил.

2 счетчик 14, оперативное запоминающее устройство (ОЗУ) !5, компаратор

16 кодов, блок 17 обработки и регистрации информации, первые управляющие выходы 18 блока 4, выход 19 первого компаратора 8, шестой 20, четвертый 21, третий 22, второй 23, первый 24 и пятый 25 информационные выходы блока 4, второй 26, пятый 27, третий 28 и четвертый 29 управляющие выходы блока 4, вход 30 блока 4, первые входы 31 блока 17, выход 32 второго компаратора 9, второй 33 и третий 34 входы блока 17, выход 35 блока 17, четвертый 36, пятый 37, шестой 38, седьмой 39 и восьмой 40 входы блока 17 и второй выход 41 блока !7.

Блок 4 программирования (фиг. 2) образуют клавишный регистр 42, элемент 43 памяти управляющего кода первого источника 12 опорного напряжения, элемент 44 памяти управляющего кода второго источника 11 опорного напряжения, элемент 45 памяти управляющего кода третьего источника 10 опорного напряжения, буферный

1254441 регистр 46, счетчик 47 первую 48 и вторую 49 группы элементов ИЛИ, инверторы 50 и 51, элементы И 52 и 53,.генератор 54 тактовых импульсов, триггер 55, счетчик 56, триггер 5

57, дешифратор 58 и группу 59 инверторов.

Первый 8 и второй 9 компараторы (фиг. 3) выполнены аналогично и состоят из элементов 60 и 61 сравне1О ния, аналогового инвертора 62 и элемента ИЛИ 63.

Вычислитель 13 (фиг. 4) содержит элементы 64 и 65 сравнения и элементы И 66 и 67. 15

Блок 17 (фиг. 5) состоит иэ элемента И. 68, инвертора 69, элементов

И 70 и 71, элементов ИЛИ 72 и 73, элементов И 74 и 75, элемента ИЛИ-НЕ

76, элемента И-HE 77, элементов

И 78 и 79, триггеров 80 и 81, элемен-. тов И 82 и 83, триггеров 84 и 85, индикаторной панели 86, первой 87 и второй 88 групп элементов И и первой 89 и второй 90 групп триггеров.

Преобразователи преобразуют параметры объекта контроля (например, амплитудное, среднее и действующее значения переменного напряжения, частота, разность фаз, параметры 30 двухполюсных электрических цепей и т.п.) в постоянное напряжение. Коммутатор 5 обеспечивает подключение соответствующего 1-го входного канала к выходу, причем номер конт- 3S ролируемого входного канала определяется значением кода на управляющем входе коммутатора 5. Клавишный регистр 42 может быть выполнен в виде панели с клавишами для набора 4О кодов информации. При нажатии клавиши осуществляется подключение напряжения, соответствующего уровню

"0" и " 1" на соответствующие выходы клавишного регистра 42. 45

Устройство работает следующим образом.

Программа контроля состоит из нескольких кадров, в каждом из которых осуществляется контроль очередного Sp параметра Х объекта 3 контроля.

Объект 3 контроля признается годиьм по данному параметру, если последний лежит в пределах нижнего Х „ и верхнего X допустимых значений, т.е. у

8 если выполняется условие Х„сХ Х„.

В противном случае объект 3 контроля признается негодным.

При переходе на очередной кадр программы контроля под воздействием сигналов блока 4 программирования, передаваемых по цепям управления на управляющие входы преобразователей 1 и коммутатора 5, очередной параметр Х преобразуется в соответствующем преобразователе 1 в сигнал У в виде постоянного напряжения, который через коммутатор 5 поступает на вход вычислителя 13 и первые входы блоков 6 и 7 вычитания.

На другие входы блоков 6 и 7 вычитания и вычислителя 13 поступают опэрные напряжения У и Y, сфор1 мированные в источниках 12 и 11 опорного напряжения под воздействием управляющих сигналов с блока 4 программирования и соответственно равные верхнему )(и нижнему Х„ допустимым значейиям контролируемого параметра в очередном кадре программы. Третий источник 10 опорного напряжения формирует опорное напряжение У, величина которого равна граничному значению 6 погрешносе ти Ь соответствующего преобразова-. теля. Напряжение поступает на вторые входы компараторов 8 и 9. Компараторы 8 и 9 формируют на выходе сигнал " 1", если разности преобразованного параметра у и соответственно опорных сигналов Y и У равных верхнему Х и нижнему Х„ допустимым значенйямконтролируемого параметра Х, поступающих на первые входы компараторов 8 и 9, по модулю превышают значение опорного напряжения ., равного граничному з

O значению л погрешности 6 соответствующего преобразователя 1, поступающего на вторые входы компараторов, т.е. если I У- У, t Y или (Х ь — X,(>а, выходной сигнал компаратора 8 равен "1", в противном случае — "0"; если

Y или fX - X-х„ а, выходной сигнал компаратора 9 равен

"1", в противном случае — "0". Результаты сравнения с выходов компараторов 8 и 9 поступают s блок 17.

На выходе вычислителя 13 появляется сигнал "1", если объект 3 контроля признан годным по данному параметру Х, т.е. если 9 <7 с Y или Х„(Х < X . В случае признания объекта 3 контроля негодным по параметру Х, т.е. если У<У

1254441 или У >У„, или Х (X„илн Х >Х на ь э выходе вычислителя 13 появляется сигнал "0".

В зависимости от соотношения сигналов 7, У„, У,, У поступающих соответственно от преобразователей

1 и источников 12, 11 и 10 опорного напряжения устройство работает в двух режимах: режиме достоверного анализа и критическом режиме.

Если разность преобразованного сигнала У и соответствующего опорного сигнала У или У по модулю

1 2 больше опорного сигнала У, т. е. если 1Х + 4 - Хь > и)X + h-X „I >b1,. то устройство работает в режиме достоверного анализа. При этом на выходах компаратора 8 или 9 появляется сигнал "1", поступающий на входы 49 и 39 блока 17.

Под действием "1" с выходов компараторов 8 и 9 блок 17 анализирует сигнал на входе 37, поступающий с выхода вычислителя 13, и если он равен " 1", т.е. когда вычислитель

13 признает объект 3 контроля годным по данному параметру (т. е. > „ Х с Х 8 ) и при этом выполняются неравенства

IX +0 - Х > а и 1Х+ - XÄ(+A, фиксируемые блоками б и 7 вычитания и компараторами 8 и 9, то объект 3 контроля признается годным по данному параметру. Если сигнал на выходе вычислителя 13 равен "0", т.е. если

Х (Х „ или Х >Х, то объект контроля 3 признается негодным по данному периметру.

Если разчость,преобразованного сигнала У и соответственно опорного сигнала У, или сигнала У по модулю меньше опорного сигнала Чз т.е. еслн 1Х +й - Х 1(ht или

1Х +6 — Х„1(д -, то устройство работает в критическом режиме, т.е. информация о годности объекта 3 контроля (уровень "0" или "1"), формируемая на выходе вычислителя 13, не является достоверной, из-за чего появляется необходимость проведения внутри данного кадра программы не-! скольких контрольно-измерительных тактов. В данном режиме логический сигнал иа выходе одного из компараторов 8 или 9 равен "0".

В каждом контрольно-измерительном такте, включая и первый, в случае признания вычислителем 13 годности объекта 3 контроля код на вы5

3.5

Ь ходе счетчика 14, соединенного входом с выходом вычислителя 13, увеличивается на 1. Данный код с выхода счетчика 14 поступает на первый вхоД компаратора 16 кодов, в котором в каждом такте кадра программы сравнивается с кодом, поступающим с выхода ОЗУ 15 на второй вход компаратора 16 кодов. В каждом контрольно-измерительном такте на выходе 03У 15 появляется записанный ранее код числа результатов "Годен" (формируемого вычислителем 13 и подсчитываемого счетчиком 14), необходимого для признания объекта 3 контроля годным но данному параметру Х при проведении данного числа контрольно-измерительных тактов. Таким образом, если по окончании очередного контрольно-измерительного такта коды на входах комнаратора 16 кодов равны, логический сигнал на выходе последнего равен "1" и поступает на вход

38 блока 17, в результате чего объект 3 контроля признается годным.

Если при проведении очередного контрольно-измерительного такта на выходах компараторов 8 и 9 появляется сигнал " 1" т.е. в данном такте о выполняется условие (X + ь — Х 1 > Ьг и tX +3, — X „,I) h" то устройство переходит из критического режима s. достоверный и блок 17 принимает суждение о годности объекта 3 контроля по сигналу на выходе вычислителя 13, как было описано выше, и осуществляется переход на следующий кадр программы.

Если же в течение времени, отведенного на проведение назначенного числа контрольных тактов, устройство не переходит из критического режима в достоверный и на выходе компаратора 16 кодов не появляется "1", т.е. решение "Годен" не может быть принято с заданной достоверностью, то на входе 33 блока 17 появляется сигнал " 1", поступающий с выхода 29 блока 4 программирования, в результате чего блок 17 принимает решение

"Негоден".

По окончании каждого кадра программы (при этом блок 17 при щл суждение о годности объекта контроля 3 по данному параметру) на выходе блока 17 появляется сигнал "1", который поступает на вход 30 блока 4 программирования, в результате чего

1254441 последний осуществляет переход на новый кадр программы контроля.

До начала контроля все клавиши клавишного регистра 42 блока 4 программирования находятся в отжатом состоянии, обеспечивая подключение второго, шестого, седьмого, восьмого, девятого выходов клавишного регистра

42 к напряжению, соответствующему уровню "8, а всех остальных выходов — к напряжению, соответствующему уровню " 1". При этом в "О" установлены буферный регистр 46 "0" с восьмого выхода клавишного регистра 42, счетчики 47 и 56 — " 1" с выхода инвертора 50, триггеры 55 и 57 — "0" с выхода элемента H 53, дешифратор

58 — " 1" с выхода инвертора 51, триггеры 80, 81, 84 и 85 блока 17 — "0" с выхода 29 блока 24 программирования. На выходах 35 и 4 1 блока 17 присутствуют сигналы " 1". Счетчик

14 установлен в "0" сигналом " 1" с выхода 41 блока 17.

До начала первого кадра программы контроля (до нажатия кнопки "Запуск") устройство работает в режиме записи информации. В элементы 43-45 памяти записываются коды опорчых напряжений источников 12, 11 и 10 опорных напряжениИ для каждого кадра программы контроля, т.е. для каждого контролируемого параметра.

Причем в каждую ячейку элементов

43-45 памяти заносятся коды для соот- 35 ветствующих кадров программы. Коды адресов ячеек нажатием соответствующих клавиш клавишного регистра 42 устанавливаются на шестом выходе клавишного регистра 42 и через груп- 40 пу 48 элементов ИЛИ (на втором входе группы 48 элементов ИЛИ установлен код "0" с выхода счетчика 47) поступают на адресные входы элементов 43-45 памяти. В буферный регистр 45

46 записывается код и числа контрольно-измерительных тактов, проводимых при контроле каждого параметра в критическом режиме. В счетчик

47 записывается код М числа контро- 50 лируемых параметров объекта 3 контроля. Требуемые коды поступают на информационные входы элементов

43-45 памяти, буферного регистра 46, счетчика. 47 со второго выхода кла- 55 вишного регистра 42, в котором набираются нажатием соответствующих клавиш. В ОЗУ 15 записываются коды и, числа результатов "Годен", 1 необходимых для признания с заданной достоверностью годным объекта 3 контроля для каждого числа 1 (2,...,h ) контрольно-измерительных тактов. Причем для малых значений, при которых объект 3 контроля не может быть признан годным с заданной достоверностью, при работе в критическом режиме 1 выбирается большим, чтобы не произошло формирование ложного результата "Годен". Требуемый код поступает с выхода 24 блока 4 программирования на информационный вход ОЗУ 15. Код адреса ячейки (т.е. числа 1 ) поступает с выхода 25 блока 4 программирования на адресный вход ОЗУ 15. Выбор блока, в который требуется записать код, сформированный на втором выходе клавишного регистра 42, осуществляется нажатием соответствующих клавиш клавишного регистра 42. При этом при записи информации в элементы 43-45 памяти, ОЗУ 15 и счетчик 47 сигнал "О" появляется соответственно на первом, третьем, четвертом, патом, десятом выходах клавишного регистра 42. При записи информации в буферный регистр

46 на седьмом выходе клавишного регистра 42 появляется " 1". Причем перед записью информации в буферный регистр 46 и счетчик 47 нажатием соответствующеи клавиши -осуществляется их вывод из режима установки в "0" (" 1" появляется на восьмом выходе клавишного регистра 42). После записи информации клавиша адреса соответствующего блока или узла возвращается в исходное состояние.

До нажатия кнопки "Запуск" (по окончании режима записи информации) на выходе счетчика 47 установлен код N, в результате чего устройство подготовлено для проведения первого кадра программы контроля. Это означает, что на вых дах источников

12, 11 и 10 опорного напряжения установлены опорные напряжения, необходюкые при контроле первого параметра, дешифратор 58 блока 4 программирования осуществил выдачу управляющего сигнала на соответствующий преобразователь 1, осуществляющий преобразование первого параметра объекта 3 контроля, а блоки 6 и 7 вычитания и компараторы 8 и 9 определили режим работы устройства

1254441

20

35 по первому параметру (режим достоверного анализа или критический).

При нажатии кнопки "-Запуск" (момент времени t, ) сигнал "1" с девятого выхода клавишного регистра

42 разрешает прохождение тактовых импульсов с выхода генератора 54 тактовых импульсов через элемент

И 53.

С появлением первого тактового импульса на выходе элемента И 53 начинается первый кадр программы (момент времени t ). Тактовый импульс уменьшает состояние счетчика 56 на единицу (счетчик 56, как и счетчик

47, работает в режиме вычитания) и сбробирует блок 17, т.е. разрешает формирование суждения о годности объекта контроля. Если устройство работает в достоверном режиме, то сигнал " 1" на выходе элемента И 68 блока 17 открывает элементы И 70 и 71, разрешая прохождение " 1" через элемент И 70 или 71 в зависимости от сигнала на выходе вычислителя 13.

Если вычислитель 13 признал объект

3 контроля годным, то " 1" появляется на выходе элемента И 70 и на выходе элемента И 74, на второй вход которого пришел тактовый импульс (момент времени 1 ). При этом "1" появляется на выходе элемента И 78 или 79 в зависимости от контролируемого параметра (вторые входы соедииены с соответствующими выходами инвертора 59 блока 4 программирования), в результате чего срабатывает соответствующий триггер 80 или 81 и на индикаторной панели 86 индицируется результат "Годен" по соответ- 40 ствующему параметру. В случае признания вычислителем 13 объекта 3 контроля негодным сигнал "1" появляется на выходе элемента И 71 и на выходе элемента И 75 (момент времени t„ ). При этом. срабатывает триггер 82 или 83 (в зависимости от контролируемого параметра) и на индикаторной панели 86 индицируется результат "Негоден" по соответству- 50 ющему параметру.

Каждый кадр программы контроля заканчивается, если состояние объекта 3 контроля по данному параметру определено (" Годен" .или "Негоден" ).. 55

При этом на выходах 35 и 41 блока

17 появляются сигналы "0" и " 1" соответственно. В результате этого счетчик 14 возвращается в исходное состояние, а на выходе счетчика 56 устанавливается код числа контрольно-измерительных тактов, переписанный из буферного регистра 46, что необходимо для проведения .следующего кадра программы.

По окончании тактового импульса на выходе 35 блока 17 происходит скачок логического уровня из "0 1 в " 1", в результате чего код на выходе счетчика 47 уменьшается на единицу, т.е. осуществляется подключение следующего канала объекта контроля 3 и начинается следующий кадр программы контроля (например, моменты времени г и 15 ). до прихода нового тактового импульса на выходе соответствующего преобразователя 1 устанавливается значение, т.е. соответствующий канал годен для принятия решения о годности объекта контроля.

Если в первом контрольно-измерительном такте очередного кадра программы на выходе элемента И 68 нрисутствует "О" при наличии."О" на выходе одного из компараторов 8 или 9, то устройство работает в критическом режиме, В этом случае, как было сказано выше, проводятся еще несколько тактов. Каждый новый контрольно-измерительный такт начинается с появлением очередного тактового импульса на выходе элемента

И 53 блока 4 программирования. При этом код на выходе счетчика 56, отсчитывающего число проведенных контрольно-измерительных .тактов в каждом кадре программы, уменьшается на единицу (счетчик 56 работает в режиме вычитания).

Если в очередном контрольно-измерительном такте при работе в критическом режиме вычислитель 13 признает объект 3 контроля годным, то код на выходе счетчика 14, подсчитывающего число результатов "Годен", формируемых вычислителем 13, увеличивается на единицу.

Если в очередном контрольно-измерительном такте при работе в критическом режиме срабатывает компаратор 16 кодов, что имеет место при равенстве кодов счетчика 14 и ОЗУ 15, принимается решение "Годен" (момент времени „ ).

1254441

Если при работе устройства в критическом режиме заканчивается назначенное количество контрольно-измерительных тактов, на выходе переноса счетчика 56 появляется сигнал "0" s (момент 1, ), при возвращении которого в состояние " 1" (момент f.g ) срабатывает триггер 57 и с выхода

28 блока 4 программирования на вход

33 блока 17 поступает сигнал "1", в результате чего блок 17 принимает решение "Негоден".

После проведения последнего кадра программы (т.е. когда объект 3 контроля проконтроливан по всем параметрам) на выходе переноса счетчика 47 блока 4 программирования появляется сигнал "0", при возвращении которого в прежнее состояние "1" срабатывает триггер 55. "0" с инверсного выхода триггера 55 закрывает элемент И 53, запрещая прохождение через элемент И 53 тактовых импульсов с выхода генератора 54 тактовых импульсов. Возвращение устройства в исходное состояние осуществляется установкой в исходное состояние всех клавиш клавишного регистра 42 блока 4 программирования.

Граничное значение 6 г погрешнос- ЗО ти выбирают с учетом того, чтобы вероятность принятия погрешностью значения, превышающего граничное значение аг было незначительным, т. е.- Р (h Мь) О. Например, если извест- 5 но, что погрешность преобразования распределена по нормальному закону с дисперсией б, то можно принять ьr =38.

Если граничные значения погрешностей неодинаковы для положительных н от- 4р рицательных значений, то за величину

4р следует принять большее,по абсолютной величине граничное значение.

Если значение преобразованного параметра Ч удовлетворяет условию

<Ус У,-у, Н Ó Ч су су -Y или Y„+ Y ау с м любое значение погрешности в пределах не может 50 повлиять на правильность принятия решения о годности объекта 3 контроля по данному параметру и устройство работает в режиме достоверного анализа, при котором годность объекта SS

3 контроля определяется в течение одного контрольно-измерительного такта.

Если значение преобразованного параметра Y удовлетворяет условию

1,-У, (Ч сУ Ч или У,- У,сусУ у„ то решение о годности объекта 3 контроля по контролируемому параметру может быть неверным из-за влияния на результат преобразования У случайной погрешности преобразователя 1. В этом случае устройство работает в критическом режиме, при котором формируется статическое решение о годности объекта 3 контроля с заданной достоверностью по результатам нескольких контрольно-измерительных тактов.

Форм у л а изобретения

1. Устройство для контроля параметров, содержащее преобразователи, коммутатор, вычислитель, два блока вычитания, два компаратора, блок опорныХ сигналов, счетчик и блок программирования, первые управляющие выходы которого соединены с управляющими входами соответствующих преобразователей, входы которых соединены с .соответствующими выходами объекта контроля, выходы - с соответствующими входами коммутатора, выход которого соединен с первыми входами первого и второго блоков вычитания, вторые входы которых соедине" ны соответственно с первым и вторьм выходами блока опорных сигналов, выходы — с первыми входами первого и второго компараторов соответственно, вторые входы которых соединены с третьим выходом блока опорных сигналов, выход вычислителя соединен со счетным входом счетчика, а управляющий вход - с пятым управляющим выходом блока программирования, третий и четвертый информационные выходы которого соединены соответственно с первым и вторым информационныии входами блока опорных сигналов, о т л и ч а ю щ е е с я тем, что, с целью. повышения быстродействия устройства, s него введены оперативное запоминающее устройство, компаратор кодов и блок обработки и регистрации информации,.пятый вход которого соединен с выходом вычислителя, первый вход которого соединен с выходом коммутатора, управляюший вход — с четвертым входом блока обработки и регистрации ин1254441

14 формации, а второй и третий входы— соответственно с первым и вторым выходами блока опорных. сигналов, третий информационный вход которого соединен с вторым информационным вы- 5 ходом блока программирования, шестой информационный выход которого соединен с управляющим входом коммутатора, первые управляющие выходы — с первыми входами блока обработки и регистрации информации, седьмой и восьмой входы которого соединены с выходами первого и второго компараторов соответственно, а второй выход — с управляющим входом 5 счетчика, информационный выход которого соединен с первым информационным входом компаратора кодов, выход которого соединен с шестым входом блока обработки и регистрации 2о информации, второй и третий входы и первый выход которого соединены соответственно с третьим и четвертым управляющими вьгходами и входом блока

25 программирования, первый и пятыи информационные и второй управляющий выходы которого соединены соответственно с информационным, адресным и управляющим входами оперативного запоминающего устройства, выход кото-ЗО рого соединен с вторым информационным входом компаратора кодов.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок программирования содержит клавишный ре- 35 гистр, три элемента памяти, генератор тактовых импульсов, дешифратор, два счетчика, буферный регистр, два триггера, два элемента И, две группы элементов ИЛИ, два инвертора и груп- 40 пу инверторов, выходы которой соединены с первыми управляющиья выходами блока, а входы — с соответствующими разрядами выхода дешифратора, информационный вход которого соеди- 45 нен с информационным выходом первого счетчика, шестым информационным выходом блока и вторым входом первой группы элементов ИЛИ, первьй вход которой соединен с шестым выходом 50 клавишного регистра и первым входом второй группы элементов ИЛИ, выход которой соединен с пятым информаци" онным выходом блока, второй вход " с информационным выходом второго 55 счетчика, управляющий вход которого соединен с выходом первого элемента

И, а выход переноса — с входом установки в " 1" второго триггера, прямой выход которого соединен с третьим управляющим выходом блока, вход установки в "0" со счетным входом вто рого счетчика, пятым управлякнцим выходом блока, выходом второго элемента И и входом установки в "0" первого триггера, вход установки в которого соединен с выходом переноса первого счетчика, инверсный выход — с третьим входом второго элемента И, второй вход которого соединен с выходом. генератора тактовых импульсов, первый вход — с четвертым управляющим выходом блока, девятым выходом клавишного регистра и первым входом первого элемента И, второй вход которого соединен с входом блока и счетным входом первого счетчика, информационный вход которого соединен с информационными входами первого, второго и третьего элементов памяти, первым информационным выходом блока, вторым выходом клавишного регистра и информационным входом буферного регистра, управляющий вход которого соединен с седьмым выходом клавишного регистра, выход— с информационным входом второго счетчика, вход установки в "0" которого соединен с выходом первого инвертора и входом установки в "0" первого счетчика, управляющий вход которого соединен с десятым выходом клавишного регистра, восьмой выход которого соединен с входом установки в

"0" буферного регистра, входом первого инвертора и входом второго инвертора, выход которого соединен с входом установки "0" дешифратора, первый, третий и четвертый выходы клавишного регистра соединены с управляющими входами соответственно первого, второго и третьего элементов памяти, адресные входы которых соединены с выходом первой группы элементов ИЛИ, а выходы — соответственно с четвертым, третьим и вторым информационным выходами блока, второй управляющий выход которого соединен с пятым выходом клавишного регистра.

3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок обработки и регистрации информации содержит пять элементов И, два элемента ИЛИ, инвертор, элемент ИЛИ-НЕ, элемент И-НЕ, две группы элементов

254441

15 1

И, две группы триггеров и индикаторную панель, входы которой соединены с прямыми выходами соответствующих триггеров первой и второй групп, входы установки s ""1" которых соединенЫ с выходами соответствующих элементов И первой и второй групп, а входы установкив "О"-с .вторым входом элемента И-НЕ и третьим входом блока, восьмой и седьмой входы которого соединены соответственно с первым и вторым входами первого элемента И, выход которого соединен с перваки входами второго и третьего элементов И, выходы которых соединены соответственно с вторым входом первого элемента ИЛИ и первым входом второго элемента ИЛИ, первый и второй входы которых соединены соответственно с щестым и вторым входами блока, а выходы - с первыми входами четвертого и пятого элементов И соответственно, вторые входы которых соединены с четвертым входом блока, второй выход которого соединен с вы5 выходом элемента И-НЕ, первый вход которого соединен с первым выходом блока и выходом элемента ИЛИ-НК, первый вход которого соединен с выходом четвертого элемента И и первыми входами элементов И первой группы, вторые входы которых соединены с соответствующими входами первых входов блока и вторычи входами соответствующих элементов И второй груп 5 пы, первые входы которых соединены с вторым входом элемента ИЛИ-HE и выходом пятого элемента И, пятый вход блока соединен с вторым входом второго элемента И и входом инвертора, 20 выход которого соединен с вторым входом третьего элемента И.

1254441

1254441

t7 В У

Составитель В. Копылов

Техред H.Попович

Корректор Е.Сирокман

Редактор Л.Пчелинская

Заказ 4719/51

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ЯВтвйй

М

Ели.53

Юых Т3

Eblх. И

Тираж 836 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауаская наб., д. 4/5