Устройство для прерывания программ

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к устройствам для прерываний программ при сопряжении различных внешних устройств с цифровыми вычислительными машинами. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что, в устройство, содержащее регистр защиты , шифратор, выходной элемент ИЛИ, триггер режима, входной элемент И, N каналов прерьгаания, каждый из которых «i Jitfi .- - е содержит триггер прерывания, триггер управления и четыре элемента И, введен регистр сброса и ряд дополнительных связей. Повышение достоверности обработки прерывания программ достигается соединением второго входа входного элемента И с входом ответа устройства и второго входа триггера режима с управляющим входом устройства , чем обеспечивается изменение алгоритма блокирования поступления в ЦВМ сигналов прерывания в режиме работы с относительными приоритетами и тем самым исключается возникновение сбойных ситуаций. Введение регистра сброса и соединение его входов с выходами вторых элементов И, а выходов с первыми входами триггеров управления каналов прерывания и соответствующее тактирование регистра сброса сигналами ответа и управления позволило сократить количество линий связи с ЦВМ и исключить по одному элементу в каждом канале прерывания. 1 ил. (Л

44 А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

С 11 (19) (11) (51)4 С 06 F 9/46

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОЬ У СВИДЕТЕЛЬСТВУ . Д

1 (21) 3875322/24-24 (22) 26.03.85 (46) 30,08.86. Бюл. 9 32 (72) П.П. Куликов, А.А. Овдиенко, И,Д, Петренко и Л.В. Смирнова (53) 68.1.325(088.8) (56) Авторское свидетельство СССР

Я 645158, кл. G 06 F 9/46, 1976.

Авторское свидетельство СССР

В 924710, кл. G 06. Р 9/46, 1982. (54) УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАМ1 (57) Изобретение относится к вычислительной технике, а именно к устройствам для прерываний программ при сопряжении различных внешних устройств с цифровыми вычислительными машинами. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается тем, что, в устройство, содержащее регистр защиты, шифратор, выходной элемент ИЛИ, триггер режима, входной элемент И, N каналов прерывания, каждый из которых

1 1 .. содержит триггер прерывания, триггер управления и четыре элемента И, введен регистр сброса и ряд дополнительных связей. Повышение достоверности обработки прерывания программ достигается соединением второго входа входного элемента И с входом ответа устройства и второго входа триггера режима с управляющим входом устройст" ва, чем обеспечивается изменение алгоритма блокирования поступления в

ЦВМ сигналов прерывания в режиме работы с относительными приоритетами и тем самым исключается возникновение сбойных ситуаций. Введение регистC ра сброса и соединение его входов с Е выходами вторых элементов И, а выходов с первыми входами триггеров управления каналов прерывания и соответ. ствующее тактирование регистра сброса сигналами ответа и управления поэ- Я волило сократить количество линий связи с ЦВМ и исключить по одному элементу в каждом канале прерывания.

1 ил.

Изобретение относится к вычислительной технике, а именно к устройствам для прерывания программ при сопряжении различных внешних устройств с цифровыми вычислительными машинами.

Цель изобретения — сокращение количества внешних связей и оборудования.

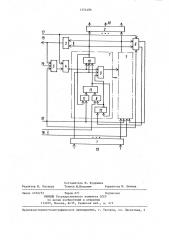

На чертеже приведена функциональная схема устройства для прерывания программ.

Устройство содержит регистр 1 saщиты, шифратор 2, элемент ИЛИ З,триг15

rep 4, элемент И 5, регистр 6 сброса, каналы 7, в каждый из которых входят элементы И 8-11, триггер 12 триггер 13, вход 14 управления режи-мами устройства, группу 15 кодовых

20 входов устройства, ответный вход 16 устройства, сигнальный вход 17 устройства, группу 18 запросных входов устройства, выход 19 прерывания устройства, группу 20 выходов кода адреса прерывания устройства.

Обслуживание внешних запросов с абсолютными приоритетами обеспечивается разрешающим выходным потенциалом триггера 4 режима, который сбрасывается в нулевое состояние при:

30 включении устройства и его установка в единичное состояние блокируется запрещающим потенциалом на входе 14 управления режимами.

В исходном состоянии разрешающим З5 потенциалом с выходов триггеров 12 управления каждого канала разрешен прием внешних запросов, поступающих по группе 18 входов через элемент И 8 и фиксируемых триггерами 13. 4О

Выходным потенциалом с триггеров 13 устанавливаются соответствующие триггеры 12, выходом которых на входах элементов И 8 блокируется прием соответствующего внешнего запроса. Сиг- <> налы с триггеров. 12 и 13 и регистра

1 поступают на входы элементов И 9 и 10, которые выделяют запрос, имеющий высший приоритет, и обеспечивают сквозную передачу сигнала запрета И ! прерывания от высшего уровня приоритета к низшему. Приоритеты запросов уменьшаются слева направо в порядке нумерации каналов 7.

Таким образом, сигнал прерывания 5$ формируется только на выходе элемента И 10, наиболее приоритетного в текущий момент времени канала 7. Этот

1254486 2 сигнал поступает на вход элемента

ИЛИ 3, на вход дешифратора 2, на вход регистра 6 и на первый вход элемента

И 11 соответствующего канала. На выходе элемента ИЛИ 3 формируется сигнал, а на выходе шифратора 2 — команда перехода, которые поступают в ЦВМ.

После приема команды перехода ЦВМ по входу 16 выдает сигнал, управляющий записью значений с выходов элементов

И 10 каждого канала в регистр 6 и устанавливающий в нулевое состояние триггер 13 работающего в текущий момент канала.

Триггеры 12 хранят внешние запросы до полного выполнения и через элемент И 9 запрещают поступление в ЦВМ внешних запросов более низких приоритетов. Триггеры 12 .устанавливаются в нулевое состояние по окончании программы, вызванной внешним запросом, для чего иэ ЦВМ по программе выдается сигнал по входу 17, который, поступая на второй вход регистра с сброса, открывает его выходы и формирует сигнал сброса соответствующего триггера 12. Таким образом, на входе элемента И 8 и.на вхопе элемента И 9 устанавливается разрешающий потенциал, т.е. снимается блокировка запросов низшего уровня приоритетаи .высший из них поступает в ЦВМ.

Режим работы с относительными приоритетами обеспечивается разрешающим потенциалом на входе 14 управления режимами. После включения устройства триггер 4 устанавливается в нулевое состояние и имеет на выходе разрешающий потенциал. В ответ на сигнал прерывания, выдаваемый устройством, ЦВМ по входу 16 формирует сигнал ответа, который совместно с сигналом прерывания и сигналом на входе

14 уетанавливает триггер режима в единичное состояние, чем запрещается поступление в ЦЙМ сигналов прерывания. всех уровней приоритетов. Триггер 4 режима сбрасывается в нулевое состояние по завершении программы прерывания сигналом, поступающим по входу

17. В ЦВМ на выполнение поступает внешний sanpoc.ñ высшим приоритетом среди всех принятых устройством.При этом оно снова блокируется сигналом ответа до завершения обслуживания запроса.

Формула изобретения

Устройство для нрерываиия программ, содержащее регистр защиты, шифратор, з 1254 элемент ИЛИ, триггер, элемент И, каналы, каждый из которых содержит два триггера и четыре элемента И, причем каждый запросный вход устройства подключен к первому входу первого элемента И одноименного канала, в каждом канале выход первого элемента И соединен с единичным входом первого триггера, выход второго элемента И подключен к первому входу третьего !О элемента И, единичный вход второго триггера соединен с выходом первого триггера и с первым входом второго элемента И, второй вход которого соединен с первым входом четвертого эле- 5 мента И, второй вход которого соединен с инверсным выходом второго триггера и вторым входом первого элемента

И., выход третьего элемента И соединен с нулевым входом первого триггера О выход второго элемента И каждого канала соединен с соответствующим входом шифратора и соответствующим входом элемента ИЛИ, второй вход третьего элемента И каждого канала соеди- 5 нен с ответным входом устройства,третий вход второго элемента И каждого канала соединен с одноименньм выходом регистра защиты, входы которого соединены с группой кодовых вхо486 4 дов устройства, третий вход второго элемента И первого канала соединен с выходом триггера, единичный вход которого соединен с выходом элемента И, первый вход которого соединен с выходом элемента ИЛИ и выходом прерывания устройства, второй вход элемента И сс>единен с входом управления режимом устройства, выходы шифратора подключены к группе выходов кода адреса прерывания устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения количества внешних связей и оборудования, в него введен регистр сброса, вход управления записью которого соединен с ответным входом устройства и с третьим входом элемента И, вход управления чтением регистра соединен с нулевым входом триггера и с сигнальным входом устройства,выходы вторык элементов И каналов соединены с входами регистра сброса, а первый вход второго триггера каждого канала соединен с одноименным выходом регистра сброса, третьи входы четвертого элемента И каждого канала, начиная с второго, соединены с выходами четвертого элемента И предццущего канала.

1254486

Составитель М. Кудряшев

Текред И.Попович Корректор М. Демчик

Редактор И. Касарда

Заказ 4722/53 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4