Цифровой измеритель симметричных составляющих

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в системах релейной залщты и автоматики. Цель изобретения - повышение точности и помехоустойчивости измерения. Устройство содержит блок 1 аналого-цифрового преобразования , сумматоры 5 и 18, накапливающий сумматор 14 и квадратор 19. Введение регистров 2,3 и 4, вычитателей 5 и 7, умножителей 8-11, блоков 12 и 13 памяти, накапливакщего сумматора 15 и блоков 16 и 17 возведения в квадрат с образованием новых связей между элементами устройства . позволяет применять дискретное преобразование Фурье с постоянным шагом дискретизации для осуществления селективной фильтрации основной гармоники. Это в свою очередь позволяет полностью ликвидировать влияние гармоник, частоты которых кратны частоте основной гармоники,Кроме того, погрешность, вносимая другими видами помех и шумов, может быть сведена до произвольно малой величины увеличением времени анализа. 7 ил. § (Л сл ел ;о Од

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5ц 4 G Ol R 29/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3869582/24-21 (22) 20.03.85 (46) 07.09.86.Бвл. - 33 . (71) Институт электроники и вычислительной техники АН ЛатвССР (72) И.Я.Билинский, А.П.Кузнецов, А.К.Микелсон, Л.П.Петерсоне, И.А.Федотов и А.Я.Янаус (53) 621.317.799 (088.8) (56) Авторское свидетельство СССР

У 976403, кл. G 01 R 29/16, 1982.

Авторское свидетельство СССР

У 1012158, кл. G 01 R 29/16, 1983. (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЪ СИММЕТРИЧНЫХ СОСТАВЛЯЮЩИХ (57) Изобретение может быть использовано в системах релейной защиты и автоматики. Цель изобретения — повышение точности и помехоустойчивости измерения. Устройство содержит

„„Я0„„1255964 A 1 блок 1 аналого-цифрового преобразования, сумматоры 5 и 18, накапливающий сумматор 14 и квадратор 19. Введение регистров 2,3 и 4, вычитателей 5 и 7, умножителей 8-11 блоков

12 и 13 памяти, накапливающего сумматора 15 и блоков 16 и 17 возведения в квадрат с образованием новых связей между элементами устройства позволяет применять дискретное преобразование Фурье с постоянным шагом дискретизации для осуществления селективной фильтрации основной гармоники. Это в свою очередь позволяет полностью ликвидировать влияние гармоник, частоты которых кратны частоте основной гармоники. Кроме того, погрешность, вносимая другими видами помех и шумов, может быть сведена до произвольно малой величины увеличением времени анализа. 7 ил.

1 12

Изобретение относится к электроиэмерительной технике и может использоваться в системах релейной защиты и автоматики, использующих составляющие прямой и обратной последовательности.

Цель изобретения — повышение точности и помехоустойчивости измерения симметричных составляющих путем применения дискретного преобразования Фурье с постоянным шагом дискретизации для осуществления селективной фильтрации основной гармоники, что позволяет полностью ликвидировать влияние гармоник, частоты которых кратны частоте основной гармоники, а погрешность, вносимая другими видами помех и шумом, может быть сведена до произвольной малой величины увеличением времени анализа.

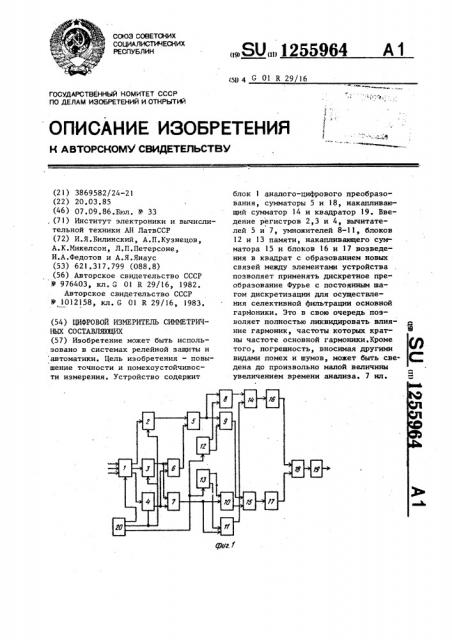

На фиг. 1 изображена функциональная схема измерителя симметричных составляющих; на фиг. 2 — функцио— нальная схема блока аналого-цифрового преобразования (параллельное преобразование); на фиг. 3 — функциональная схема блока управления (параллельное преобразование); на фиг. 4 функциональная схема блока аналого-цифрового преобразования (последовательное преобразование); на фиг. 5 — функциональная схема блока управления (последовательное преобразование); на фиг. 6 — временные диаграммы работы блока управления (последовательное преобразование); на фиг. 7 — функциональная схема квадратора.

Цифровой измеритель симметричнык составляющих содержит блок 1 аналого-цифрового преобразования, входы которого являются входами измерителя. Первый выход блока 1 соединен с входом первого регистра 2, второи выход соединен с входом второго регистра 3, третий выход соединен с входом третьего регистра 4. Выход первого регистра 2 соединен с первым входом первого вычитателя 5, выход второго регистра 3 соединен с первыми входами первого сумматора 6 и второго вычитателя 7, выход третьего регистра

4 соединен с вторыми входами первого сумматора 6 и второго вычитателя

7. Выход первого сумматора б соединен с вторым входом первого вычитателя 5, выход первого вычитателя 5 соединен с первыми входами первого

55964 х

8 и второго 9 умножителя, выход второго вычитателя 7 соединен с первыми входами третьего 10 и четвертого 11 умножителя. Первый выход первого блока 12 памяти соединен с вторым входом первого умножителя 8, второй выход первого блока 12 памяти соединен с вторым входом второго умножителя 9, первый выход второго блока

13 памяти соединен с вторым входом третьего умножителя 10 второй выход второго блока 13 памяти соединен с вторым входом четвертого умножителя 11. Выход первого умножителя 8 соединен с первым входом первого накапливающего сумматора 14, выход второго умножителя 9 соединен с первым входом второго накапливающего сумматора l5 выход третьего умножителя

10 соединен с вторым входом второго накапливающего сумматора 15, выход четвертого умножителя 11 соединен с вторым входом первого накапливающего сумматора 14. Выходы первого 14 и второго 15 накапливающего сумматоров соединены соответственно с входами первого 16 и второго 17 блоков возведения в квадрат, выходы которых соответственно соединены с первым и вторым входом сумматора 18, выход которого соединен с входом квадратора 19. Выход квадратора является выходом измерителя. Первый выход блока 20 управления соединен с управляющим входом блока 1 аналого-цифрового преобразования, второй выход соединен с управляющими входами первого 2, второго 3 и третьего

4 регистра, третий выход блока 20 управления соединен с управляющими входами первого 12 и второго 13 блоков памяти.

Все блоки, кроме блока 1 аналогоцифрового преобразования, квадратора и блока 20 управления, стандартные.

Блок 1 аналого-цифрового преобразования может работать и параллельно.и последовательно. Если преобразование осуществляется параллельно, то блок 1 аналого-цифрового преобразования построен по функциональной схеме (фиг,2) и содержит первый 21, второй 22 и третий 23 аналого-цифровые преобразователи. Преобразование всех трех входных сигналов в цифровую форму осуществляется одновременно по управляющему сигналу от

964 4 помощи счетчика 37 адреса, компаратора 38 кодов и группы 39 элементов И происходит определение адреса памяти, по которому записано соответствующее значение квадратного корня.

Принцип измерения симметричных составлякнцих в предлагаемом измерителе следующий.

Пусть X (t), X (t), Х,(t) — фазные электрические величины, являю- щиеся смесью гармонического сигнала с некоторой помехой, т.е. (3) U!

Функциональная схема квадратора

19 (фиг.7) содержит счетчик 37 адресов, компаратор 38 кодов, группу 39 элементов И и блок 40 памяти. В бло- ке 40 памяти по адресам, которые соответствуют входным величинам, записаны значения квадратного корня.При

3 1255 блока 20 управления, который содержит генератор 24 тактовых импульсов и элемент 25 задержки (фиг.3).

Если преобразование осуществляется последовательно, то функциональ ная схема (фиг.4) блока 1 аналогоцифрового преобразования содержит мультиплексор 26 входа, блок 27 выборки и хранения, аналого-цифровой преобразователь 28 и мультиплексор

29 выхода. По управляющим сигналам от блока 20 управления последовательно в цифровую форму преобразуется первый, второй и третий входной сигналы. r5

В этом случае блок 20 управления построен по функциональной схеме, которая показана на фиг. 5, и содержит генератор 30 прямоугольных импульсов, генератор 31 тактовых импульсов, элемент И 32, счегчик 33, RS-триггер 34, элемент И35 и распределитель 36 импульсов. Генераторы 30 и 31построены по той же схеме, что и генератор 24. Частота генератора 25 прямоугольных импульсов f частота генератора тактовых импульсов f причем f — — . Генератор 31 в теf1

6 чение половины периода колебания 30 открывает элемент И 32 и устанавливает RS-триггер 34 в состоянии "1", таким образом оба элемента И 32 и 35 открыты. Счетчик 33 считает три импульса и перебрасывает в состояние

"0" RS-триггер 34, который закрывает элемент И 35. Таким образом, на первый выход блока 20 управления поступает за один такт работы три импульса частоты f, . В распределителе 36 импульсов (в качестве распределителя импульсов использован дешифратор) эти импульсы соответственно распределяются и потом поступают на второй выход блока 20 управления для пооче- редного стробирования регистров 2,3 и 4.

На третий выход блока 20 управления поступают импульсы с частотой 2 которые синхронизируют работу из 5О мерителя. х4(с) = U A Sin(dt + f„) + SA(t);

Xg(t) 1 ь s>n(>t + 4) + Ss(t)l

X,(t) = U,Áin4Ýt + f,) + S,(tg, (1) где Я, (t), 8 (t), Я,(t) — соответствующие помехй.

Обозначают через Ы (t), U (t) функции, являющиеся электрическими величинами прямой и обратной последовательности соответственно. Любая иэ этих функций является гармоникой с частотой uJ и поэтому может быть записана в виде следующей суммы:

U.(t) = Ы. cosset +р. sin&t, (2) где i = 1,2, а ее эффективное значение U может r быть вычислено по формуле

Следовательно, основной задачей является определение коэффициентов с ., p.. Но коэффициенты <;, p, можно выразить через коэффициенты

Фурье сигналов X„(t), X<(t), Х,(t), соответствующих частоте Л . Если применить такой подход и коэффициенты Фурье сигналов X„(t), Х (t), Х,.(t) заменить их оценками, полученными дискретным преобразованием

Фурье по выборкам дискретных значений где К = 1,2,..., N,N = 21Ггй;

r — целое положительное число;

1/» — частота дискретизации, то получаем выражения, позволяющие по дискретным значениям 1Х (Кь), (Х (К ).1 (X (Ki)f вычислить оцен»» киК,,»». коэдЯициеитов о ;, P.,.

Так для сигналов прямой и обратной последовательности получают

5 1255)

--- ((2X (К7) — Х (КТ )

31 .,1 — Х (KY) )cosdK1.+ (.(-1) 1ГЗ(Х8(К1) с

Х (Кь))з1п + K1)1 и

;Г- (Х,(К )-Х,. К )

ЗЙ К-,) ) з п,Я + ((— )+3(X<(K )Х, (К1) ) созо)Ь.1..1 ° (4)

Определяя по формулам (4) оценки

g., p, по формуле (3) вычисляют оценку эффективного значения l;, при i = 1 прямая последовательность, 15

2 обратная последовательность.

Описанный алгоритм реализуется в цифровом измерителе симметричных составляющих следующим образом.

Сигналы Х (t), Х (.), Х (t) пос- 0 тупают на входы блока 1 аналого-цифрового преобразования и преобразуются в цифровой код Х,(K7), Х (Ki)„

Х (K7.). По управляющим сигйалам от с

25 блока 20 управления, эти сигналы записываются в регистры 2,3 и 4, В сумматоре 6 вычисляется значение Х (К ) + Х,(K;) и переда. е -cя в вычйтатель 5, где определяется значение 2Хд(К1.) — Х (К1.) - Х,(K1.).

В вычитателе 7 вычисляется значение

Х (К ) - Х,(K1) . Умножители 8 и 9 умножают значения 2X<(K ..-. Х (К1)

- Х (K1.) на величину — — соз (.1К i)

1 и — — sin(JK<) которые записаны в

3 и блоке 12 памяти. Умножители 10 и 11 осуществляют умножение Х (K7)

1 40 — Х. (K1) на — - cos (MKY) и с

113

sin (dК1), эти значения записаны в блок 13 памяти. В накапливающем

Д 1 сумматоре !4 определяется опенка а в накапливающем сумматоре 1з — оценка „ . Блоки 16 и 17 возведения в квадрат осуществляют возведение в л 1 квадрат оценок Ы.; и р.,В сумматоре л 1л 1

18 значение . и 8 суммируются. Квад-

1 1 ратор 19 вычисляет квадратный корень из этой суммы.

На выходе измерителя, таким образом, после N тактов работы имеется

5 эффективное значение симметричнои

64 составляющей прямой или обратной последовательности. формула и з о б р е т е н и я

Цифровой измеритель симметричных составляющих, содержащий блок аналого-цифрового преобразования, первый накапливающий сумматор, квадратор и блок управления, о т л и ч а ю щ и йс. я тем, что., с целью повышения точности и помехоустойчивости, в него введены два блока памяти, три регистра, два вычитателя, два сумматора, четыре умножителя, второй накапливающий сумматор, первый и второй блоки возведения в квадрат, причем выходы блока аналого-цифрового преобразования соединены соответственно с первыми входами регистров, выход первого регистра соединен с первым входом первого вычитателя, выход второго регистра соединен с первыми входами первого сумматора и второго вычитателя, вторые входы которых соединены с выходом третьего регистра, выход первого сумматора соединен с вторым входом первого вь1читателя, выходы первого и второго вычитателей соединены соответственно с первыми входами первого, второго и третьего и четвертого умножителей, вторые входы первого и второго и третьего и четвертого умножителей соединены соответственно с первым и вторым входами первого и в" îðîãî блоков памяти, выходы первого и четвертого и второго и третьего умножителей соединены соответственно с первым и вторым входами первого и второго накаплиьающих

;"умматоров, выходы первого и второго накапливающих сумматоров соединены с входами соответственно первого и второго блоков возведения в квадрат, выходы которых соответственно соединены с первым и вторым входами второго сумматора, выход которого соединен с квадратором„ первый выход блока управления соединен с управляющим входом блока аналого-цифрового преобразования, второй выход соединен с утравляющими входами первого, второго и третьего регистров, третий выход соединен с управляющими входами первого и второго блоков памяти.

1255964

puz. Х

Фиг. 5

1255964

Третий

Рыхл

Рмод аерйгй

ЮыюЯ

&юрой

Составитель Н.Михалев

Техред И. Cодaнич

Редактор Н.Данкулич

Корректор А. Обручар

Заказ 4818/45 Тираж 728

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Подписное

Производственно-полиграФическое предприятие, r.Óæãoðoä, ул.Проектная, 4