Устройство для нормализации избыточных кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике. Целью изобретения является расширение функциональных возможностей за счет работы при различных значениях характеристического параметра. Для этого в устройство , содержащее регистр сдвига, четыре триггера, счетчик, дешифратор, генератор импульсов, элементы задержки , ИЛИ, И и запрета, введено два элемента И с соответствующими связями . 1 ил. СП Од

СОЮЗ СсаЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 G 06 F 5 00 т t

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 377-1 719/24 — 24 (22) 18.07.84 (46) 07.09,86. Бюл. ¹- 33 (71) Харьковский ордена Ленина политехнический институт им. В.И, Ленина (72) Н.А.Збродов, В.Г.Воронов и В.Н.Изотов (53) 681.3(088.8) (56) Авторское свидетельство СССР

¹ 1019434, кл. G 06 F 5/00, 1982.

Авторское свидетельство СССР №- 951291, кл. С 06 F 5/00, 1980.

ÄÄSUÄÄ 1256099 А 1 (54) УСТРОЙСТВС ДЛЯ НОРМАЛИЗАЦИИ

ИЗБЫТОЧНЫХ КОДОВ (57) Изобретение относится к цифровой вычислительной технике. Целью изобретения является расширение функциональных возможностей за счет работы при различных значениях характеристического параметра. Для этого в устройство, содержащее регистр сдвига, четыре триггера, счетчик, дешифратор, генератор импульсов, элементы задержки, ИЛИ, И и запрета, введено два элемента И с соответствующими связями. 1 ил.

1256009 ф

Изобретение относится к вычислительной, аналого-цифровой и цифроаналоговой технике и может быть использовано в специализированных отказоустойчивых вычислительных машинах для нормализации избыточных r,1кодов.

Целью изобретения является расширение функциональных возможностей эа счет работы при различных значениях харакТеристического параметра.

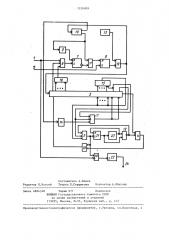

На чертеже приведена схема устройства для нормализации избыточных . кодов.

Устройство для нормализации избыточных кодов содержит вход 1 задания режима, вход 2 пуска, регистр 3 сдвига элементы И 4-6, триггеры 7, 8, элемент 9 задержки, счетчик 10, элементы И 1.1, 12, генератор 13 импульсов, дешифратор 14, элементы И 15 и 16, элементы 17 и 18 запрета, элементы ИЛИ 19 и 20, триггеры 21 и 22, элемент 23 задержки, контрольный выход 24 устройства.

r,1 коды предназначены для построения помехоустойчивых устройств и сквозного контроля информационно-вычислительных систем. Значение характеристического параметра г определяет максимальное количество единиц, находящихся в соседних двоичных разрядах числа и образующих разреШенную группу единиц, группы единиц должны быть разделены не менее, чем одним нулем.

Операция нормализации (r, 1) кодов может рассматриваться, как замена г+1 смежных единиц младших разрядов одной единицей в старшем разряде.

Устройство для нормализации избыточных кодов работает следующим образом.

Опишем работу устройства в режиме нормализации на примере приведения к нормальной форме кода числа А

=163=1011101110. Веса разрядов 2,1 кода будут соответственно 1 1 2 4 7

13 24 44 81 149;

В исходном состоянии все триггеры и счетчик 10 обнуляются. В информационнйе разряды регистра 3 сдвига заносится исходный код. Триггер нулевого разряда регистра сдвига (полагаем, что регистр одиннадцатиразрядный) устанавливается в нулевое состояние. На входе 1 задания режима устанавливается единичный сигнал, что соответствует режиму нормализации.

Устройство запускается в работу по единичному сигналу на входе 2 пуска.

Единичным сигналом с входа 1, сигналом элемента 18 запрета блокируется

5 установка триггера 22 в единичное состояние. Сигналом пуска устанавливается в единичное состояние триггер 8, в результате чего импульсы от генератора 13 импульсов поступают на вход счетч.ка 10 и сдвигают содержимое регистра 3 сдвига.

После первого тактового импульса триггеры п-1-го, ..., и-(г+1)-го разрядов регистра 3 сдвига устанавлива15 ются в единичное состояние.

Единичным сигналом с выходов элементов И 5 и И 15 устанавливается соответственно в нулевое состояние триггеры и-3 †,..., n-(r+1)-го раз20 рядов (в примере r-3-ro) и в единичное состояние — триггер 21. Единичным сигналом с прямого выхода триггера 21 через элемент задержки блокируется запись единицы пер носа через элементы И 4 и ИЛИ 19 в нулевой разряд регистра 3 сдвига в течении двух последующих тактов. В четвертом такте, нуль циклически переписывается с выхода переноса регистра 3 сдвига в ну30 левой разряд регистра 3 сдвига. Такты 5 — 7 аналогичны тактам 1 — 3. По восьмому такту содержимое счетчика 10 равно восьми, что соответствует нахождению первого и второго разрядов (2, 1)-кода в двух старших разрядах регистра 3 сдвига, Так как веса двух младших разрядов равны единице, то нормализация их осуществляется сдвигом единицы из первого младшего раз40 ряда во второй разряд. При значении счетчика 10, равном восьми, возбуждается выход дешифратора 14 и единичным сигналом с выхода элемента 17 запрета осуществляется сдвиг единицы

45 с и-2-го в старший п-1-й разряд регистра 3 сдвига. По одиннадцатому тактовому импульсу вырабатывается сигнал переполнения счетчика 10, который устанавливает в "0" тригу0 rep 8, тем самым блокируется прохождение импульсов от генератора 13 импульсов. На этом нормализация заканчивается и с регистра 3 сдвига производится считывание нормализованного кода А, =163=0100010001.

В случае наличия более чем двух смежных единиц в регистре 3 сдвига на выходе элементов И 16 и И 6 выра1256009

1О

Формула изобретения

Устройство для нормализации избыточных кодов, содержащее регистр сдвига, четыре триггера, счетчик, дешифратор, генератор импульсов, 30 два элемента задержки, два элемента запрета, два элемента ИЛИ, пять элементов И, причем инверсный выход первого элемента ИЛИ соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с выходом переноса и выходом (n-1)-го разряда регистра сдвига, выход первого элемента И соединен с первым входом второ- 4О го элемента ИЛИ, выход которого соединен с входом нулевого разряда регистра сдвига, выход нулевого разряда которого соединен с первым входом третьего элемента И, выход кото- 45 рого соединен с единичным входом первого триггера, нулевой выход которого соединен с первым входом четвертого элемента И, выход которого соединен с нулевым входом второго триггера, выход которого соединен с первым входом пятого элемента И, выход которого соединен с тактовым входом регистра сдвига и счетным входом счетчика, выход переполнения которого 5 соединен с вторым входом четвертого батывается единичный сигнал, устанавливающий триггер 7 в единичное состояние, в результате чего элемент И 11 закрыт,. и блокируется обнуление триггера 8 по сигналу переполнения счет- 5 чика 10. В этом случае цикл нормализации кода повторяется еще раз, при этом задержанным сигналом переполнения счетчика 10 через элемент 9 задержки триггер 7 устанавливается в нулевое состояние °

В режиме контроля на вход 1 задания режима устанавливается нулевой сигнал. В результате после установки триггера 8 в единичное состояние на сдвиговый регистр 3 от генератора 13 поступает только одна серия из п тактовых импульсов. При этом, если в каких-либо соседних разрядах окажутся г+1 смежных единиц, триггер 2 уста- Ю навливается в единичное состояние и на контрольном выходе появится единичный сигнал, свидетельствующий об ошибке. элемента И и через первый элемент задержки — с нулевым входом первого триггера, вход пуска устройства и выход генератора импульсов соединены соответственно с единичным входом второго триггера и вторым входом пятого элемента И, разрядный выход счетчика соединен с входом дешифратора, (п-3)-й выход которого соединен с первым информационным входом первого элемента запрета, выход которого соединен с входами (n-2)-го и (n-1)-го разрядов регистра сдвига, выходы (n-2)-го и (n-1)-го разрядов регистра сдвига соединены соответственно со вторым информационным и управляющим входами первого элемента запрета, выход второго элемента И соединен с единичным входом третьего триггера, вторым входом второго элемента ИЛИ и информационным входом второго элемента запрета, управляющий вход которого соединен с вторым входом третьего элемента И и входом задания режима устройства, выход второго элемента запрета соединен с единичным входом четвертого триггера, выход которого является контрольным выходом устройства, выход третьего триггера соединен с первым входом первого элемента ИЛИ и через второй элемент задержки — с вторым входом первого элемента ИЛИ и нулевым входом третьего триггера, разрядные входы и выходы регистра сдвига являются соответственно информационным входом и выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет работы при различных значениях характеристического параметра, оно содержит шестой и седьмой элементы И, причем выходы разрядов с (и-2)-ro по и-(г+1)-й регистра сдвига соединены соответственно с входами с первого по r-й шестого элемента И (r — значение характеристического параметра, выход которого соединен с третьим входом второго элемента И и входами разрядов с (n-3)-го по и-(г+ 1)-й регистр сдвига, выходы разрядов с первого по Г-й которого соединены с соответствующими входами седьмого элемента И, выход которого соединен с третьим входом третьего элемента И.

1256009

Составитель А.Клюев

Техред Л.Сердюкова Корпектор А.Обручар

Редактор П.Коссей

Заказ 4824/48 Тираж 671 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )ll-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4