Сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностирования цифровой аппаратуры. Целью изобретения является сокращение времени обнаружения многократных искажений входных сигналов в одном из тактов работы многовыходного объекта контроля. Сигнатурный анализатор содержит два регистра, сдвиговый регистр, группу элементов И и группу сумматоров по модулю два. Первый регистр предназначен для выбора совокупности контролируемых выходов объекта контроля. Элементы памяти второго регистра обеспечивают временной сдвиг последовательностей выходных сигналов, а сумматоры по модулю два производят суммирование выходных сигналов в каждом такте с учетом временного сдвига. При этом многократное искажение выходных сигналов в одном из тактов работы объекта контроля приводит к искажению нескольких разрядов суммарной последовательности, что, в конечном счете, обусловливает сокращение времени обнаружения таких искажений. 1 ил. N5 СЛ 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1256031

А1

1 у 4 б 06 F 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3874286/24-24 (22) 25.03.85 (46) 07.09.86. Бюл. № 33 (72) С. Н. Никулин и А. И. Алехин (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 792256, кл. G 06 F 11/00, 1979.

Авторское свидетельство СССР № 1048475, кл. G 06 F 11/00, 1981. (54) СИГНАТУРНЫЙ АНАЛИЗАТОР (57) Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и диагностирования цифровой аппаратуры. Целью изобретения является сокращение времени обнаружения многократных искажений входных сигналов в одном из тактов работы многовыходного объекта контроля. Сигнатурный анализатор содержит два регистра, сдвиговый регистр, группу элементов И и группу сумматоров по модулю два. Первый регистр предназначен для выбора совокупности контролируемых выходов объекта контроля.

Элементы памяти второго регистра обеспечивают временной сдвиг последовательностей выходных сигналов, а сумматоры по модулю два производят суммирование выходных сигналов в каждом такте с учетом временного сдвига. При этом многократное искажение выходных сигналов в одном из тактов работы объекта контроля приводит к искажению нескольких разрядов суммарной последовательности, что, в конечном счете, обусловливает сокращение времени обнаружения таких искажений. 1 ил.

1256031

Формула изобретения

1

Изобретение относится к цифровой вы ислительной технике и может быть использовано для контроля и диагностирования применяемой в ней цифровой аппаратуры.

Цель изобретения — сокращение времени обнаружения многократных искажений входных сигналов в одном из тактов работы многовыходного объекта контроля.

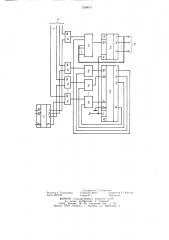

На чертеже представлена функциональная схема сигнатурного анализатора.

Он содержит первый регистр 1, сдвиговый регистр 2, второй регистр 3, группу элементов И 4, сумматоры 5 и 6 по модулю два, группу 7 информационных входов, синхровход 8, группу 9 информационных выходов.

Сигнатурный анализатор работает следующим образом.

После подачи питания регистры 2 и 3 устанавливаются в нулевое состояние, а в регистр 1 записывается двоичный код, соответствующий совокупности анализируемых выходов объекта контроля. Сигналы с выходов разрядов регистра 1, установленных в единичное состояние, поступают на вторые входы элементов И 4, разрешая прохождение сигналов с объекта контроля по соответствующим информационным входам 7 на сумматоры по модулю два 5 и 6.

Затем на входы 7 сигнатурного анализатора подаются сигналы с выходов контролируемого объекта xi(t), хг(1),..., xm(t), а на вход 8 подаются импульсы, синхронизирующие работу объекта контроля и сигнатурного анализатора.

Сигнал xi(t) через первый элемент И 4 поступает на первый сумматор 5 по модулю два, где осуществляется его сложение по модулю два с сигналом, поступающим с выхода первого разряда регистра 3: y(t)=x (t) ®

®zi (t).

Сигнал zi (t) записан в регистр 3 на предыдущем такте t — 1 и равен сумме по модулю два сигнала x (t — 1) со второго информационного выхода и сигнала z (t — 1), поступающего со 2-го разряда регистра 3:

zi(t)=x (t — 1) ®zq(t — 1). Сигнал zz(t — 1), в свою очередь, образован сигналами хз(1 — 2) и z3(t — 2): zz(t — 1) =хз(1 — 2) Юкз(1 — 2) и т.д.

Выразив значение сигналов на выходах регистра 3 через значения сигналов, поступающих на информационные входы 7, получим

y(t) =xi (t) ®хг(1 — 1) ®."Qx (t — m+1).

Таким образом, последовательность сигналов y(t) является суммой по модулю два последовательностей выходных сигналов об.ьекта контроля, сдвинутых один относительно другого на один такт. При этом любые искажения сигналов в одном из тактов выходных последовательностей контролируемого объекта за счет введенной операции сдвига приведет к искажению по10

45 следовательности y(t) по крайней мере в одном такте.

Сумматор 5 по модулю два, связанный с регистром 2, образует формирователь сигнатур и производит деление многочлена, соответствующего последовательности y(t), на образующий полином Р(1), соответствующий разрядности регистра 2 и совокупности выходов регистра 2, подключенных к входам первого сумматора 5 по модулю два.

После окончания последовательности у (1) регистр 2 устанавливается в состояние, соответствующее сигнатуре-остатку от деления у (t) на Р (1) . Полученная сигнатура сравнивается с эталонной. Искажения в некоторых разрядах у(t) приведут к тому, что полученная сигнатура будет отличаться от эталонной, что свидетельствует о неисправности контролируемого объекта. В случае совпадения полученной и эталонной сигнатур делается вывод о работоспособности контролируемого объекта.

Таким образом, предлагаемый сигнатурный анализатор позволяет за один цикл проверки контролируемого объекта определить его отказ, заключающийся в искажении выходных сигналов в одном из тактов работы, что обусловливает сокращение времени обнаружения таких искажений.

Сигнатурный анализатор, содержащий первый регистр, группу элементов И, группу сумматоров по модулю два и сдвиговый регистр, причем первые входы элементов И являются группой информационных входов анализатора, выходы элементов И подключены к первым входам соответствующих сумматоров по модулю два, а вторые входы элементов И соединены с соответствующими выходами первого регистра, группа информационных входов которого является группой входов установки режима анализатора, выход первого сумматора по модулю два подключен к информационному входу сдвигового регистра, группа входов первого сумматора по модулю два соединена с группой выходов сдвигового регистра, синхровход анализатора соединен с синхровходом сдвигового регистра, группа выходов которого является группой выходов анализатора, отличаюи1ийся тем, что, с целью сокращения времени обнаружения многократных искажений входных сигналов, он содержит второй регистр, причем второй вход i-го сумматора по модулю два (i=i, m, где m — разрядность второго регистра) соединен с выходом

i-го разряда второго регистра, выход j ãî сумматора по модулю два (j=2,m) соединен

c(j — 1)-м входом второго регистра, m-й вход которого подключен к шине нулевого потенциала, вход управления записью второго регистра соединен с синхровходом анализатора, 1256031

Составитель С. Старчнкпн

Редактор С. Патрушева Техред И. Верес Корректор A. Обручар

Заказ 4825/49 Тираж 671 Г!одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Рау шская наб.. д. 4!5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4