Аналого-цифровое делительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике. Устройство содержит два преобразователя код-напряжение, два блока сравнения, два элемента И, генератор тактовых импульсов, счетчик, сдвиговый регистр и элемент НЕ. Повышение быстродействия при делении большего сигнала на меньший достигается на основе предварительного уменьшения сигнала делимого до напряжения, меньшего или равного сигналу делителя, и последуюш,его определения кода результата деления на основе уравновешивания сигналов, поступаюших на первый блок сравнения. При этом разделение во времени реализуется по результату сравнения сигналов на втором блоке сравнения, выходной сигнал которого управляет работой элементов И. I ил. S to СП о 4ib О5

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU „„1256046 (1) 4 G 06 G 7 16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 13

К АBTOPCHOMV СВИДЕТЕЛЬСТВУ

Авторское свидетельство СССР № 511598, кл. G 06 G 7/16, 1974.

Авторское свидетельство СССР № 809225, кл. G 06 G 7/163, 1979. (21) 3840758/24-24 (22) 25.12.84 (46) 07.09.86. Бюл. № 33 (71) Научно-производственное объединение космических исследований при АН АЗССР (72) И. А. Курковский, Ф. М. Исмаилов и И. И. Злькинд (53) 681.335 (088.8) (56) Авторское свидетельство СССР № 879602, кл. G 06 G 7/161, 1980. (54) АНАЛОГО-ЦИФРОВОЕ ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к автоматике и вычислительной технике. Устройство содержит два преобразователя код-напряжение, два блока сравнения, два элемента И, генератор тактовых импульсов, счетчик, сдвиговый регистр и элемент НЕ. Повышение быстродействия при делении большего сигнала на меньший достигается на основе предварительного уменьшения сигнала делимого до напряжения, меньшего или равного сигналу делителя, и последующего определения кода результата деления на основе уравновешивания сигналов, поступающих на первый блок сравнения. При этом разделение во времени реализуется по результату сравнения сигналов на втором блоке сравнения, выходной сигнал которого управляет работой элементов И. 1 ил.

1256046

Формула изобретения

Изобретение относится к автоматике и вычислительной технике и может быть использовано при обработке информации в аналого-цифровых вычислительных системах.

Целью изобретения является повышение быстродействия при делении большего сигнала на меньший.

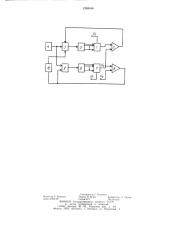

На чертеже изображена блок-схема аналого-цифрового делительного устройства.

Устройство содержит первый преобразователь 1 код — напряжение, первый блок 2 сравнения, первый элемент И 3, генератор 4 тактовых импульсов, счетчик 5, сдвиговый регистр 6, второй преобразователь 7 коднапряжение, второй блок 8 сравнения, второй элемент И 9 и элемент НЕ 10.

Аналого-цифровое делительное устройство работает следующим образом.

В исходном состоянии счетчик 5 обнулен. В старший разряд сдвигового регистра 6 занесена «1», а на выходе преобразователя 7 код-напряжение — сигнал Uq, равный сигналу делимого U .

Если Ui(U, т. е. сигнал делимого U меньше сигнала делителя Uq, то второй элемент И 9 закрыт сигналом с выхода второго блока 8 сравнения, а первый элемент U 3 открыт сигналами с выхода первого блока 2 сравнения и с выхода элемента НЕ 10. Импульсы с генератора 4 тактовых импульсов поступают через первый элемент И 3 на счетчик 5, выходы которого подключены к цифровому входу преобразователя 1 код-напряжение. Процесс продолжается до тех пор, пока не сработает первый блок 2 сравнения и не закроет первый элемент И 3. При этом в счетчике 5 находится код результата деления.

Если Ui)U, т. е. сигнал делимого больше сигнала делителя, то первый элемент И 3 закрыт сигналом, поступающим с выхода второго блока 8 сравнения через элемент НЕ 10 на третий вход элемента И 3, а второй элемент И 9 открыт сигналом с выхода второго блока 8 сравнения. Импульсы с генератора 4 тактовых импульсов поступают через второй элемент И 9 на сдвиговый регистр 6 и сдвигают «1» из старшего разряда в последующие до тех пор, пока напряжение U> на выходе второго преобразователя 7 код — напряжение настанет меньше напряжения Uz. В этот момент срабатывает второй блок 8 сравнения, второй элемент И 9 закрывается сигналом с выхода второго блока 8 сравнения, а первый элемент И 3 открывается сигналом, поступающим с выхода второго блока 8 сравненния через элемент HE 10 на третий вход элемента И 3. При этом на первом входе первого блока 2 сравнения сигнал делителя устройства Uz, а на втором входе сигнал U,=- -ф-, где п — количество сдвигов

50 сдвигового регистра 6. Поскольку U (U, счетчик 5 начинает счет импульсов, поступающих с генератора 4 тактовых импульсов, преобразователь 1 преобразует их число в напряжение до тех пор, пока не сработает блок 2 сравнения и не закроет первый элемент И 3.

При этом процесс деления заканчивается.

В счетчике 5 находится код результата деления, а в регистре 6 запоминается число сдвигов сдвигового регистра 6 с целью дешифрации запятой результата деления.

Таким образом, при делении большего сигнала на меньший быстродействие повышается благодаря тому, что в начале осуществляется сдвиг «1» из старшего разряда регистра в последующие каждым тактовым импульсом генератора, а не сигналом «Единица переполнения» с выхода счетчика импульсов, до тех пор, пока сигнал делимого не станет меньше или равным сигналу делителя, а затем осуществляется сравнение величин напряжений с выходов двух преобразователей код — напряжение первым блоком сравнения.

Аналого-цифровое делительное устройство, содержащее генератор тактовых импульсов, подключенный выходом к первому входу первого элемента И, соединенного вторым входом с выходом первого блока сравнения, а выходом — со счетным входом счетчика, выходы разрядов которого подключены к цифровому входу первого преобразователя код — напряжение, соединенного аналоговым входом с входом сигнала делителя устройства, а выходом — с первым входом первого блока сравнения, второй вход которого подключен к выходу второго преобразователя код — напряжение, соединенного цифровым входом с выходами разрядов сдвигового регистра, а аналоговым входом — с входом сигнала делимого устройства, отличающееся тем, что, с целью повышения быстродействия при делении большего сигнала на меньший, в него дополнительно введены второй элемент И, элемент HE и второй блок сравнения, подключенный входами к выходу второго преобразователя код-напряжение и входу сигнала делителя устройства, а выходом — к первому входу второго элемента И и входу элемента НЕ, выход которого соединен с третьим входом первого элемента И, причем второй элемент И подключен вторым входом к выходу генератора тактовых импульсов, а выходом — к тактовому входу сдвигового регистра.

1256046

Составитель С. Казинов

Редактор А. Воровин Техред И. Верес Корректор .1. Патай

За к а з 4 825, 49 Тираж 67! Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4!5

Филиал ППГ1 «Патент», г. Ужгород, ул. Проектная, 4