Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах , содержащих динамические элементы памяти, требующие выполнения периодической регенерации содержимого. Цель изобретения - повышение быстродействия устройства. Запоминающее устройство содержит блок памяти, блок MecTkoro управления, блок управления, мультиплексор, последовательно соединенные генератор импульсов, делитель частоты, формирователь сигналов и счетчик, два триггера и одновибратор. Устройство работает в двух режимах , обращение и регенерация. Устройство имеет полностью синхронную схему, что и позволяет повысить его быстродействие за счет устранения внутренних запасов времени, присущих асинхронным схемам из-за разброса параметров их элементов. 5 ил. (Л N3 СЛ 05 О QD а

СОЮЗ СОВЕТСНИХ .СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1256096 А 1 (5D4С 11 С 11 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ пользовано в запоминающих устройствах, содержащих динамические элементы памяти, требующие выполнения периодической регенерации содержимого.

Цель изобретения — повышение быстродействия устройства. Запоминающее устройство содержит блок памяти, блок местного управления, блок управления, мультиплексор, последовательно соединенные генератор импульсов, делитель частоты, формирователь сигналов и счетчик, два триггера и одновибратор. Устройство работает в двух режимах, обращение и регенерация. Устройство имеет полностью синхронную схему, что и позволяет повысить его быстро- 3 действие за счет устранения внутренних запасов времени, присущих асинхронным схемам из-за разброса пара- Се метров их элементов. 5 ил. (21) 3848634/24-24 (22) 23.01.85 (46) 07.09.86. Бюл, N - 33 (71) Киевский ордена Трудового Крас ного Знамени завод электронных вычислительных и управляющих машин (72) Е.Я. Белалов, В.К. Бочков,,Э.В. Рудаков и С,П. Саламатов (53) 681,327(088.8) (56) Патент ФРГ Ф 2637004, кл. 42 Т 27/00, опублик. 1976.

Андреев В.П., Баранов В.В. Бекин Н.В. Полупроводниковые запоминающие устройства и их применение. Под ред. А.Ю. Гордонова. М.: Радио и связь, 1981, с. 127, рис. 3.19. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть ис1256096

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах.

Цель изобретения — повьппение быстродействия устройства.

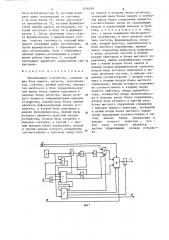

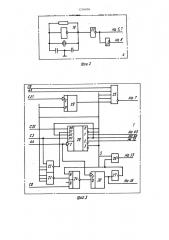

На фиг. 1 изображена структурная схема запоминающего устройства; на фиг. 2 — структурная схема генератора импульсов; на фиг. 3 — структурная схема блока местного управления; на фиг. 4 — структурная схема формирователя сигналов; на фиг. 5 — структурная схема блока управления.

Запоминающее устройство (фиг. 1) содержит блок 1 местного управления, формирователь 2 сигналов, блок 3 управления, генератор 4 импульсов, делитель 5 частоты, счетчик 6, первый

7 и второй 8 триггеры, мультиплексор

9, блок 10 памяти, регистр 11, одновибратор 12.

На фиг. 1 обозначены: информационный вход 13, адресный вход 14,управляющие входы 15 и 16, информационный

17 и управляющий 18 выходы устройства. Генератор 4 импульсов (фиг. 2) содержит кварцевый генератор 19 и инверторы 20 и 21.

Блок 1 местного управления (фиг.2) содержит элементы И-НЕ 22 и 23, элемент И-ИЛИ-НЕ 24, элементы И-HE 25 и

26, элемент НЕ 27, регистр 28 и триггеры 29 и 30. Формирователь 2 сигналов (фиг. 4) содержит триггер 31 и элемент И-НЕ 32. Блок 3 управления (фиг. 5) содержит регистр 33, триггеры 34-36, элемент И-ИЛИ-НЕ 37, элементы НЕ 38 и 39, элемент ИЛИ 40,элемент НЕ 41 и элемент И 42.

Запоминающее устройство может содержать динамические элементы памяти, расположенные по строкам и столбцам и требующие выполнения периодической регенерации содержимого. Поэтому устройство имеет два режима работы: обращение и регенерация, В,первом режиме выполняется обмен данными с процессором, а во втором — регенерация содержимого блока памяти.

В режиме обращения устройство работает следующим образом.

С входа 15 сигнал "Запрос" поступает на триггер 8, который выполняет синхронизацию этого сигнала. Синхронный запрос с выхода триггера 8 поступает на вход блока 1, который формирует сигнал разрешения работы триггера 7, который запускает управляемую

55 серию синхросигналов, частота которои в два раза ниже, чем исходная частота генератора 4.

Затем блок 1 анализирует занятость устройства и наличие запросов. Если устройство свободно, то он формирует признак режима обращения, который поступает на вход блока 3 управления, который вьщает управляющие сигналы в мультиплексор 9, блок 1О, регистр 11, а также признак занятости, который поступает в блок 1.

Мультиплексор 9 принимает адрес обращения с входа 14 и формирует две посылки, сначала старшие разряды адреса (адрес строки), затем младшие разряды адреса, которые поступают в блок

10 который принимает с входа 16 сигнал Запись". Последний задает одну из двух операций: запись (ниэкий уровень) и чтение (высокий уровень). При операции "Запись" блок 10 принимает данные с входа 13, две посылки адреса с мультиплексора 9, стробы приема адреса строки и адреса столбца с блока 3.

При операции "Чтение" блок памяти принимает те же сигналы с блоков 9 и 3 и выдает считанные данные в регистр 11, с выхода которого данные поступают на выход 17 устройства.

В конце операции блок 3 снимает признак занятости и вьщает ответ на выход 18. Процессор снимает запрос 15, блок 1 снимает признак режима обращения и разрешение работы триггера 7, после чего прекращает вырабатываться управляемая синхронизация.

В режиме регенерации устройство работает следующим образом.

Генератор 4 формирует непрерывную серию импульсов, высокой частоты, которая поступает на вход делителя 5 частоты, который вырабатывает последовательность импульсов низкой частоты,которая поступает на вход формирователя 2. С выхода последнего сигнал . поступает на вход блока 1, который вьщает сигнал разрешения работы триггера 7, которьп запускает управляемую серию синхросигналов. Затем блок 1 . анализирует занятость устройства и наличие запросов. Если устройство свободно, то блок 1 формирует признак режима регенерации. В случае конфликта, т.е. при поступлении. двух запросов одновременно, запрос регенерации имеет более высокий приоритет. Приз,нак режима регенерации поступает на

1256096 вход мультиплексора 9, который передает адрес регенерации со счетчика

6 на вход блока 10. Затем запускается оцновибратор 12, который формирует строб приема адреса регенерации, который поступает в блок 10 и формирователь 2. После окончания этого строба формирователь 2 вырабатывает сигнал запуска счетчика 6, который формирует следующий адрес регенерации. 10 Затем формирователь 2 сбрасывает запрос регенерации, блок 1 сбрасывает признак режима регенерации и разрешение работы триггера 7, которыйпрекращает выработку управляемой син- 5 хросерии.

Формула и з о б р е т е н и я

Запоминающее устройство, содержа- ур .щее блок памяти, регистр, лультиплек сор, счетчик, первый триггер, генератор импульсов и блок управления,причем выход блока памяти подключен к первому входу регистра, выход кото- 25 рого является информационным выходом устройства, первый вход блока памяти является информационным входом устройства, а второй вход подключен к выходу мультиплексора, первый вход которого является адресным входом устройства, второй вход соединен с выходом счетчика, а третий — с первым выходом блока управления, второй и третий выходы которого подключены соответственно к третьему входу бло35 ка памяти и второму входу регистра, четвертый вход блока памяти и четвертый выход блока. управления являются соответственно одним из управляющих входов и управляющим выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены делитель частоты, формирователь сигна— лов, второй триггер, одновибратор и блок местного управления, причем выход генератора импульсов подключен к входу делителя частоты и первым входам триггеров и блока местного управления, выход одновибратора соединен с пятым входом блока памяти и первым входом формирователя сигналов, второй вход которого подключен к выходу делителя частоты, а выходы соединены соответственно с входом счетчика и вторым входом блока местного управления, выходы которого подключены соответственно к второму входу первого триггера, входу одновибратора, четвертому входу мультиплексора и первому .входу блока управления, второй вход которого и третий вход блока местного управления соединены с выходом первого триггера, четвертый и пятый входы блока местного управления подключены соответственно к пятому выходу блока управления и выходу второго триггера, вто рой вход которого является другим управляющим входом устройства.

1256096

1256096

Составитель В. Рудаков

Техред А.Кравчук Корректор Л. Пилипенко

Редактор А. Сабо

Заказ 4830/52 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4