Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение .относится к вычислительной технике, в частности к интегральным запоминающим устройствам на биполярных транзисторах. Целью изобретения является повьшение быстродействия запоминающего устройства. (ЗУ). ЗУ содержит матрицу элементов памяти на биполярных транзисторах, две группы усилительных и первую группу нагрузочных транзисторов, источники тока строк и управляющие транзисторы, служащие для выборки строк, три группы переключающих транзисторов , и три источника тока, служащие для выборки разрядов. Кроме того, в устройство введены вторая группа нагрузочных транзисторов, третья группа резисторов, четвертая группа переключающих транзисторов, две группы диодов, создамцих форсированный режим перезаряда емкостей разрядных шин, и четвертый источник тока разрядов , создающий дополнительный ток в разрядных пшнах устройства. Поскольку дополнительный ток протекает только в течение форсированного режима переходного процесса перезаряда емкостей разрядных шин, время выборки снижается. Помехоустойчивость ЗУ не снижается, так как в стационарном режиме дополнительный ток в вибираемьй элемент памяти не течет. 2 ил. сл NP сл О) о ;о

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИХ

„„SU„,, 1256097 А 1 (59 4 G 11 С 11/40

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ л

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ "! (21) 3847601/24-24 (22) 21. 01. 85 (46) 07.09.86. Бюл. У. 33 (72) Ю.В.Барчуков, О.М.Лавриков, В.А.Неклюдов и А.Г.Сергеев (53) 681.327 (088.8) (56) Электронная техника. Сер.

Микроэлектроника, 1975, вып.3, с ° 15.

IEEE J. of So1id State Sircuits, 1983, Ф 5, р.515. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к интегральным запоминающим устройствам на биполярных транзисторах. Целью изобретения является повышение быстродействия:запоминающего: устройства, (ЗУ). ЗУ содержит матрицу элементов памяти на биполярных транзисторах, две группы усилительных и первую группу нагрузочных транзисторов, источники тока строк и управляющие транзисторы, служащие для выборки строк, три группы переключающих транзисторов,и три источника тока, служащие для выборки разрядов. Кроме того, в устройство введены вторая группа нагрузочных транзисторов, третья группа резисторов, четвертая группа переключающих транзисторов, две группы диодов, создакицих форсированный режим переэаряда емкостей разрядных шин, и четвертый источник тока pasрядов, созданиций дополнительный ток в разрядных шинах устройства. Поскольку дополнительный ток протекает только в течение форсированного режи- Я ма переходного процесса перезаряда емкостей разрядных шин, время выборки снижается. Помехоустойчивость ЗУ С" не снижается, так KcLK в стационарном режиме дополнительный ток в вибирае- Я мый элемент памяти не течет. 2 ил.

Изобретение относится к вычислительной технике и может быть применено в запоминающих устройствах (ЗУ), выполненных на биполярных запоминающих транзисторах.

Цель изобретения — повышение быСтродействия устройства.

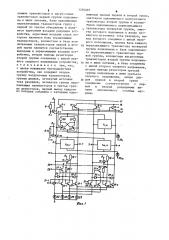

На фиг. 1 представлена принципиальная схема предлагаемого устройства; на фиг. 2 — принципиальная схема элемента памяти.

Предлагаемое устройство содержит (фиг. 1) матрицу элементов 1„„ -1 памяти, соединенных в m строк шинами

2,-2 и и столбцов разрядными шинами 3, -3„ и 4„ -4„, управляющие транзисторы 5„ -5, первую группу резисторов 6„ -6„„ адресные входы 7, -7,„ строк, шину 8 питания, первую 9, -9„ и вторую 10, -10 группы усилительных транзисторов с выходами 11 и 12 и управляющими входами 13 и 14 устройства, первую группу нагрузочных транзисторов 15„ -15, вторую группу

Э резисторов 16„-16, шину 17 первого опорного напряжения, группы с первой по третью переключающих транзисторов

18 -18 19 — 19 и 20 -20 с адреси 1 ными входами 21, -21 разрядов устройства, источники 22-24 с первого по третий тока разрядов, первую 25;—

25„ и вторую 26 -26„ группы диодов, 1 вторую группу нагрузочных транзисторов 27,-27, третью группу резисторов 28„ -28„, шины 29 и 30 соответственно второго и третьего опорных напряжений, четвертую группу переключа щих транзисторов 311 -31л четвертый источник 32 тока разрядов и источники 33„ — 33 тока строк, каждый из элементов 1ц -1 „ памяти содержит (фиг ° 1) первый 34 и второй 35 запоминающие транзисторы и нагрузочные элементы 36 и 37, выполненные на резисторах или транзисторах 38 и 39 (фиг. 2). Резисторы 28 и шина 30 в некоторых применениях могут быть исключены. Данное устройство может быть использовано также в ЗУ с потенциальным считыванием, в которых базы транзисторов 9 и 10 соединены с соответствующими шинами 3 и 4, а эмиттеры этих транзисторов в каждом столбце соединены между собой и с дополнительными источниками токов.

Предлагаемое устройство работает следующим образом.

1256097

)выборка информации осуществляется обычным для ЗУ такого типа образом.

Рассмотрим для определенности выборку элемента 1„ памяти. При выборке

5 этого элемента с входа 7 ток не по1 ступает и на шине 2, поддерживается низкий потенциал..На входе 21

1 низкий потенциал и транзисторы 181, 19, 20,,31, выключены. Потенциалы

10 на шинах 3, и 4, равны, поддерживаются транзистором 151 на высоком уровне и определяются из уравнения

U Š— U

РШ оП1

15 где UoÄ„вЂ” величина первого опорного напряжения на шине 17;

U — прямое напряжение эмитЬэ15 терного перехода транзис20 тора 15, Величины опорных напряжений на шине 30 E „ E выбиоП3 опт раются иэ соотношений б

25 Е > 11 — П р с В +

one - on 3 Бэ ГР27. де П 5гр

30 и ББэгр р-1 граничные напряжения отпирания диодов 251, 26, и транзистора

27, .

При этом диоды 25, 26 и тран35 зистор 27, закрыты, При выборке элемента 1 ток, поступающий из источника опорного напряжения на шину

7, выключается и через эмиттерный

1 повторитель на транзисторе 5 на ши1

40 ну 2, поступает положительный импульс напряжения, а в результате подачи импульса напряжения на вход

21, в шине 31 и 4 1 через транзисто- ры 18, и 19, поступают разрядные

45 токи I„, приблизительно равные токам, задаваемым источниками 22 и 23. Одновременно включается транзистор 20, и его коллекторный ток (приблизительно равный току источника 24) проте50 кающий через резистор 16, приводит к снижению потенциала на базе транзистора 15, . В результате транзистор

15, закрывается и начинается процесс разрядки емкостей С „ разряцных шин

55 3 и 4 токами этих шин I а потенциалы на этих шинах понйжаются. При выборке включается транзистор 31 и

1 его коллекторный ток (приблизитель10

Срш U в р ри рш

t рВ в котором аБ — логический nepePU3 пад напряжения на разрядной шине, а ток I складывается из тока и тока через соответствущий диод 25

1 или 26,. В ЗУ большой информационной емкости (более четырех К бит)

С образуется емкостями m элементов памяти и величина t по отнорш ,шению к полной задержке считывания составляет

20 м (0,5...0,7) t, 3 и задержки сигналов в транзисторах

5,, 15 и 27, пренебрежимо малы в

1 сравнении с t, что повышает быстродействие ЗУ.

Рассмотрим считывание логической в! и

1 из элемента 1 . При этом тран11 зистор 35 включен, а транзистор 34 выключен. Величина Е выбирается оп 2. из соотношения

Š— U м Ц о111 6327 = 635 БЭЭЬ 3 6 напряжения на прямосмещенном эмиттерном пере- 40 ходе транзисторов

27, 35 и диода 26 соответственно потенциал базы транзистора 35 в 45 режиме выборки.

БЭ 27 РЭ35 и 0 6

535

При этом по окончании процесса разряда емкости шины 4, когда потен1 циал на ней опускается на столько, 50 что отпирается эмиттерный переход транзистора 35, диод 26 закрывается, 1 а транзистор 27, открывается и ток отводится в транзистор 27, обеспечивает ускоренный перезаряд емкостей ээ шин 3„, 4„ и протекает в них только в течение длительности переходного процесса в этих шинах, за счет чего

12560 но равный току 1 источника 32) протекает через резистор 28 и понижает, t потенциал на коллекторе транзистора

3 1,. В результате этого диоды 25, и 26, отпираются и часть тока I

5 через эти диоды поступает в шины 3

1 и 4,. Длительность процесса разряда емкости С определяется соотношением

97 повышается быстродействие устройства. В стационарном режиме дополнительный ток в разрядных шинах не течет, поэтому помехоустойчивость не снижается.

Формула и щ о б р е т е н и я

Запоминающее устройство, содержащее группы усилительных транзисторов, управляющие транзисторы, первую группу нагрузочных транзисторов, группы переключающих транзисторов, группы резисторов, источники тока строк, источники тока разрядов в матрицу элементов памяти, каждый из которых состоит из нагрузочных элементов, выполненных из резисторов, первого и второго запоминающих транзисторов, коллекторы и базы которых соединены по триггерной схеме с первыми выводами нагрузочных элементов, первые эмиттеры подключены к входу соответствующего источника тока строки, а вторые эмиттеры — соответственно к первой и второй разрядным шинам столбца матрицы, причем вторые выводы нагрузочных элементов всех элементов памяти строки соединены с эмиттером соответствующего управляющего транзистора, коллектор и база которого подключены к выводам соответствующего резистора первой группы, первая разрядная шина каждого столбца матрицы соединена с эмиттером одноименного усилительного транзистора первой группы, коллектором одноименного переключающего транзистора первой группы и первым эмиттером соответствующего нагрузочного транзистора первой группы, второй эмиттер которого подключен к второй разрядной шине этого же столбца матрицы, эмиттеру одноименного усилительного транзистора второй группы и коллектору одноименного переключающего транзистора второй группы, база каждого нагрузочного транзистора первой группы подключена к коллектору одночменного переключающего транзистора третьей группы и первому выводу одноименного резистора второй группы, эмиттеры переключающих транзисторов групп с первой по третью соединены с входами источников тока разрядов с первого по третий соответственно, выходы источников тока соединены с шиной нулевого потенциала, коллекторы управ1256097

)Ф

12 иг.

5 ляющих транзисторов и нагрузочных транзисторов первой группы подключены к шине питания, базы одноименных переключающих транзисторов групп с первой bio третью объединены и являются адресными входами разрядов устройства, адресными входами строк которого являются базы управляющих транзисторов, коллекторы и базы усилительных транзисторов первой и второй групп являются соответственно выходами и управляющими входами устройства, вторые выводы резисторов второй группы соединены с шиной первого опорного напряжения устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, оно содержит вторую группу нагрузочных транзисторов, группы диодов, четвертый источник тока разрядов, четвертую группу переключащих транзисторов и третью группу резисторов, первый вывод каждого из которых соединен с катодами одноименных диодов первой и второй групп, эмиттером одноименного нагруэочного транзистора второй группы и коллектором одноименного переключающего транзистора четвертой группы, эмиттер которого подключен к входу четвертого источника тока разрядов, выход которого соединен с шиной нулевого потенциала, причем база каждого

10 переключающего транзистора четвертой группы подключена к базе одноименного переключающего транзистора первой группы, коллекторы нагрузочных транзисторов второй группы подключены к шине питания, а базы соединены с шиной второго опорного напряжения, вторые выводы резисторов третьей группы подключены к шине, третьего опорного напряжения, аноды дио20 дов первой и второй групп соединены соответственно с первой и второй разрядными шинами одноименного столбца матрицы.

1256097

Составитель Т.Зайцева

Редактор А.Сабо Техред А.Кравчук Корректор Л.Пилипенко

Заказ 4830/52 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 3-35, Раушская.наб., д.4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4