Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при наладке и функциональном контроле блоков памяти. Цель изобретения - повышение быстродействия и надежности устройства. Устройство содержит блок 1 памяти микрокоманд, регистр 2 адреса микрокоманд, регистр 3 микрокоманд, первые регистр 8 адреса данных и регистр 10 данных, вторые регистр 11 адреса данных и ре- . гистр 14 данных, первый 7 и второй 3 сумматоры. Особенностью устройства является использование.при формировании адресов и данных суммат оров 7 и 9 и регистров 11 и 14. Это позволяет в одном устройстве использовать и программный метод контроля, когда по ля адреса и данных микрокоманды непосредственно содержат исполнительный адрес и данные, и алгоритмический метод контроля, когда с помощью регистров 11 и 14 и сумматоров 7 и 9 осуществляется требуемая модификация, адреса и данных. 5 ил. (Я 1C ел О5 О СО ;о

СОЮЗ СО8ЕТСНИХ .СООИАЛИСТИЧ ЕСНИХ

РЕСПУБЛИН

ÄÄSUÄÄ1256099 А1 (Ю 4 С 11 С 29/00

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

1 фГ»- ру4 Р

II) f

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ фЩ .бр." « таад (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при наладке и функциональном контроле блоков памяти. Цель изобретения — повышение быстродействия и (21) 3856097/24-24 (22) 19.02.85 (46) 07.09.86. Sun. N - 33 (71) Харьковский ордена Ленина полигехнический институт им. В,И.Ленина (72) В.И.Август, И.Сезыков и Н.А.Иванюк (53) 681. 327 (088. 8) (56) Электронная промышленность.

Вып.2 (56), 1977, с. 20.

Авторское свидетельство СССР

¹ 1092569, кл. G 11 С 29/00, 1982. надежности устройства. Устройство содержит блок 1 памяти микрокоманд, регистр 2 адреса микрокоманд, регистр

3 микрокоманд, первые регистр 8 адреса данных и регистр 10 данных, вторые регистр 11 адреса данных и регистр 14 данных, первый 7 и второй 3 сумматоры. Особенностью устройства является использование при формировании адресов и данных сумматоров 7 и 9 и регистров 11 и 14. Это позволяет в одном устройстве испольэовать и программный метод контроля, когда по-. ля адреса и данных микрокоманды непосредственно содержат исполнительный адрес и данные, и алгоритмический ме- Е

O тод контроля, когда с помощью регистров 11 и 14 и сумматоров 7 и 9 осущестяяяется требуемая модиФикация. адреса и данных. 5 ил.

1256099 2

Изобретение относится к вычислительной технике и.может быть использовано при осуществлении наладки и контроля блоков памяти.

Цель изобретения — повышение быст.родействия и надежности устройства.

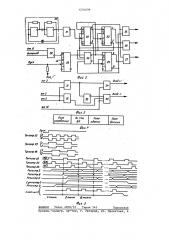

На фиг.1 изображена структурная схема устройства для контроля блоков памяти; на фиг.2 — структурная схема блока управления, на фиг.3 — структурная схема коммутатора, на фиг.4— формат микрокоманды; на фиг.5 — временные диаграммы работы устройства.

Устройство для контроля блоков памяти (фиг. 1) содержит блок 1 памяти микрокоманд, регистр 2 адреса микрокоманд, регистр 3 микрокоманд, .коммутатор 4, счетчик 5 циклов, регистр 6 кода обращения, первый сумматор 7, 1 первый регистр 8 адреса данных, второй сумматор 9, первый регистр 10 данных, второй регистр 11 адреса данных, блок 12 вывода адреса, блок 13 индикации данных, второй регистр 14 адреса данных, блок 15 вывода данных, блок 16 индикации данных, компаратор

17, блок 18 ввода данных и блок 19 управления. Блок 19 управленйя (фиг.2) содержит кварцевый генератор

20, элемент НЕ 21, первый 22, второй

23 .и третий 24 триггеры, элементы И .25-27, элемент ИЛИ-НЕ 28, четвертый триггер 29 и элемент И 30. Коммутатор 4 содержит (фиг.3) первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 31 и 32, элемент HE 33 и элементы И 34 и 35.

Устройство для контроля блоков памяти работает следующим образом.

Перед пуском устройства контроля в блок 1 памяти микрокоманд заносятся требуемые тесты в виде набора микрокоманд, формат которых изображен на фиг.4. В состав микрокоманды входят четыре поля: адреса, адреса данных, режима работы контролируемого блока памяти и управления. Поле режима работы контролируемого блока памяти содержит коды сигналов обращения

"Запись" или "Чтение" ("Зп/Чт") и выбора кристалла ("ВК"). Поля адреса и данных содержат значение адресаконтролируемого блока памяти и данные, которые либо записываются по; указанному адресу при записи, либо используются для сравнения со считанной информацией при считывании. . После управления может содержать один или несколько независимых кодов one-

Если код операции микрокоманды не содержит кодов, указывающих на изменение адреса микрокоманды, адрес микрокоманды и содержимое регистра 3 микрокоманды остаются без изменений.

В этом случае задается код П, который определит количество повторений выборки одной и той же микрокоманды по постоянному адресу микрокоманды.

По коду P разрешается поступление синхроимпульсов Т на вход счетчика

5. По переполнению счетчика 5 высо раций, определяющих режим работы отдельных блоков устройства контроля.

По сигналу пуска снимается сигнал сброса триггеров 22- 24 блока 19 и начинают вырабатываться импульсы синхронизации Т -Т, представляющих серию перекрывающихся импульсов оди-. наковой частоты (фиг.5), Синхроимпульсы определяют моменты занесения

10 информации в регистры и счетчики устройства. В устройстве организована конвейерная работа регистров 3, 8, 10, 11 и 14, что позволяет выполнить контроль блоков памяти на частоте

15 выборки блока памяти микрокоманд.

В соответствии с временной диаграммой в первом такте по синхроимпульсу Т микрокоманда с блока 1 памяти микрокоманд заносится в регистр

20 3 микрокоманд, по синхроимпульсу Т> из.меняется содержимое регистра 2. Во втором такте по синхроимпульсу содержимое полей данных, адреса и режима контролируемого блока памяти заносит25 ся в регистры 8, 10 и 6 и через блоки 12 и 15 поступает на контролируе-! мый блок памяти, по синхроимпульсу

Т в регистр 2 заносится вторая миг крокоманда, содержимое регистров 8 и

З0 10 заносится в регистры 11 и 8, по синхросигналу Т4 происходит подготовка адреса третьей микрокоманды. В третьем и последующих тактах работа блоков аналогична.

35 Если в текущей микрокоманде заданы в поле управления коды операций, то одновременно с обращением к контролируемому блоку памяти устройство выполняет заданные внутренние опера40 ции. Если код операции микрокоманды содержит код +1 или -1 (фиг.3), на входы регистра 2 поступают импульсы, которые на единицу увеличивают или . уменьшают содержимое регистра 2, тем

45 самым определяя значение адреса следующей микрокоманды.

3 1256 . кий уровень сигнала с выхода счетчика поступает на элементы ИСКЛЮЧАЮЩЕЕ, ИЛИ 31 и 32. При двух одноименных сигналах на входах высокий уровень: с выхода элемента НЕ 33 разрешает поступление синхроимпульса Т на вход

+1 регистра 2 адреса микрокоманд. Таким образом после цикла повторений чтения одной и той же микрокоманды из памяти 1 микрокоманд наступает 10 изменение адреса микрокоманды и переход к следующей очередной микроко— маиде.

В тестах контроля блоков памяти часто используются обращения к группе адресов, изменяющихся с постоянным шагом, для выполнения подобных тестов минимальным количеством микрокоманд используется команда суммирования адреса и/или данных. Если поле 20

r управления микрокоманды содержит коды операций суммирования, то поле адреса и поле данных микрокоманды содержат не значения адреса и данных, а их приращения. Значения адреса и данных 2S такой микрокоманды получают в регистрах 8 и 11 путем суммирования содержимого регистров 11 и t 4 и их приращений, поступающих на сумматоры 7 и 9 с регистра 3 микрокоманд. Таким образом, 30 используя команду суммирования, можно без изменения микрокоманды получить текущие значения адреса и/или данных с заданных приращением.

Формула изобретения

Устройство для контроля блоков памяти, содержащее последовательно соединенные регистр адреса микроко40 манд, блок памяти MHKpGKQMGHp и ре- . гистр микрокоманд, первый регистр адреса данных, первый регистр данных, блок управления, блок ввода данных, блок вывода адреса, блок индикации

45 данных,, блок индикации адреса и компаратор, причем выход первого ре- . гистра данных соединен с входами блока вывода данных, блока индикации данных и с первым входом компарато50 ра, выход первого регистра адреса данных соединен с входами блока выво099 4 да адреса и блока индикации адреса, выход блока ввода данных соединен с вторым входом компаратора, выход которого подключен к одному иэ входов блока управления, другие входы которого являются управляющими входами устройства, первый и второй выходы блока управления подключены соответственно к управляющим входам первых регистра адреса данных и регистра данных и регистра микрокоманд, о т— л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности,-в него введены вторые регистр адреса данных и регистр дан— ных, первый и второй сумматоры, счетчик циклов, коммутатор и регистр кода обращения,-причем первый и второй выходы регистра микрокоманд соединены с первым и вторым выходами комму татора, третий вход которого подключен к выходу счетчика циклов, а выходы соединены с входами регистра адре— са микрокоманд, третий выход регистра микрокоманд соединен с входом счетчика циклов, четвертый выход — с входом регистра кода обращения, пя тый и шестой выходы регистра микрокоманд соединены с первым и вторым входами первого сумматора, третий вход которого подключен к выходу второго регистра адреса данных, седьмой и восьмой выходы регистра микрокоманд . соединены с первым и вторым входами второго сумматора, третий вход которого подключен к выходу второго ре— гистра данных, входы вторых регистра данных и регистра адреса данных соединены соответственно с выходами пер-. вых регистра данных и регистра адреса данных, один из выходов регистра кода обращения соединен с третьим входом компаратора и является одним из управляющих выходов устройства, другим управляющим выходом которого является другой выход регистра кода обращения, .управляющие входы вторых регистра данных и регистра адреса, данных и счетчика циклов подключены к второму выходу блока управления, третий выход которого соединен с управляющим входом коммутатора.

1256099

Фгг»

Фиг. J

Фиг. >

Русе

Триггер 72

Триггер 7Р

Триггер М

Триггер 22

Триггер ЛУ

Триггер М

Регистр 3

Регистр.г

Регистр Н

fyw omop7

° ° Ф

Регистр 2

Счетчик 5

Imam утаит Я такт

Фиг. 5 щщИПК Заказ 4830/52 Тираж 543 Подписное

Произв,-попигр. пр-тие, г. Ужгород, ул. Проектная, 4