Формирователь синусоидального сигнала

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (1)4 НОЗ К5 01,4 02

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ :,ч, р

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ц

К АBTOPCHOMV СВИДЕТЕЛЬСТВУ

Авторское свидетельство СССР № 723767, кл. Н 03 К 5/01, 1978. (54) ФОРМИРОВАТЕЛЬ СИНУСОИДАЛЬНОГО СИГНАЛА

Ь )

4ч (Ь

Ю (21) 3847830/24-21 (22) 28.01.85 (46) 07.09.86. Бюл. № 33 (72) А. Д. Хомутов и И. А. Столяров (53) 621.374.387 (088.8) (56) Смеляков В. В. Цифровая измерительная аппаратура инфранизких частот. — М.:

Энергия, 1975, с. 124.

Авторское свидетельство СССР № 809513, кл. Н 03 К 4/02, 1979.

„,Я0„„1256120 А1 ((57) Изобретение относится к радиотехнике и может быть использовано в измерительной аппаратуре. Цель изобретения уменьшение нелинейных искажений выходного сигнала. Формирователь содержит управляемый генератор 2 импульсов, делитель 3 частоты, одновибратор 4, элементы

И 5 — 1, 5 — 2, кольцевой счетчик 9, сумматор 10 и интегратор 17. Введение триггера

6, реверсивного счетчика 7, преобразователя 8 код — напряжение, кольцевого счетчика 11, сумматоров 12 и 15, вычитателя

13, блока 14 пропуска такта и аналогового ключа 16 и образование новых функциональных связей повышают точность аппроксимации. 2 ил.

1256170

Изобретение относится к радиотехнике и может быть использовано в измерительной аппаратуре.

Цель изобретения — уменьшение нелинейных искажений выходного сигнала путем повышения точности аппроксимации.

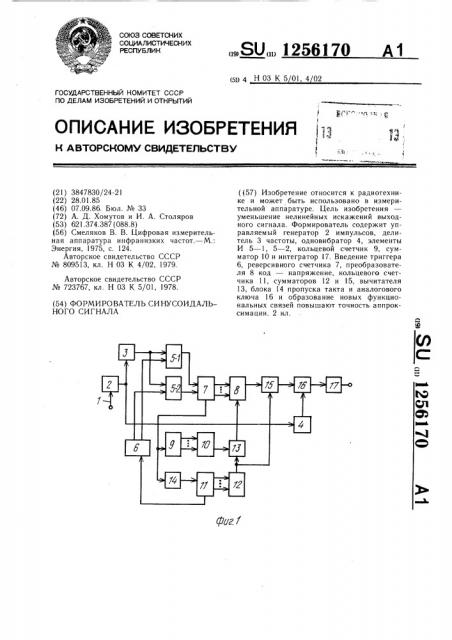

На фиг. 1 приведена функциональная схема формирования синусоидального сигнала;на фиг. 2 — функциональная схема блока пропуска такта.

Формирователь синусоидального сигнала содержит шину 1 управления, управляемый генератор 2 импульсов, делитель 3 частоты, одновибратор 4, элементы И 5 — 1 и

5 — 2, триггер 6, реверсивный счетчик 7, преобразователь 8 код — напряжение, первый кольцевой счетчик 9, первый сумматор 10, второй кольцевой счетчик 11, второй сумматор 12, вычитатель 13, блок 14 пропуска такта, третий сумматор 15, аналоговый ключ 16, интегратор 17.

Блок 14 пропуска такта содержит триггер 18 такта и элемент И 19 пропуска такта.

Управляемый генератор 2 импульсов подключен к шине 1 управления, а выходом соединен с делителем 3 частоты и одновибратором 4. Одновибратор 4 управляет аналоговым ключом 16, а делитель 3 частоты через элементы И 5 — 1 и 5 — 2 — реверсивным счетчиком 7. Реверсивный счетчик 7. первым выходом соединен с преобразователем 8 код — напряжение, а выход переноса реверсивного счетчика 7 соединен с входом первого кольцевого счетчика 9 и через блок 14 пропуска такта с входом второго кольцевого счетчика 11. Первый кольцевой счетчик 9 соединен через первый сумматор

10 с первым входом вычитателя 13, построенного на операционном усилителе, а второй кольцевой счетчик — с вторым сумматором 12. Выход второго сумматора 12 соединен с вторым входом вычитателя 13 и с вторым входом третьего сумматора 15, выход которого через аналоговый ключ 16 подключен к входу интегратора 17. Выход вычитателя 18 подключен к входу опорного напряжения преобразователя 8 код — напряжение, выход которого подключен к первому входу сумматора 15. Выход интегратора 17 является выходом формирователя синусоидального сигнала.

Устройство работает следующим образом.

Управляемый генератор 2 импульсов формирует последовательность импульсов с частотой повторения, зависящей от сигнала на шине 1 управления. Элементы И 5 — 1 и 5 — 2, триггер 6, реверсивный счетчик 7, преобразователь 8 код — напряжение, первый 9 и второй 11 кольцевые счетчики, первый 10 и второй 12 сумматоры, вычитатель 13 и блок 14 пропуска такта предназначены для линейно-ступенчатой аппроксимации синусоидального сигнала. Делитель 3 частоты, одновибратор 4, аналоговый ключ 16 и интегра5

55 тор 17 выполняют функцию стабилизации амплитуды сигнала при изменении частоты.

В начальный момент времени реверсивный счетчик 7 устанавливается в нулевое положение и сигналом переноса устанавливает второй кольцевой счетчик 11 в нулевое положение, а первый кольцевой счетчик— в первое. На вычитателе 13 сформировано напряжение первой ступени аппроксимации.

Триггер 6 установлен, и через элемент И 5 — 1 с делителя 3 частоты тактовая частота управляемого генератора 2 импульсов поступает на суммирующий вход реверсивного счетчика 7. Под управлением реверсивного счетчика преобразователь 8 код — напряжение ступенчато изменяет напряжение выхода от нулевого значения до значения напряжения первой ступени аппроксимации. Вычитатель 13 формирует напряжение, равное разности между напряжениями, установленными на выходах первого сумматора 10 и второго сумматора 12. Первый 10 и второй

12 сумматоры на входах имеют дозирующие резисторы и формируют выходное напряжение согласно кодам, установленным кольцевыми счетчиками 9 и 11. В соответствии с этим на выходе второго сумматора 12 в начальный момент времени установлено нулевое напряжение, а на выходе первого сумматора 10 — равное напряжению первой ступени аппроксимации.

Напряжения преобразователя 8 код — напряжение и второго сумматора 12 складываются третьим сумматором 15, построенным на операционном усилителе. С выхода третьего сумматора 15 ступенчатое напряжение поступает на аналоговый ключ 16, который вырезает в каждом такте узкий импульс под управлением одновибратора 4, при этом сохраняя амплитуду ступеней напряжения. Интегратор 1? выделяет огибающую аппроксимированного синусоидального сигнала.

Разность положений кольцевых счетчиков

11 и 9 образуется под управлением блока

14 пропуска такта. Последний пропускает тактовую частоту, начиная с второго такта, так как первый такт взводит триггер !8 такта и разрешает прохождение тактовой частоты через элемент И 19 пропуска такта.

По отсчету определенного числа тактов реверсивный счетчик 7 переходит в начальное положение и вырабатывает сигнал переноса, который устанавливает второй кольцевой счетчик 11 во второе положение, а первый кольцевой счетчик 9 — в первое.

На вычитателе 13 формируется напряжение второй ступени аппроксимации, а на выходе третьего сумматора 15 — напряжение, равное сумме напряжений первой ступени аппроксимации и ступенчато нарастающего напряжения второй ступени аппроксимации.

Этот процесс продолжается, причем в любой момент времени на выходе третьего сумматора 15 формируется напряжение, равное сумме предыдущего напряжения и сту1256170

Формула изобретения

Составитель Ю. Акаткин

Редактор В. Петраш Техред И. Верес Корректор В. Бутяга

Заказ 4835/56 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 пенчато нарастающего до последующей ступени аппроксимации напряжения, до достижения вторым кольцевым счетчиком 11 своего максимального значения.

При достижении вторым кольцевым счетчиком 11 максимального значения на его втором выходе появляется сигнал переноса, который сбрасывает триггер 6, после чего тактовая частота через элемент И 5 — 2 поступает на вычитающий вход реверсивного счетчика 7. Под управлением реверсивного счетчика 7 на выходе преобразователя

8 код — напряжение вырабатывается ступенчато убывающее напряжение, которое складывается на третьем сумматоре 15 с предыдущей ступенью аппроксимации, тем самым формируется спад синусоидального сигнала, в отличие от момента времени до переполнения второго кольцевого счетчика

11, когда формировался его подъем.

Процесс циклически повторяется, и на выходе интегратора 17 формируется синусоидальный сигнал.

Формирователь синусоидального сигнала, содержащий управляемый генератор импульсов, вход которого подключен к шине управления, делитель частоты, вход которого соединен с выходом управляемого генератора импульсов, одновибратор, вход которого подключен к выходу управляемого генератора импульсов, первый и второй элементы И, первый кольцевой счетчик, первый сумматор, интегратор, причем шина управления является входом, а выход интегратора — выходом формирователя синусоидального сигнала, отличающийся тем, что с целью уменьшения нелинейных искажений выходного сигнала путем повышения точности аппроксимации, в него введены триггер, прямой и инверсный выходы которого соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом делителя частоты, реверсивный счетчик, суммирующий

10 вход которого соединен с выходом первого элемента И, вычитающий вход — с выходом второго элемента И, а выход переноса — с входом первого кольцевого счетчика, выходы которого подключены к входам первого сумматора, преобразователь код— напряжение, входы данных которого соединены с выходами реверсивного счетчика, блок пропуска такта, вход которого подключен к выходу переноса реверсивного счетчика, второй кольцевой счетчик, вход которого соединен с выходом блока пропуска такта, а выход переноса — с входом триггера, второй сумматор, входы которого соединены с выходами кольцевого счетчика, вычитатель, первый и второй входы которого подключены соответственно к выходам первого и второго сумматоров, а выход— к входу опорного напряжения преобразователя код — напряжение, третий сумматор, первый вход которого соединен с выходом преобразователя код — напряжение, а второй вход — с выходом второго сумматора, аналоговый ключ, сигнальный вход которого подключен к выходу третьего сумматора, вход управления — к выходу одновибратора, а выход — к входу интегратора.