Фазовый синхронизатор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники . Цель изобретения - расширение функциональных возможностей устройства. Фазовый синхронизатор содержит коммутатор 2 и группу 3 из п последовательно соединенных элементов задержки. Введение группы 1 из п триггеров, каждый из которых D-типа, и выполнение коммутатора 2 в виде группы из п элементов И-ИЛИ позволяют осуществить фазовую синхронизацию входной импульсной последовательности с асинхронным сигналом. 1 ил. N9 СП О) 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

<511 4 ?? 03 ?? 5>

1Д

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ .СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3887728/24-21 (22) 26.03.85 (46) 07.09.86. Бюл. № 33 (72) А. К. Галанчук, С. А. Колесов и Ю. В. Соколов (53) 621.374 (088.8) (56) Авторское свидетельство СССР № 688983, кл. Н 03 К 5/153, 1978.

Авторское свидетельство СССР № 881992, кл. Н 03 К 5/1 53, 1980. (54) ФАЗОВЫЙ СИНХРОНИЗАТОР

„„SU„„1256176 (57) Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения — расширение функциональных возможностей устройства.

Фазовый синхронизатор содержит коммутатор 2 и группу 3 из п последовательно соединенных элементов задержки. Введение группы 1 из п триггеров, каждый из которых D-типа, и выполнение коммутатора 2 в виде группы из и элементов И вЂ” ИЛИ позволяют осуществить фазовую синхронизацию входной импульсной последовательности с асинхронным сигналом. 1 ил.

1256176

Формула изобретения

ВНИИПИ Заказ 4835/56 Тираж 816 Подписное

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения — расширение функциональных возможностей путем фазовой синхронизации выходной импульсной последовательности с асинхронным сигналом.

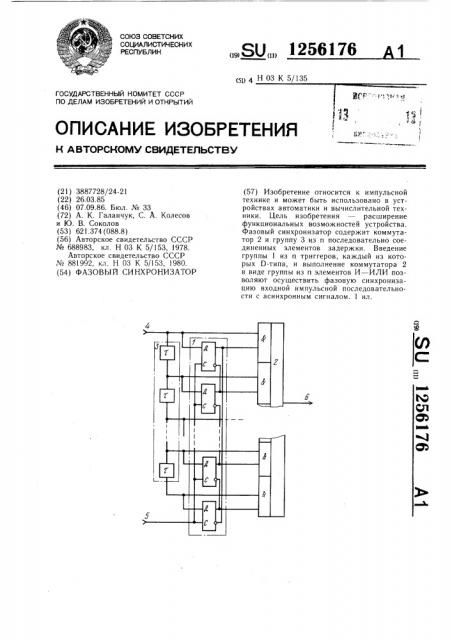

На чертеже приведена электрическая структурная схема устройства.

Фазовый синхронизатор содержит группу

1 из п триггеров, каждый из которых D-типа, коммутатор 2, выполненный в виде группы из п элементов И вЂ” ИЛИ, группу 3 из и последовательно соединенных элементов задержки, выходы каждого из которых соединены с соответствующими входами первой .группы входов коммутатора 2, причем вход первого элемента задержки из группы 1 и последовательно соединенных элементов задержки соединен с шиной 4 тактовых импульсов, с дополнительным входом первой группы входов коммутатора 2 и с D-входом первого триггера из группы 1 и триггеров, прямой выход которого соединен с дополнительным входом второй группы входов коммутатора 2 и с инверсным выходом последнего триггера из группы 1 л триггеров, С-вход которого соединен с шиной 5 асинхронного сигнала и с С-входами каждого триггера из группы 1 и триггеров. Причем выходы элементов задержки группы 2 последовательно соединенных элементов задержки соединены с D-входами соответствующих триггеров из группы 1 п триггеров, инверсный выход каждого триггера из группы 1 п триггеров соединен с прямым выходом последующего триггера из группы 1 и триггеров и с соответствующими входами второй группы входов коммутатора 2, выход которого соединен с выходной шиной 6.

Коммутатор 2 выполнен в виде К двухвходовых конъюнкторов, объединенных по ин версным выходам в монтажное ИЛИ. Такое соединение допускают ТТЛ-вентили с открытым коллектором либо ЭСЛ-вентили с открытым эмиттером.

Фазовый синхронизатор работает следуюшим образом.

На шину 4 поступают тактовые импульсы с периодом повторения Т. Проходя через группу 3 последовательно соединенных элементов задержки, сигнал размножается на К фаз, каждая из которых отстоит от соседней на время Т/К. Эти фазы постоянно присутствуют íà D-входах соответствуюших триггеров группы 1. В момент прихода на объединенные С-входы триггеров группы 1 асинхронного сигнала последние устанавливаются в логические состояния, соответствующие уровням фаз сигнала с шины 4 на их D-входах.

Зо

4О

Рассмотрим два соседних триггера. Предположим, что на D-входе первого триггера из группы 1 в момент привязки присутствовал уровень «лог. О» и он установился в состояние «Лог. О», что соответствует уровню «Лог.1», установившемуся на его инверсном выходе. На D-входе следующего за ним триггера из группы 1 в момент привязки все еще присутствует уровень «Лог. 1«, и он установится в состояние «Лог. 1». Таким образом, на объединенных инверсном и прямом выходах этих двух триггеров из группы

1 устанавливается уровень «Лог. 1». Особенностью распределения сигналов в устройстве в момент привязки является то, что рабочий фронт переключения сигнала с шины

4 из «Лог. 1» в «Лог. О». расположен между D-входами первого и второго рассмотренных триггеров из группы 1. Видно, что в группе 1 л триггеров в состояние «Лог.1 установится лишь одна пара объединенных выходов. Сформированный в момент привязки уровень «Лог. 1» пропускает через коммутатор 2 ту фазу, рабочий фронт переключения которой из «Лог. 1» в «Лог. О» наиболее близок к фронту внешнего асинхронного сигнала. Установившееся состояние триггеров из группы 1 сохраняется до прихода очередного асинхронного сигнала.

Фазовый синхронизатор, содержащий группу из и последовательно соединенных элементов задержки, выход каждого из которых соединен с соответствуюшим входом первой группы входов коммутатора, шину тактовых импульсов и выходную шину, отличающийся тем, что, с целью расширения функциональных возможностей путем фазовой синхронизации выходной импульсной последовательности с асинхронным сигналом, в него введены шина асинхронного сигнала, группа из и триггеров, каждый из которых D-типа, D-вход первого из которых соединен с входом первого элемента задержки из группы п последовательно соединенных элементов задержки, с шиной тактовых импульсов и с дополнительным входом первой группы входов коммутатора, выполненного в виде группы из и элементов И—

ИЛИ прямой выход — с дополнительным вхо дом второй группы входов коммутатора и с инверсным выходом последнего триггера и3 группы л триггеров, С-вход которого соединен с шиной асинхронного сигнала и С-входами каждого триггера из группы и триггеров, инверсный выход каждого из которых соединен с прямым выходом последующего триггера из группы и триггеров и с соответствующим входом второй группы входов коммутатора, выход которого соединен с выходной шиной.