Устройство для передачи информации шумоподобными сигналами

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и радиотехнике. Повышается скорость передачи информации. Устройство содержит на передающей стороне источник 3 цифровой информации, генератор 7 кодов Уолша, генератор 8 псевдослучайной последовательности, сумматор 9 по модулю два и балансный модулятор 12, а на приемной стороне - блок 13 выбора максимума, смеситель 17, генератор 18 опорного сигнала , интегратор 19, генератор 23 псевдослучайной последовательности и два сумматора 24 и 25 по модулю два. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (191 (и) (,511 4 Н 04 L 27/26

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ф p г

ОПИСАНИЕ ИЗОБРЕТЕНИЯ j И 13!

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3703202/24-09 (22) 20.02.84 (46) 07.09.86. Бюл. У 33 (71) Московский институт инженеров гражданской авиации (72) А.А.Кузнецов, А.В.Прохоров и В.В.Соломенцев (53) 621.394.61(088.8) (56) Лившиц А.Р. и др. Теория и проектирование многоканальных систем связи для пространственно-рассредоточенных объектов ° Л.: Ленинградский Университет, 1975, с.7 — 9.

Алексеев А.И. и др. Теория и при,менение псевдослучайных сигналов. .М.: Наука, 1969, с ° 274-276.

{54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ ШУМОПОДОБНЬ МИ СИГНАЛАМИ (57) Изобретение относится к электросвязи и радиотехнике. Повышается скорость передачи информации. Устройство содержит на передающей стороне источник 3 цифровой информации, генератор 7 кодов Уолша, генератор 8 псевдослучайной последовательности, сумматор 9 по модулю два и балансный модулятор 12, а на приемной стороне блок 13 выбора максимума, смеситель 17, генератор 18 опорного сигнала, интегратор 19, генератор 23 псевдослучайной последовательности и два сумматора 24 и 25 по модулю два.

1256239

Цель достигается введением на передающей стороне сумматора 1 сигналов, генератора 2 несущего сигнала, дешифратора 4 временной задержки, дешифратора 5 номера кода, блока 6 управления задержкой, генератора 10 тактовых импульсов и генератора 11 синхроИзобретение относится к электросвязи и радиотехнике и может быть ис1 пользовано для передачи информации.

Цель изобретения — повышение скорости передачи информации. 5

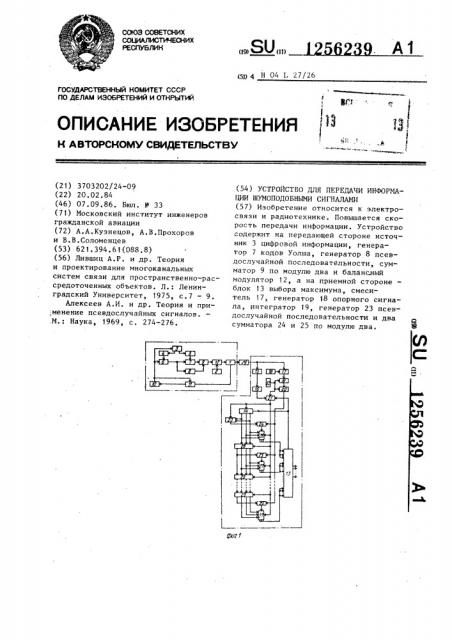

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — структурная электрическая схема блока управления задержкой; на фиг. 3 — структурная электрическая схема логического элемента; на фиг. 4 — структурная электрическая схема генератора синхросигнала; на фиг ° 5 — структурная электрическая схема счетчика-дешифратора °

Устройство для передачи информации шумоподобными сигналами содержит на передающей стороне сумматор 1 сигналов, генератор 2 несущего сигнала, источник 3 цифровой информации, деши- >О фратор 4 временной задержки, дешифратор 5 номера кода, блок 6 управления задержкой, генератор 7 кодов Уолша, генератор 8 псевдослучайной последовательности, сумматор 9 по модулю два, генератор 10 тактовых импульсов, генератор. 11 синхросигнала, балансный модулятор 12, а на приемной стороне блок 13 выбора максимума„ счетчик-дешифратор i 4,,приемник 15 синхросигна- 30 ла, первый компаратор 16„ смеситель 17, генератор 18 опорного сигна-. ла, интегратор i 9,,второй компаратор 20, логический элемент 2 1, генератор 22 тактовых импульсов, генератор 23 псевдослучайной последовательности, первый 24 и второй 25 сумматоры по модулю два, первый 26 и вторые 27 анализаторы, первый 28 и вторые 29 блоки задержки.

4О

Блок управления задержкой содержит первый 30 и второй 31 дешифрато.ры, RS-триггер 32, первый счетчик 33, сумматор 34 по модулю два с инверсией, сигнала, а на приемной стороне счетчика-дешифратора 14, приемника 15 синхросигнала, двух компараторов 16 и 20, логического элемента 21, генератора 22 тактовых импульсов, двух анализаторов 26 и 27 и двух .блоков 28 и 29 задержки.4 з.п.ф-лы,5 ил. инвертор 35, первый 36 и второй 37 элементы И, второй счетчик 38.

Логический элемент содержит RSтриггер 39 и элемент И 40, Генератор синхросигнала содержит компаратор 41, с-огласованный фильтр 42, генератор 43 шумоподобного сигнала, счетчик 44, дешифратор 45 и элемент 46 памяти.

Счетчик-дешифратор содержит счетчик 47 и первый 48, второй 49 и третий 50 дешифраторы.

Устройство работает следующим образом.

Передающая часть работает следующим образом.

Включают генератор 10 тактовых импульсов, который подает первый сигнал на генератор 11 синхросигнала и останавливается. Под действием сигнала генератор 11 синхросигнала формирует синхросигнал,длительностью Т.

По окончании его формирования он подает управляющий сигнал на генератор тактовых импульсов и запускает его. Генератор 10 тактовых импульсов работает до тех пор, пока его не включат, а генератор 11 синхросигнаz ла через каждые (2 +2 -2) такта, начиная с момента подачи на него пер- вого сигнала, начинает формирование очередного синхросигнала. При этом длительность синхросигнала Т„ не превосходит длительности (2 +2 -2) и тактов, Одновременно под действием первого сигнала генератора 10 тактовых импульсов источник 3 цифровой информации подает на дешифратор 5 номера кода К бит двоичной информации и на дешифратор 4 временной задержки L бит двоичной информации, Последние расшифровывают поданную информацию и подаюч управляющие сигналы на ге1256 нератор 7 кодов Уолша и блок 6 управления задержкой соответственно. Под действием последующих сигналов генератора 10 тактовых импульсов, поступающих через блок 6 управления за- g держкой с задержкой на 1 тактов, определяемой управляющим сигналом, и дешифратора 5 временной задержки, где 0 К 2 — 1, на генератор 7 кодов

Уолша и генератор 8 псевдослучайной последовательности последние формируют кодовую последовательность Уолша, определяемую управляющим сигналом с дешифратора 5 номера кода и псевдослучайную последовательность 15 соответственно.

Двоичные сигналы с генератора 7 кодов Уолша и генератора 8 псевдослучайной последовательности поступают на входы сумматора 9 по модулю 20 два, который производит сложение и подает результаты на вход балансного модулятора 12. Последний манипулирует фазу несущего сигнала, поступающего с генератора 2 несущего сигнала, на 025 или «, например при поступлении сиг— нала "Лог. 1" или "Лог ° 0" соответственно. Сигнал с выхода балансного модулятора 12 поступает на вход сумматора 1 сигналов, на другой вход gp которого поступает сигнал генератора

11 синхросигнала ° Сумматор 1 сигналов суммирует их и подает результирующий сигнал в линию передачи данных. При поступлении (2 +t. 1)-го сигнала на

35 блок 6 управления задержкой последний подает сигнал на генератор 7 ко-, дов Уолша и генератор 8 псевдослучайной последовательности, под действием которого они вырабатывают очередной элемент кода и переходят в исходное состояние. В это время источник 3 цифровой информации под, и действием (2 +2 -2)-ro сигнала подает новую информацию на дешифратор 5 45 номера кода и дешифратор 4 временнои задержки, которые расшифровывают ее и подают новые управляющие воздействия на генератор 7 кодов Уолша и блок 6 управления задержкой соответственно. Далее работа передающей части повторяется.

Приемная часть работает следующим образом.

Сигнал из линии передачи данных подается на вход смесителя 17, который перемножает его с сигналом, поступающим с генератора 18 опорного

239 4 сигнала, идентичным несущему. Сигнал со смесителя 17 поступает на интегратор 19, который интегрирует низкочастотную составляющую (огибающую несущего сигнала) и подает результат на компаратор 20. Поспедний н момент поступления сигналов с генератора.22 тактовых импульсов берет отсчет, принимает решение о наличии или отсутствии манипуляции фазы несущего сигнала, вырабатывает сигнал "Лог.О" или "Лог. 1" соответственно и подает его на входы сумматоров 24 и 25 по модулю два. Приемник 15 синхросигнала принимает синхросигнал из линии передачи данных и подает его на компаратор 16, который в момент прихода синхросигкала подает сигнал на первый вход логического элемента 21, переводя его н состояние, в котором он пропускает сигналы, поступающие с генератора 22 тактовых импульсов, до поступления сигнала на его вчорой вход. При поступлении сигналов с логического элемента 21 блоки 28 и 29 задержки считывают информацию. Все сумматоры 24 и 25 по модулю два складывают двоичные сигналы со своих входов.

Под действием первого сигнала с логического элемента 2 1 счетчик- дешифратор 14 вырабатывает сигнал на втором выходе и подает его на второй управляющий вход генератора 23 псевдослучайной последовательности, разрешая ей формирование до поступления сигнала на третий упранляющий вход.

Генератор 23 псевдослучайной последовательности вырабатывает первый эле— мент ПСП и подает его на второй вход первого сумматора 24 по модулю два и вход первого блока 28 задержки.

Сигнал с четвертого вь,хода счетчикадешифратора 14 поступает также на вход (2 ° (2 — 1)+1)-го блока 29 задержки и второй управляющий вход первого анализатора 27, разрешая ему прибавлять двоичный сигнал с выхода первого сумматора 24 по модулю два со своим содержимым до поступления сигнала на его третий управляющий вход. Все остальные анализаторы 27 остактся в исходном состоянии.

При поступлении второго сигнала с логического элемента 2 1 генератор 23 псевдослучайной последовательности вырабатывает второй элемент ПСП и подает его на первый вход первого сум9 12562 матора 24 по модулю два и на вход блока 28 задержки, Блок 28 задержки, считавший первый элемент ПСП, подает его на первый вход второго сумматора 25 по модулю два и на вход ь второго блока 29 задержки, (2 (2 — 1)+

+1)-й блок 24 задержки, считавший сигнал с четвертого выхода счетчикадешифратора 14, подает его на вход .(2 ° (2" — 1)+2)-го блока 29 задержки и 10 на второй управляющий вхоц второго анализатора 27, разрешая ему прибавлять двоичный сигнал с выхода второго сумматора 25 по модулю два к своему задержанному до поступления сигнала на еro третий управляющий вход. Все остальные, кроме первого и второго анализаторов 24 и 25, остаются в исходном состоянии,, L

При поступлении 2 -го сигнала ь с логического элемента 21 (2 — 1) -й блок 29 задержки, считая на предыдущем такте первый элемент кода с (2 -2)-ro блока 29 задержки, подаL ет его на первый вход 2 -го суммато- 25 ра 25 по модулю два. (3 (2 -i)) é

4 блок 29 задержки считавший на предыЭ дущем такте сигнал с (3 (2 — 1) — 1) — го блока 29 задержки, подает его на вто4 рой управляющий вход 2 -го анализато-3д ра 27, разрешая ему прибавлять двоичный сигнал с выхода 2" -ro сумматора 25 мо модулю два к своему содержимому до поступления сигнала на его третий управляющий вход, Таким образом, все анализаторы 26 и 27 включаются в работу.

Формула изобретения

1. Устройство для передачи информации шумоподобными сигналами, содержащее на передающей стороне источник информации, генератор кодов Уолша, выход которого соединен с первым входом сумматора по модулю два, 45 выход которого соединен с первым входом балансного модулятора, генератор псевдослучайной последовательности, выход которого подключен к второму входу сумматора по модулю 50 два, а на приемной стороне — блок выбора максимума, генератор псевдослучайной последовательности, первый и второй сумматоры по модулю два, генератор опорного сигнала и смеси- 55 тель, выход которого соединен с сигнальным входом интегратора, о т л ич а ю щ е е с я тем, что, с целью

39 Ь повышения скорости передачи информации, в нем на передающей стороне введены сумматор сигналов, генератор несущего сигнала, генератор синхросигнала, дешифратор номера кода, дешифратор временной задержки, блок управления задержкой и генератор тактовых импульсов, вход которого подключен к первому выходу генератора синхросигнала, вход которого соединен с выходом генератора тактовых импульсов, с входом источника цифровой информации и с первым входом блока управления задержкой, второй вход которого подключен к выходу дешифратора временной задержки, вход которого подключен к первому выходу источника цифровой информации, второй выход которого соединен с входом дешифратора номера кода, выход соединен с первым входом генератора кодов Уолша, второй вход которого подключен к выходу блока управления задержкой и к входу генератора псевдослучайной последовательности, при этом выход генератора несущего сигнала соединен с вторым входом балансного модулятора, выход которого соединен с первым входом сумматора сигналов, второй вход которого подключен к второму выходу генератора синхросигнала, а на приемной стороне введены первый и вторые анализаторы, первый и вторые блоки задержки, счетчик-дешифратор, логический элемент, первый и второй компараторы, генератор тактовых импульсов и приемник синхросигнала, выход которого соединен с входом первого компаратора, выход которого соединен с первым входом логического элемента, второй вход которого под— ключен к выходу генератора тактовых импульсов, к первому входу второго компаратора и установочному входу интегратора, выход которого соединен с вторым входом второго компаратора, выход которого соединен с первыми входами первого и второго сумматоров

I по модулю два, выходы которых соединены с первыми входами первого и второго анализаторов, выходы которых подключены к сигналЬным входам блока выбора максимума, управляющий вход которого соединен с первым выходом счетчика-дешифратора и третьим входом логического элемента, выход которого соединен с вторыми входами первого и соответствующего второго ана1256239 лизаторов, с первыми входами первого и соответствующего второго блоков задержки, с первым входом генератора псевдослучайной последовательности и входом счетчика-дешифратора, вто- 5 рой выход которого соединен с вторым входом первого блока задержки, с третьим входом первого анализатора и вторым входом генератора псевдослучайной последовательности, третий вход которого подкпючен к третьему выходу счетчика-дешифратора, четвертому входу первого анализатора и третьему входу первого блока задержки, четвертый вход которого подключен 15 к четвертому выходу счетчика-дешифратора и пятому входу первого анализатора, выход генератора псевдослучайной последовательности соединен с вторым входом первого сумматора по 20 модулю два и пятым входом первого блока задержки, первый, второй и третий выходы которого соединены соответственно с третьим, четвертым и пятым входами соответствующего второго анализатора и соответственно вторым, третьим и четвертым входами соответствующего второго блока задержки, пятый вход которого подключен к четвертому выходу первого блока задерж- ЗО ки и второму входу соответствующего второго сумматора по модулю два, первый, второй, третий и четвертый выходы каждого предыдущего второго блока задержки соединены соответственно с вторым, третьим, четвертым и пятым входами каждого последующего второго блока задержки, соответственно с третьим, четвертым и пятым входами соответствующего второ- 4р

ro анализатора и вторым входом соответствующего второго сумматора по модулю два, выход генератора опорного сигнала подключен к первому входу смесителя, второй выход которого соединен с входом приемника синхросигнала, первый, второй, третий и четвертый выходы последнего второго блока задержки соединены соответственно с третьим, четвертым и пятым входами соответствующего второго анализатора и вторым входом соответствующего сумматора по модулю два.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что, блок управления задержкой содержит первый и второй счетчики, первый и второй дешифраторы, сумматор по модулю два с инверсией, инвертор, первый и второй элементы И и RS-триггер, установочный вход которого подключен к выходу первого элемента И, первые входы которого подключены к выходам сумматора по модулю два с инверсией, первые входы которого соединены с первыми выходами первого счетчика и первыми входами первого дешифратора, вторые входы которого подключены к выходам инвертора и вторым выходам первого счетчика, синхронизирующий вход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом RS-триггера, сбросовый вход которого соединен со сбросовым входом второго счетчика и выходом второго дешифратора, входы которого подключены к выходам второго счетчика, синхронизирующий вход которого подключен к выходу второго элемента И, выход первого дешифратора соединен с установочным входом первого счетчика, выходы инвертора подключены к вторым входам первого элемента И, при этом синхронизирующий вход первого счетчика является первым входом блока удравления задержки, вторым входом которого являются вторые входы сумматора по модулю два с инверсией, выходом блока управления задержкой является выход второго элемента И.

3. Устройство по п. i, о т л ич а ю щ е е с я тем, что логический элемент содержит последовательно соединенные RS-триггер и элемент И, выход которого является выходом логического элемента, первым, вторым и третьим входами которого являются соответственно первый вход RSтриггера, второй вход элемента И и второй вход RS — òðèããåðà.

4. Устройство по п. 1, о т л ич а ю щ е е с я тем, что генератор синхросигнала содержит компаратор, согласованный фильтр, генератор шумоподобного сигнала, дешифратор, счетчик и элемент памяти, выходы которого соединены с первыми входами счетчика, выходы которого подключены к входам пешифратора, выход которого соединен с вторым входом счетчика и входом генератора шумоподобного сигнала, выход которого через согласованный фильтр подключен к входу компаратора, выход которого является первым выходом генератора синхросиг12562 нала, вторым выходом которого является выход генератора шумоподобного сигнала.

5. Устройство по и. 1, о т л ич а ю щ е е с я тем, что счетчикдешифратор содержит первый, второй и третий дешифраторы и счетчик, выходы которого соединены с соответствующими входами первого, второго и

39 1О третьего дешифраторов, выход первого дешифратора соединен с первым входом счетчика, второй вход которого является входом счетчика-дешифратора, первым, вторым, третьим и четвертым выходами которого являются выходы соответственно первого, второго и третьего дешифраторов и первый выход счетчика.

1256239

Составитель В.Чибисов

Техред.М. Ходаиич Корректор А.Тяско

Редактор И.Дербак. Заказ 4838/59

Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва; Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4