Устройство для декодирования кодов с @ проверками на четность

Иллюстрации

Показать всеРеферат

Изобретение относится к юблаС- ти вычислительной техники и касается техники передачи и хранения вычислительной информации. Целью изобретения является повышеиие достоверности контроля. Устройство содержит логические блоки, в состав которых ; входят сумматоры по модулю два обнаружения ошибок в группах и дешифраторы , сумматоры по. модулю два группы символов кодов, кроме того, устройство содержит блок исправления ощибок. Поставленная.цель достигается тем, что число логических блоков равно двум, а число сумматоров по модулю два символов кодов равно в первом логическом блоке 2 - 1, 2 1« К К, + К, +. а во втором 1, где « -iv I- I. При этом в каждый логический блок введеи дополнительный сумматор по модулю два группы символов кодов, в устройство введены узел блокировки и два узла суммирования по модулю два. I з.п. ф-лы, I ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

aO4.G 06 F ll 10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЬЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРОЮ (21) 3474922/24-24 .(22) 21.07,80 (46) !5.09.86.Бюл. У 34 (72) А.В.Пастухов и А.П.Смирнов (53) 681.3 (088.8) (56) Патент США У 3573728, кл. 340-146.1, опублик. 1970.

Авторское свидетельство СССР

У 451084, кл. Н 04 L l/10, Q 06 Р !1/08, 1972 . (54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЧ

КОДОВ С К IIPOBEPKAMH НА ЧЕТНОСТЬ (52) Изобретение относится к области вычислительной техники и касается техники передачи н хранения вычислительной информации. Целью изоб" ретения является повышение достоверности контроля. Устройство содержит

„„SU„„1257648 А 1 логические блоки, в состав которых входят сумматоры по модулю два обнаружения ошибок s группах и дешифраторы, сумматоры по модулю два группы символов кодов, кроме того, устройство содержит блок исправления ошибок. Поставленная цель достигается тем, что число логических блоков . равно двум, а число сумматоров по модулю два группы символов кодов равно в первом логическом блоке 2 - 1, К1 авовтором2"-1, где К К + К +

kL

+ 1. При этом в каждый логический блок введен дополнительный сумматор по модулю два группы с имволов кодов, Is устройство введены узел блокировки Е и два узла сумьырования по модулю два. l s.n. ф-лы, ил.

1257648 2

Изобретение относится к вычислительной технике и касается техники передачи и хранения вычислительной информации.

ЦелЬю изобретения является повышение достоверности контроля.

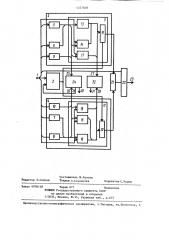

На чертеже приведена схема устройства.

Устройство содержит вход l устройства, узел 2 блокировки, логические блоки 3 и 4 группы, сумматоры 5-8 по модулю два группьг символов кодов, дополнительные сумматоры

9 и 10 по модулю два группы символов кодов, узлы обнаружения ошибок в группах ll 12, сумматоры l 3-16 по модулю два обнаружения ошибок в группах, дополнительные сумматоры

17 и. 18 по модулю два обнаружения ошибок в группах, дешифраторы 19,20 обнаружения ошибок.в группах, дешифратор 21, блок 22 исправления ошибок, выход 23 устройства, второй узел 24 суммирования по модулю два, входы 25 и 26 узла 24, входы 27 и 28, выходы 29-31, первьпr узел 32 суммирования по модулю два.

Устройство работает следующим образом.

На вход 1 поступают параллельно информационные и контрольные символы кода.

Случай А. Отсутствуют ошибки входной информации и.иет отказов оборудования устройства.

Сигналы,.формируемые на выходах сумматоров 13-16, дают нулевые значения проверок — на выходах 30 и 31 сформируются нулевые значения. На выходе дешифратора 21 присутствует сигнал, свидетельствующий об отсутствии ошибок информационных символов, которые без искажений будут переданы на вход устройства.

Слу ай Б. Наличие ошибок во входной информации, отсутствие отказов оборудования устройства.

При ошибочном информационном символе {кроме x ) на выходах сумматоров 13-16 значения проверок отличны от нуля, при этом на выходах

30, 31 и.выходе узла 2 равны соответственно 0,0 и 1.,Поэтому на одном из выходов дешифратора 20 появится сигнал, соответствукнций номеру ошибочного байта, а на одном из выходов дешифратора 19 — сигнал, соответствуюгций номеру ошибочного символа в байте. На выходе дешифратора 21 появится сигнал, однозначно соответствующий номеру ошибочного информационного символа в коде.

S При поступлении этого сигнала на вход блока 22 он инвертирует значение информационного символа с ошибочного на правильное.

При ошибочном контрольном или информационном символе х на выходах

30 и 31 будут значения соответственно 0,0 и узел 2 сформирует значение

О, который заблокирует формирование сигналов ошибок дешифраторами 19 и 20. При этом формирование сигналов номера ошибочного символа, если это требуется, осуществляется не двумя последовательно соединенными дешифраторами 19(20), 2! а одним односту20 пенчатым дешифратором /на чертеже не показан/.

Случай В. Отсутствие ошибок во входной информации и наличие отказов оборудования устройства.

При отказах основной части оборудования (сумматоров 7,8, 10,13-18, узлов 24 и 32) на выходе узла 2 сигнал равен О, сигналы на выходах 30 и 31 также равны 1,1. В результате

30 .обеспечивается правильная выдача сим.волов на выход 23 и локализация отказов оборудования по соответствующим ненулевым сигналам выходов 30 и 31.

Случай Г. Наличие многократных (двойных) ошибок во входной информации или одиночньгх ошибок и отказов оборудования устройства.

Этот случай является не основным и характеризуется возникновением от40 носихельно маловероятных неисправностей. Его реализация, обеспечивающая останов по ошибке., не приведена на.чертеже, является достаточно простой и выполняется с использованием

45 сигналов проверок.

Таким образом, данное устройство позволяет повысить достоверность контроля.

Формула из о б ре т ения

1, Устройство для декодирования кодов с К.проверками на четиость, содержащее группу логических блоков, каждый из которых содержит сумматоры по модулю два группы символов кодов, выходы которых соединены с соответствующими входага узла обнаруже48

2. Усгройство по п.1, о т л и ч а ю щ е е с я тем, что, узел о6aapymemm ошибок в группах содержит дешифратор ошибок.в группах, сумматоры по модулю два обнаружения ошибок в группах, дополнительный сумматор по модулю два обнаружения ошибок в 1pyrmax, входы которых являются соответствующими входами узла, выходы соединены с входами дешифратора ошибок в группах и являются выходами значений проверок узла, блокирую-. щий вход и выход дешифратора ошибок в группах являются соответственно блокирующим входом и выходом узла. з,12576 ния ошибок в группах, а.также содержащее дешифратор, входы которого соединены с выходами узлов обнаружения ошибок в группах логических блоков группы, а выход соединен с первым входом блока исправления ошибок, выход которого является выходом устройства, а второй вход соединен с информационным входои устройства, входы сумматоров по модулю два группы сим- 10 волов кодов логических блоков группы соединены с соответствунщнми информа" ционными входами устройства, о т л ич а ю щ .e e с я теи, что, с целью повывЬния достоверности контроля, в 15 устройство введены узел блокировки и два узла суммирования tro модулю.два, а число логических блоков s группе равно двум, число суиматоров по модулю два группы символов кодов равно 20 ,в первом логическом блоке 2 - 1

К

Ф а. so втором 2 - 1 (где К K - + K +

+ 1), причем в каждый логический. .блок введен дополнительньй сумматор по модулю два группы символов кодов, 25 вход и выход которого соединены соответственно с соответствующим входом устройства и соответствующим входои второго узла суммирования по модулю два, кроме то- ЗО

ro, первая и вторая группы вколов первого узла суммирования по-модулю два соединены соответственно с выходами всех сумматоров по модулю два группы символов кодов логических блоков группы, а первый выход соединен с управляющим входом узла блокировки, информационньп1 вход которого соединен с входом устройства, первая и вторая группы входов второго узла суммирования по модулю два соединены соответственно с выходами значений проверок узлов обнаружения ошибок в группах, а выход второго и второй выход первого узла суммирования по модулю два являются выходами локализации отказов устройства, выход узла блокировки соединен с блокирующими входами узлов обнаружения ошибок в группах.

257648

Составитель И.Хазова

Техред Л.Сердюкова

Редактор Э.Слигон

Корректор С.Черни

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

3 l3035, Москва, N-35, Раушская наб., д.4/5. Заказ 4958/48

Производственно-.полиграфическое предприятие, г.ужгород, ул.Проектная, 4