Устройство для контроля двух импульсных последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники и может быть использовано в ЭВМ и цифровых системах с повышенной дос- . товерностью. Отличительной особенностью устройства является то, что оно может использоваться для контроля пар последовательностей нмпульсов, для которых заранее неизвестно, на какой из входов импульс поступит первым, либо в тех случаях, когда требуется Подключение устройства для контроля в произвольный, заранее неизвестный момент времени. Это существенно расширяет область применения устройства. Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей с различной очередностью поступления. Поставленная цель достигается введением третьего и четвертого злементов И, 3 ил. (Л с: ю ел SI О 4 ;о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Д!! 4 С 06 F 11/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTMPbITPM (2l) 3779308/24-24 (22) 13.08.84 (46) 15.09.86.Бюл. У 34 (71) Научйо-исследовательский институт автоматизации управления и про.изводства (72) А.И.Павлов, С.В.Суярко, Г.Н.Тимонькин, С.Н.Ткаченко и В.С.Харченко (53) 681 ° 3 (088 ° 8) (56) Авторское свидетельство СССР

У 1045373, кл. Н 03 К 5/19, 1982.

Авторское свидетельство СССР

Ф !223232, кл г 06 F ll/16, 1985

{54) УСТРОЙСТВО ДПЯ КОНТРОЛЯ ДВУХ

ИИПУЛЬСННХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение относится к области цифровой вычислительной техники и может быть использовано в ЭВМ и, Я0„„1257649 А1 цифровых системах с повышенной дос" товерностью. Отличительной особенностью устройства. является то, что оно может использоваться для контроля пар последовательностей импульсов, для которых заранее неизвестно, на какой из входов импульс поступит первым, Либо в тех случаях, когда требуется подключение устройства для контроля в произвольный, заранее неизвестный момент времени. Это существенно расширяет область применения устройства. Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей с различной очередностью поступления. Поставленная цель достигается введением третьего и четвертого элементов И. 3 ил.

1257649

Изобретение относится к цифровой вычислительной технике и может быть использовано в 3ВМ и цифровых системах с повышенной достоверностью.

Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей с различной очередностью поступления.

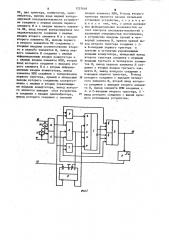

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 и

3 — временные диаграммы его работы для случаев неперекрывающихся и частично перекрывающихся последовательностей импульсов.

Устройство содержит первый I u второй 2 триггеры, коммутатор 3 элементы И 4-7, элемент ИЛИ 8, одновибратор 9, входы 10 и 11 первой и второй контролируемых последовательностей устройства, вход 12 начальной установки устройства„ выход 13 сбоя устройства, элементы И-НЕ 14 и 15.

Триггер 1 предназначен для запоминания, по какому из входов устройства пришел последний импульс, и управления в соответствии с этим коммутатором 3. Он представляет собой синхронный JK-триггер, переключение которого происходит в противоположное состояние по заднему фронту импульса на входе С, если

J.=К=1, Входы R u S триггера предназначены для его начальной установки и являются асинхронными, Триггер 2 предназначен для управления начальной установкой триггера при запуске устройства. Он также запрещает работу коммутатора 3 до правильной начальной установки триггера 1. Триггер 2 представляет собой счетный. триггер, переключение которого в единичное состояние происходит по заднему фронту импульса, поступившего на объединение J и С входы. Вход К вЂ” асинхронный, служит для начальной установки триггера 2 в нулевое состояние.

Коммутатор 3 формирует сигналы ошибки на выходе !3 сбоя устройства, если нарушается последовательность поступления импульсов на входы

10 и 11 устройства. Он включается в работу только при единичном состоянии триггера 2.

Элементы И 4, 5 совместно с элементами НЕ 14, 15 предназначены для обеспечения работоспособности устрой40

50!

О

l$

35 ства, если на его входы 10 и 11 поступают частично перекрывающиеся во времени последовательности импульсов. В этом случае на выход элемента И 4 проходит только часть импульса, поступившего на вход 10 устройства и не перекрывающегося с импульсом, поступившим на вход 11 (см.фиг.3). Аналогично на выход элемента И 5 проходит только часть импульса, поступившего на вход 11 и не перекрывающегося с импульсом на входе 10 устройства (см.фиг.3).

Элементы И 6,7 предназначены для формирования сигналов начальной установки триггера 1, Элемент И 6 формирует сигнал на S-вход триггера 1, если триггер 2 находится в исходном состоянии и первым поступил импульс на вход 10 устройства. Элемент И 7 формирует сигнал на К-вход триггера

1, если триггер 2 находится в исход ном состоянии и первым поступил импульс на вход 11 устройства.

Элемент ИЛИ. 8 предназначен для формирования сигналов переключения триггера 1 в процессе работы устройства.

Одновибратор 9 служит для формирования импульса, переключающего триггер 1 в противоположное состояние, если в результате ошибки в одной из входных последовательностей устройство сформировало на выходе

13 сигнал ошибки, а триггер в результате пропадания одного из входных импульсов оказался в состоянии, противоположном требуемому. Одновибратор 9 формирует импульсы по заднему фронту импульса, поступившего на выход 13 устройства. Длительность импульса, формируемого одновибратором 9, выбирается минимальной длины, обеспечивающей надежное срабатывание триггера 1.

Устройство работает следующим образом.

Перед началом работы на вход 12 начальной установки устройства подается сигнал начальной установки, по которому триггер 2 устанавливается в нулевое состояние, Состояние триггера 1 произвольное.

Импульс контролируемых последовательностей, поступивший первым на входы 10 и 11 устройства, производит начальную установку триггера 1 и за1257649 пуск устройства в работу — установку триггера 2 в единичное состояние.

Пусть первым поступает импульс на вход 10 устройства (см.фиг.2).

Этот импульс проходит через открытые 5 элементы И 4 и 6 на вход S триггера

1 и устанавливает его в единичное состояние. Одновременно этот импульс проходит через элемент ИЛИ 8 на синхровход триггера 1 и объединенные

3- и С-входы триггера 2. По заднему фронту этого импульса триггер 2 переключается в единичное состояние и своими выходными сигналами закрывает элементы И 6, 7, разрешает работу триггера 1 по счетному входу (подав единичный сигнал на входы J и К триггера 1) и открывает коммутатор 3. Переключения триггера 1 по заднему фронту этого импульса не происходит, так как в момент окончания импульса на входах J и К триггера 1 присутствует нулевой сигнал. После установ.ки триггера в единичное состояние устройство готово к контролю входных 25 последовательностей.

При правильном формировании входных последовательностей следующим поступает импульс на вход ll устройства. Через элементы И 5 и ИЛИ 8 он 30 проходит на входы триггера 1 и коммутатора 3. На выход коммутатора 3 не поступает, так как последний закрыт нулевым сигналом с инверсного .выхода триггера 1, а по его заднему З5 фронту триггер 1 переключается в противоположное, т.е ° нулевое сос- тояние.

Следующим поступает импульс на вход 10 устройства. Через элементы

И 4 и ИЛИ 8 он проходит на синхровход триггера 1, и по его заднему фронту триггер 1 переключается в противоположное (единичное) состояние, На выход коммутатора 3 он так- 45 же не проходит, так как последний закрыт нулевым сигналом с единично-. го выхода триггера 1.

При отсутствии искажений во входных последовательностях устройство 50 работает аналогично описанному выше.

При пропадании импульса в одной из входных последовательностей,например импульса на входе ll устройст- 55 ва (см.фиг.2), на вход триггера 1 последовательно поступают два импульса с входа 10 устройства. Первый из них устанавливает триггер 1 в единичное состояние, а второй проходит через коммутатор 3, открытый сигналом с единичного выхода триггера на выход 13 сбоя устройства, сигнализируя об искажении контролируемых последовательностей импульсов. Своим задним фронтом этот импульс переключает триггер 1 в нулевое состояние. После этого по заднему фронту импульса на выходе 13 сбоя устройства одновибратор 9 формирует импульс, который проходит через элемент ИЛИ 8 и вновь переключает триггер 1 в единичное состояние. Если в последующем искажений контролируемых последовательностей не происходит, то устройство функционирует аналогично описанному выше, не выдавая сигналов ошибки.

Если происходит пропуск импульса в последовательности, поступающей на вход 10 устройства, то на вход lt последовательно поступают два импульса (см.фиг.2). Первый из них своим задним фронтом устанавливает триггер 1 в нулевое состояние, а второй проходит через открытый коммутатор

3 на выход 13 устройства, сигнализируя о пропуске импульса. Триггер 1 вновь переключается в единичное состояние. По заднему фронту импульса на выходе 13 одновибратор 9 формирует импульс, который возвращает триггер 1 в нулевое состояние и тем самым подготавливает устройство к слее дующему такту работы.

Если на выходы 10 и 11 устройства поступают частично перекрывающиеся во времени последовательности импульсов (см.фиг.3), то на выходах элементов И 4 и 5 появляются только те части импульсов, которые не совпа дают по времени с импульсами на про-: тивоположном входе, Следовательно, благодаря наличию на входах устройства элементов И 4 и 5 задача контроля частично перекрывающихся во вре- . мени входных последовательностей импульсов решается так же, как и задача контроля неперекрывающихся входных последовательностей.

Формула изобретения

Устройство для контроля двух им- ,пульсных последовательностей, содерI жащее два элемента И, два элемента

1257649

НЕ, два триггера, коимутатор, одновибратор, причем вход первой контролируемой последовательности устройства соединен с первым входом первого элемента И и с входом первого элемен та НЕ, вход второй контролируемой пос. ледовательности соединен с первым входом второго элемента И и с входои второго элемента НЕ, выходы первого и второго элементов НЕ соединены с 10 вторыии входами соответственно второго и IIepBofo элементов И, выход первого элемента И соединен с первым информационныи входом коммутатора и

С первцм входом элемента ИЛИ, второй 1$ вход которого соединен с выходом второго элемента И и с вторым информа- ционным входом коммутатора, выход элемента ИЛИ соедИнен с синхровходом первого триггера, прямой и инверсный 20 выходы которого соединены соответственно с первым и вторым управляющими входами коммутатора, выход которого является выходом сбоя устройства и соединен с входом одновнбратора,, выход которого соединен с третьим

6 входом элемента KIH R âõîä второго триггера является входом начальной установки устройства, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей за счет контроля последовательностей с различной очередностью поступления, в устройство введены третий и четвертый элементы И, причем прямой выход второго триггера соединен с Jи К-входами первого триггера и . третьим н четвертым управляющими входами коммутатора, инверсный выход. второго триггера соединен с первыми входами третьего и четвертого элементов И, выход первого элемента И соединен с вторым входом третьего элемента И, выход которого соединен с

5-входом первого триггера, R-вход которого соединен с выходом четвертого элемента И, второй вход которо- го соединен с выходом второго элемента И, выход элемента ИЛИ соединен с

3- и С-входами второго триггера, К— вход которого соединен с шиной нулевого потенциала устройства.

1257649

Составитель Е.Торопов

Техред Л. Сердюкова

Корректор С Черни

Редактор И.Рыбченко

Тирах 673 Подписное

ВНИИПИ Государственного комитета СССР . по делам изобретений и открмтий

113035. Москва, W-35, Рауаская наб., д.М5, Заказ 4958/48

Производственно-полиграфическое предприятие, г.ухгород, ул.Проектная, 4