Синтезатор частоты

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ сОциАлистичеснИх

РЕСПУБЛИН (50 4 Н 03 1. 7/18 госудч ственный комитет сссР пО делАм изОБРетений и ОтнРытий

ОПИСАНИЕ ИЗОБРЕТЕНИН 1. "

H А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ кн, формирователя управляющих сигналов, к выходу сигнала отключения управления выходной частотой которого подсоединен второй вход первого ключа, отличающийся тем, что, с целью повышения стабильности частоты выходного сигнала, выход делителя частоты соединен с входом сигнала отключения начальной установки формирователя управляющих сигналов, а вторые управляющие входы частотно-ф;:зового детектора и делителя частQTbl с переменным коэффициентом деления объединены и подключены к второму выходу сигнала начальной установки формирователя управляющих сигналов.

2, Синтезатор по н. 1, о т л ич а ю шийся тем, что формирователь управляющих сигналов содержит последовательно-соединенные генератор тактовых импульсов, элемент KIN-НЕ, элемент ИЛИ и первый D-триггер, последовательно соединенные формирователь импульсов и RS-триггер, а также второй Э-триггер, инверсный вход которого подключен к С-входу первого

D-триггера, вторые входы элемента

ИЛИ-НЕ, элемента ИЛИ и S-вход второго Р-триггера объединены и являются входом сигнала задержки включения формирователя. управляющих сигналов, R-вход RS-триггера объединен с С-входом второго D-триггера и является входом сигнала отключения начальной установки формирователя управляющих сигналов, D-вход второго D-триггера объединен с входом формирователя импульсов н подключен к выходу элемента ИЛИ-НЕ, при этом прямой выход пер,(21) 3769957/24-09 (22) 05,07.84 (46) 15.09.86. Бюл. У 34 (71) Московский ордена Трудового

Красного Знамени электротехнический институт связи (72) А.В.Пестряков и А.Л.Козлов (53) 621.373.42(088.8) (56) 11атеит франции Ф 21 48920, кл. Н 03 К 1/00, 23,03.73.

Авторское свидетельство СССР

У 1007202, кл. Н 03 I, 7/18,23,03,83, (54)(57) 1. СИНТЕЗАТОР ЧАСТОТЫ, содержащий последовательно соединенные опорный генератор, делитель частоты, частотно-фазовый детектор, первый ключ, фильтр нижних частот, перестраиваемый генератор и делитель частоты с переменным коэффициентом деления, выход которого подключен к второму входу частотно-фазового детектора, датчик синхронизма, вход и выход которого соединены соответственно с выходом частотно-фазового детектора и с входом сигнала задержки включения формирователя управляющих сигналов, и второй ключ, первый и второй входы которого подключены соответственно к шине питания и к выходу сигнала управления напряжением питания, формирователя управляющих сигналов, первые управляющие входы частотно-фазового детектора, делителя частоты и делителя частоты с переменным коэффициентом деления объединены и подключены к выходу второго ключа, второй управляющий вход делителя частоты подключен к первому выходу сигнала начальной установ„„ВИ„,Л 257845 А1 выходом сигнала начальной установки, вторым выходом сигнала начальной установки и выходом сигнала отключения начальной установки формирователя управляющих сигналов, 1257845 вого D-триггера, выход формирователя импульсов, прямой выход RS-триггера и выход второго D-триггера являются соответственно выходом сигнала управления напряжением питания, первым

Изобретение относится к радиотехнике и может быть использована в приемо-передающей аппаратуре систем радиосвязи.

Цель изобретения — повышение ста- 5 бильности частоты выходного сигнала.

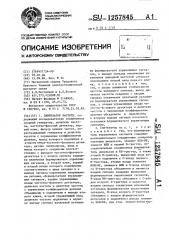

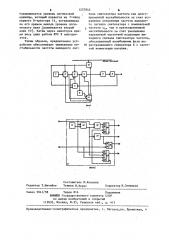

На фиг. 1 представлена электрическая структурная схема синтезатора частоты, на фиг, 2 — схема формирователя управляющих сигналов.

Синтезатор частоты содержит опорный генератор l делитель частоты 2, частотно-фазовый детектор (ЧФД) 3, первый ключ 4, фильтр 5 нижних частот (ФНЧ), перестраиваемый генератор 6, делитель 7 частоты с переменным коэффициентом деления (ДПКД), датчик синхронизма 8, формирователь 9 управляющих сигналов (ФУС), второй ключ 10. При этом формирователь 9 уп- 20 равляющих сигналов содержит генератор 11 тактовых импульсов, элемент

ИЛИ-НЕ 12, элемент ИЛИ 13, первый .D-триггер 14, формирователь 15 импульсов, RS-триггер 16, второй Dтриггер 17, Синтезатор частоты работает следующим образом, В отсутствии установившегося режима на выходе датчика синхрониэма

8 появляется сигнал, блокирующий работу ФУС 9. При этом с выхода сигнала управления напряжением питания и с выхода сигнала отключения управления выходной частотой ФУС 9 на 35 управляющие входы первого 4 и второго 10 ключей поступают сигналы, под действием которых эти ключи замыкаются и работает кольцо.фазовой автоподстройки. 40

В установившемся режиме с выхода датчика синхронизма 8 на вход сиг-. нала задержки включения ФУС 9 поступает сигнал разблокировки,и ФУС 9

2 формирует на своих выходах периодические сигналы. В установившемся режиме в определенный момент времени на выходе сигнала управления напряжением питания ФУС 9 появляется сиг нал, под действием которого. второй ключ 10 замыкается, и напряжение питания подается на делитель частоты

2, ЧФД 3, ДПКД 7, с первого и второго выходов сигналов начальной установки ФУС 9 подаются сигналы на установку в исходное состояние делителя частоты 2, ЧФД 3, ДПКД 7. Длительность сигнала установки в исходное состояние делителя частоты 2 равна интервалу времени, достаточного для завершения переходных процессов, связанных с включением питания и установкой цифровых элементов в исходное состояние. После исчезновения первого сигнала начальной установки делитель частоты 2 начинает полный цикл счета., С появлением первого импульса на выходе делителя частоты 2 снимается второй сигнал начальной установки в исходное состояние ЧФД 3, ДГКД 7, замыкается первый ключ 4. В результате этого делитель частоты 2 и ДПКД 7 одновременно начинают полный цикл счета, т.е. осуществляется привязка начала счета делителя частоты 2 и ДПКД

7 к фазе колебания опорного генератора 1, соответствующей моменту срабатывания делителя частоты 2. В результате исчезает начальная разность фаз сигналов, поступающих на

ЧФД 38 - =-„, так как Ь, =О, а следовательно, уменьшается нестабильность частоты выходного сигнала синтезатора частоты в установившемся режиме.

Через некоторое время, определенное скважностью сигнала генера30

3 12578 тора тактовых импульсов ll и момен- 1 том появления импульса на выходе делителя частоты 2, размыкается первый ключ 4, разрывая тем самым цепь кольца фазовой автоподстройки, затем размыкается второй ключ 10, он снимает напряжение питания с делителя частоты 2, ЧФД 3, ДПКД 7. Потребление энергии питания синтезатором в этом состоянии сокращается. На- 10 пряжение, запомненное на емкости

ФНЧ 5, поддерживает частоту подстраиваемого генератора 6, соответствующую частоте, достигнутой системой фазовой автоподстройки до момента ее отключения.

Затем, через некоторое время, напряжение от источника питания подается на все узлы синтезатора частоты, кольцо фазовой автоподстрой- 20 ки замыкается, и весь цикл работы повторяется.

В отсутствии установившегося режима на входе сигнала задержки включение ФУС 9 присутствует положитель- » ный потенциал, который подается на входы элементов ИЛИ-НЕ 12 и ИЛИ 13, а также. на S-вход второго D-триггера 17. С выхода элемента ИЛИ 13 положительный потенциал подается на

S-вход первого D-триггера 14, а с выхода элемента ИЛИ-НЕ 12 нулевой потенциал подаетея на вход формирователя импульсов 15 и D-вход второго D-триггера 17.

На $-вход RS-триггера 16 с выхода формирователя 15 импульсов поступает сигнал с нулевым логическим уровнем, а на ll -вход RS -òðèããåðà 16 №О подаются импульсы с выхода делителя частоты 2, т.е. в отсутствии установившегося режима на выходе сигнала управления напряжением питание и на выходе сигнала отключения уп" равления выходной частотой ФУС 9

45 присутствует сигнал с уровнем логической единицы, первый и второй ключи 4 и 10 замкнуты, а на первом и втором выходах сигнала начальной установки ФУС 9 присутствует сигнал

50 с уровнем логического нуля.

В установившемся режиме на выходе датчика синхронизма 8 нулевой потенциал и ФУС 9 формирует на esoux выходах управляющие сигналы с пернс дом, определяемым генератором 11 тактовых импульсов.

Рассмотрим работу ФУС 9 на приме. ре одного периода выходных импульсов генератора 11 тактовых импульсов °

Появившийся на выходе элемента

ИЛИ-HE 12 импульс с положительным потенциалом устанавливает на прямом выходе первого D-триггера 14 уровень, соответствующий логической единице (замыкается второй ключ 10).

Одновременно из выходного импульса элемента ИЛИ-НЕ 12 на выходе формирователя импульсов 15, формируется импульс необходимой длительности (импульс установки в начальное сос" тояние счетчиков делителя частоты

2), который также подается на S-вход

RS-триггера 16, устанавливая на прямом выходе RS-триггера 16 уровень логической единицы (импульс установки в начальное состояние ЧФД 3, ДПКД 7). После исчезновения импульса на выходе формирователя 15 импульсов делитель частоты 2 начинает полный цикл счета, и первый появившийся импульс на входе сигнала отключения начальной установки ФУС

9 устанавливает на прямом выходе второго D-триггера 17 и четвертом выходе ФУС 9 уровень, соответствующий логической единице {замыкается первый ключ 4), одновременно импульс с выхода делителя частоты 2 поступает на R-вход RS-триггера 16, устанавливая на прямом выходе КЯтриггера 16 уровень, соответствующий логическому нулю 1снимается импульс установки в исходное состояние ЧФД 3, ДПКД 7),и ДПКД 7 одновременно с делителем частоты 2 начина-. ет полный цикл счета, т.е. осуществляется привязка начала счета делителя частоты 2 и ДПКД 7 к фазе опорного генератора 1, соответству«"щей моменту срабатывания делителя частоты 2. Исчезает начальная разность фаз 3р так как а, =О.

С исчезновением положительного потенциала на выходе элемента ИЛИНЕ 12, а следовательно, и íà S-входе., ! первого 9-триггера 14 и D-входе вто- рого П-триггера 17, первый появившийся импульс на входе сигнала отключения начальной установки ФУС 9 устанавливает уровень логического куля на прямом выходе второго1 триггера 17 (размыкается первый ключ

4), на инверсном выходе которого усСоставитель N. Ковалев

Техред И.Верес Корректор В.Синицкая

Редактор Т,Митейко

Заказ 5041/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород,ул, Проектная, 4

Ф 1257845 танавливается уровень ло ической . нала синтезатора частоты как долгоединиЦы, который подается на С-вход временной нестабильности за счет устпервого Э-триггера 14, устанавливая ранения отклонения частоты выходнона его прямом выходе уровень логи- го сигнала синтезатора с номинальной ческого нуля (размыкается второй частоты а„ так и кратковременной ключ 10). Чатем через некоторое вре- нестабильности за счет уменьшения мя весь цикл работы ФУС 9 повторя- паразитной частотной модуляции выется. ходного сигнала синтезатора частоты,, Таким образом, предлагаемое уст- обусловленной колебаниями фазы перойство обеспечивает уменьшение не- !О рестраиваемого генератора 6 с частостабильности частоты выходного сиг- той коммутации питания,